# System-level design for efficient execution of CNNs at the edge

Minakova, S.

#### Citation

Minakova, S. (2022, November 24). System-level design for efficient execution of CNNs at the edge. Retrieved from https://hdl.handle.net/1887/3487044

Version: Publisher's Version

License: License agreement concerning inclusion of doctoral thesis in the Institutional Repository of the University of Leiden

Downloaded from: <a href="https://hdl.handle.net/1887/3487044">https://hdl.handle.net/1887/3487044</a>

**Note:** To cite this publication please use the final published version (if applicable).

# System-level Design For Efficient Execution of CNNs at the Edge

Svetlana Minakova

| This work has received funding from the European Unions Horizon 2020 Research and Innovation project under grant agreement No. 780788.                                                                                             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| System-level Design For Efficient Execution of CNNs at the Edge. Svetlana Minakova Dissertation Universiteit Leiden.                                                                                                               |

| Copyright © 2022 by Svetlana Minakova. This dissertation was typeset using LATEX. Cover design: from images generated using DALL·E mini Deep Learning algorithm [20]. The images are combined and post-processed by Anna Minakova. |

|                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                    |

# System-level Design For Efficient Execution of CNNs at the Edge

#### **Proefschrift**

ter verkrijging van de graad van doctor aan de Universiteit Leiden, op gezag van rector magnificus prof.dr.ir. H. Bijl, volgens besluit van het college voor promoties te verdedigen op donderdag 24 november 2022 klokke 11.15 uur

door

Svetlana Minakova geboren te Ryazan, Rusland in 1993

#### **Promotores:**

Dr. T.P. Stefanov

Prof.dr. H.A.G. Wijshoff

### **Promotiecommissie:**

Prof.dr. S. Ha (Seoul National University)

Prof.dr. J. Castrillon (Technical University of Dresden)

Prof.dr. H.E. Bal (Vrije Universiteit Amsterdam)

Prof.dr. A. Plaat

Prof.dr. N. Mentens

Prof.dr. M.S.K. Lew

### **Contents**

| Ta | ıble o | f Cont  | ents                                                     | vii  |

|----|--------|---------|----------------------------------------------------------|------|

| Li | st of  | Figures | 3                                                        | xi   |

| Li | st of  | Tables  |                                                          | xiii |

| Li | st of  | Abbrev  | viations                                                 | xv   |

| 1  | Intr   | oductio | on                                                       | 1    |

|    | 1.1    | Accui   | racy and platform-aware characteristics of a CNN         | 3    |

|    | 1.2    |         | rements posed on a CNN executed at the Edge              | 4    |

|    | 1.3    | _       | ent trends in the design of CNNs executed at the Edge    | 4    |

|    | 1.4    |         | ations of the state-of-the-art design flow for CNNs exe- |      |

|    |        |         | at the Edge                                              | 7    |

|    |        |         | Limitation 1                                             | 7    |

|    |        | 1.4.2   | Limitation 2                                             | 8    |

|    | 1.5    | Resea   | rch contributions                                        | 9    |

|    |        | 1.5.1   | RC1: Methodology for high-throughput CNN inference       | 12   |

|    |        | 1.5.2   | 67 6 6 1                                                 | 13   |

|    |        | 1.5.3   | Methodology for run-time adaptive inference of CNN-      |      |

|    |        |         | based applications                                       | 13   |

|    |        | 1.5.4   | Methodology for joint memory optimization of multiple    |      |

|    |        |         | CNNs                                                     | 14   |

|    | 1.6    | Thesis  | s organization                                           | 15   |

| 2  | Bac    | kgroun  | ıd                                                       | 17   |

|    | 2.1    | CNN     | model                                                    | 18   |

|    |        | 2.1.1   | Layer in the CNN model                                   | 18   |

|    |        | 2.1.2   | Edge in the CNN model                                    | 22   |

|    | 2.2    | CNN     | deployment and inference at the Edge                     | 22   |

viii Contents

|   | 2.3  | 0 1                                                            | 24                       |

|---|------|----------------------------------------------------------------|--------------------------|

|   | 2.4  | 1                                                              | 25                       |

|   | 2.5  | 1                                                              | 28                       |

|   | 2.6  | Genetic Algorithm (GA)                                         | 30                       |

| 3 |      | 07 0 0 1                                                       | 33                       |

|   | 3.1  |                                                                | 34                       |

|   | 3.2  |                                                                | 35                       |

|   | 3.3  |                                                                | 36                       |

|   | 3.4  | 0 1                                                            | 37                       |

|   | 3.5  | 0)                                                             | 38                       |

|   |      |                                                                | 41                       |

|   |      | 11 0                                                           | 42                       |

|   |      |                                                                | 44                       |

|   | 3.6  | Experimental results                                           | 47                       |

|   | 3.7  | Conclusion                                                     | 49                       |

| 4 | Met  | hodology for low-memory CNN inference                          | 51                       |

|   | 4.1  | •                                                              | 51                       |

|   | 4.2  |                                                                | 52                       |

|   | 4.3  |                                                                | 54                       |

|   | 4.4  |                                                                | 55                       |

|   | 4.5  | <u> -</u>                                                      | 60                       |

|   |      |                                                                | 61                       |

|   |      |                                                                | 62                       |

|   | 4.6  |                                                                | 66                       |

|   | 4.7  |                                                                | 69                       |

| 5 | Mot  | hodology for run-time adaptive inference of CNN-based applica- |                          |

| 3 | tion | -                                                              | 71                       |

|   | 5.1  |                                                                | 71<br>71                 |

|   | 5.2  |                                                                | , <sub>1</sub><br>72     |

|   | 5.3  |                                                                | 73                       |

|   | 5.4  |                                                                | 73<br>74                 |

|   | 5.5  | <del>-</del>                                                   | 78                       |

|   | 5.6  |                                                                | 70<br>79                 |

|   | 5.7  |                                                                | 7 )<br>81                |

|   | 0.7  |                                                                | 81<br>82                 |

|   |      |                                                                | 85                       |

|   |      |                                                                | 85                       |

|   |      | on of the control edges                                        | $\mathcal{O}\mathcal{O}$ |

Contents ix

|    |       | 5.7.4 Deployment and inference                               | 86  |

|----|-------|--------------------------------------------------------------|-----|

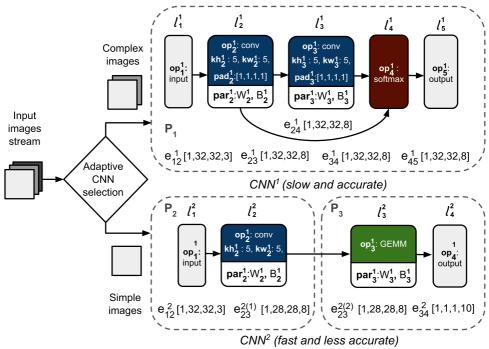

|    | 5.8   | SBRS MoC automated derivation                                | 86  |

|    | 5.9   | Transition protocol                                          | 89  |

|    | 5.10  | Experimental Study                                           | 94  |

|    |       | 5.10.1 Automated scenarios derivation                        | 95  |

|    |       | 5.10.2 SBRS MoC memory reuse efficiency                      | 99  |

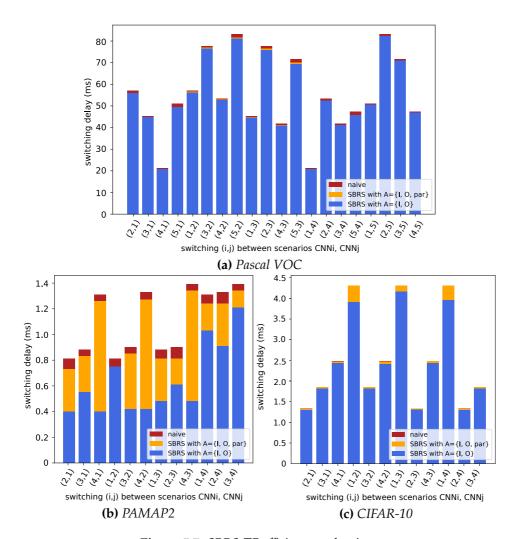

|    |       | 5.10.3 SBRS-TP efficiency                                    | 101 |

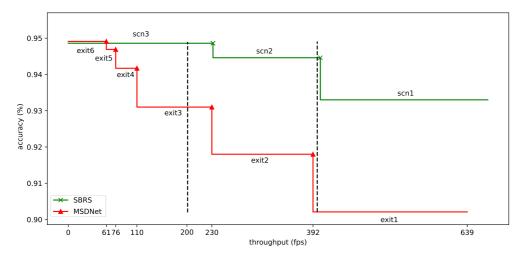

|    |       | 5.10.4 Comparative study                                     | 103 |

|    | 5.11  | Conclusion                                                   | 105 |

| 6  | Met   | hodology for joint memory optimization of multiple CNNs      | 107 |

|    | 6.1   | Problem statement                                            | 107 |

|    | 6.2   | Contributions                                                | 108 |

|    | 6.3   | Related Work                                                 | 109 |

|    | 6.4   | CNN-based application                                        | 111 |

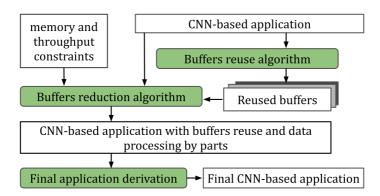

|    | 6.5   | Methodology                                                  | 113 |

|    |       | 6.5.1 Buffers Reuse Algorithm                                | 115 |

|    |       | 6.5.2 Buffers Reduction Algorithm                            | 118 |

|    |       | 6.5.3 Final application derivation                           | 123 |

|    | 6.6   | Experimental Results                                         | 124 |

|    |       | 6.6.1 Comparison to existing memory reuse methodologies .    | 124 |

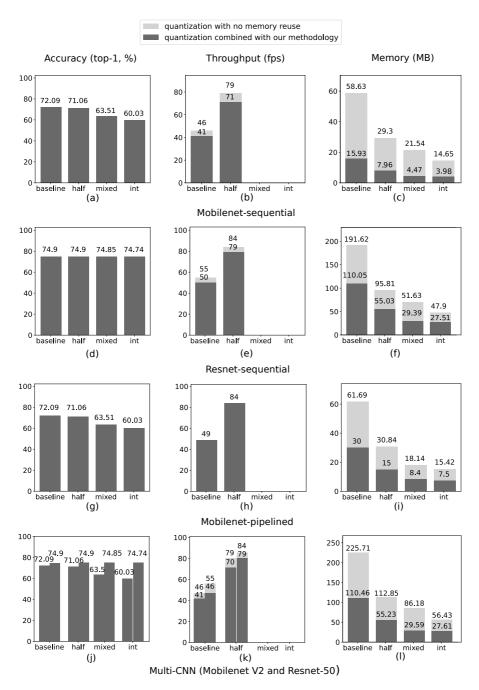

|    |       | 6.6.2 Joint use of quantization and our proposed methodology | 128 |

|    | 6.7   | Conclusions                                                  | 132 |

| 7  | Sum   | mary and concluding remarks                                  | 133 |

| Bi | bliog | raphy                                                        | 137 |

| Su | ımma  | ry                                                           | 149 |

| Sa | menv  | vatting                                                      | 151 |

|    |       | Publications                                                 | 153 |

|    |       | lum Vitae                                                    | 155 |

|    |       |                                                              |     |

| A( | Knov  | vledgments                                                   | 157 |

# **List of Figures**

| 1.1  | CNN                                                                | 2  |

|------|--------------------------------------------------------------------|----|

| 1.2  | Execution of CNNs as cloud services and at the Edge                | 2  |

| 1.3  | Current trends in the design and inference of CNN-based ap-        |    |

|      | plications executed at the Edge                                    | 5  |

| 1.4  | CNNs associated with alternative manners of execution              | 7  |

| 1.5  | Extended CNN design flow                                           | 10 |

| 2.1  | CNN model                                                          | 18 |

| 2.2  | Processing of input data $X_2$ by layer $l_2 \ldots \ldots \ldots$ | 21 |

| 2.3  | Padding                                                            | 22 |

| 2.4  | Jetson TX2 edge platform                                           | 24 |

| 2.5  | data-level parallelism                                             | 26 |

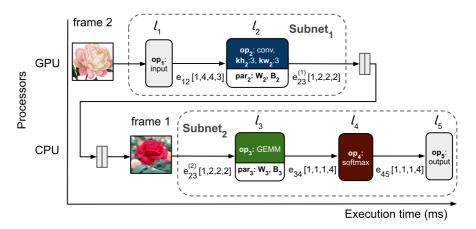

| 2.6  | task-level (pipeline) parallelism                                  | 27 |

| 2.7  | CSDF model of computation                                          | 29 |

| 2.8  | SDF model of computation                                           | 29 |

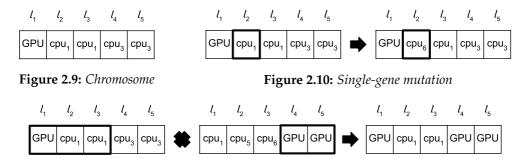

| 2.9  | Chromosome                                                         | 30 |

| 2.10 |                                                                    | 30 |

| 2.11 | Simple two-parent recombination (cross-over)                       | 30 |

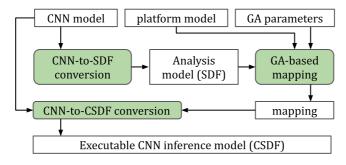

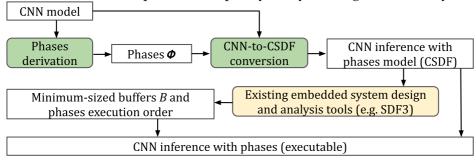

| 3.1  | Methodology for high-throughput CNN inference                      | 38 |

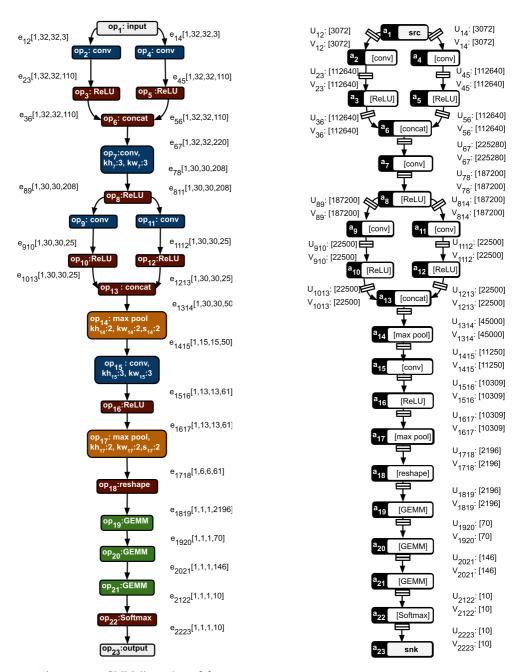

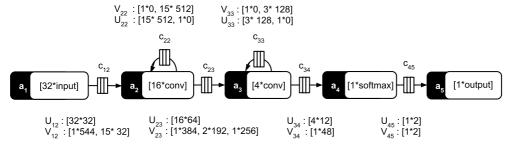

| 3.2  | CNN (input) model                                                  | 39 |

| 3.3  | SDF (analysis) model                                               | 39 |

| 3.4  | CSDF (executable CNN inference) model                              | 40 |

| 3.5  | Mapping chromosome example                                         | 43 |

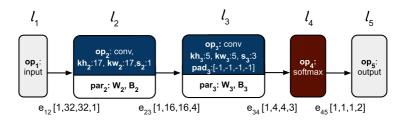

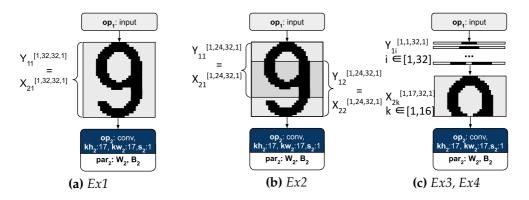

| 4.1  | Example CNN                                                        | 57 |

| 4.2  | Input data processing by layer $l_2 \ldots \ldots \ldots \ldots$   | 58 |

| 4.3  | Input data processing by layer $l_3$ , Ex4                         | 59 |

| 4.4  | Methodology for low-memory CNN inference                           | 60 |

| 4.5  | CSDF model, derived from the CNN model shown in Figure 4.1         | 62 |

xii List of Figures

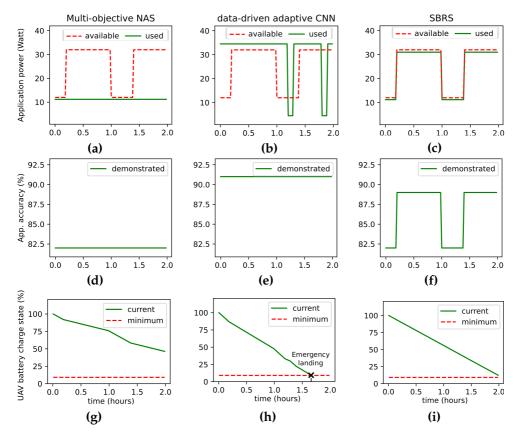

| 5.1 | Execution of a CNN-based application, affected by the applica-  |     |

|-----|-----------------------------------------------------------------|-----|

|     | tion environment and designed using different methodologies     | 76  |

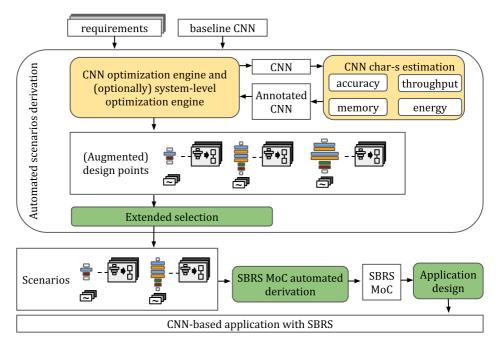

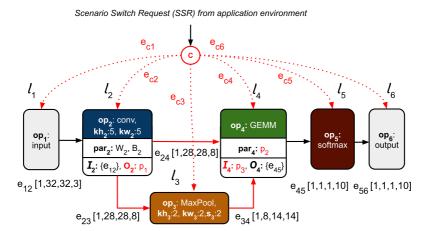

| 5.2 | SBRS methodology                                                | 79  |

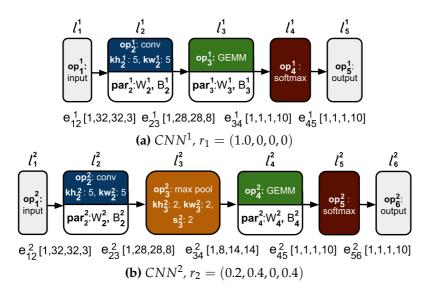

| 5.3 | Application scenarios                                           | 80  |

| 5.4 | SBRS MoC                                                        | 82  |

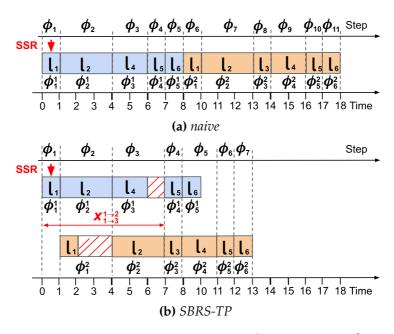

| 5.5 | Switching from scenario $CNN^1$ to scenario $CNN^2$             | 90  |

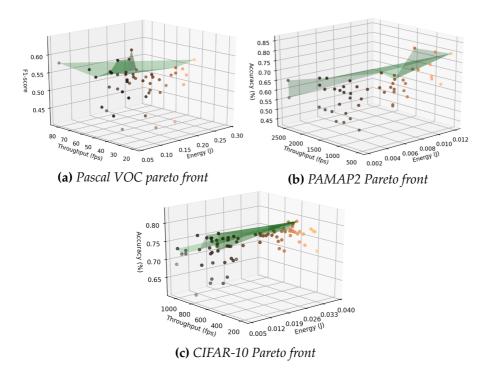

| 5.6 | Pareto-fronts based on 3 evaluation parameters, namely, accu-   |     |

|     | racy (F1-score for Pascal VOC), throughput and energy           | 98  |

| 5.7 | SBRS-TP efficiency evaluation                                   | 102 |

| 5.8 | Comparison between SBRS MoC and MSDNet CNN [39], per-           |     |

|     | forming classification on the CIFAR-10 dataset with throughput- |     |

|     | driven adaptive mechanism                                       | 104 |

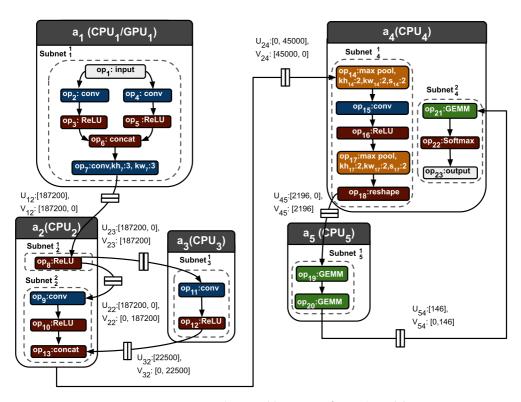

| 6.1 | Example CNN-based application <i>APP</i>                        | 111 |

| 6.2 | Our methodology design flow                                     | 114 |

| 6.3 | Experimental results                                            | 130 |

### **List of Tables**

| <ul><li>2.1</li><li>2.2</li></ul> | Attributes of layer $l_i$                                                                                                                    | 19<br>19 |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 3.1<br>3.2                        | Mapping example                                                                                                                              | 43<br>48 |

| 4.1<br>4.2<br>4.3                 | Execution of CNN inference with phases Evaluation of our memory reduction methodology CNN characteristics affecting CNN memory reduction and | 56<br>66 |

|                                   | throughput decrease                                                                                                                          | 67       |

| 5.1                               | Capturing of scenarios' components (layers and edges) in the                                                                                 |          |

|                                   | scenarios supergraph                                                                                                                         | 83       |

| 5.2                               | CNN-based applications                                                                                                                       | 96       |

| 5.3                               | Algorithm parameters for platform-aware NAS [82]                                                                                             | 97       |

| 5.4                               | Scenarios derived from pareto-fronts shown in Figure 5.6 for                                                                                 |          |

|                                   | three applications shown in Table 5.2                                                                                                        | 98       |

| 5.5                               | SBRS MoC memory reuse efficiency evaluation                                                                                                  | 100      |

| 6.1                               | Naive CNN buffers allocation                                                                                                                 | 112      |

| 6.2                               | Reused CNN buffers                                                                                                                           | 115      |

| 6.3                               | reduced CNN buffers                                                                                                                          | 120      |

| 6.4                               | Chromosome                                                                                                                                   | 121      |

| 6.5                               | Comparison of the memory reduction principles and features                                                                                   |          |

|                                   | associated with the memory reuse methodologies in [76], [65],                                                                                |          |

|                                   | and our proposed methodology                                                                                                                 | 125      |

| 6.6                               | Experimental Results                                                                                                                         | 126      |

| 6.7                               | Applications                                                                                                                                 | 128      |

| 6.8                               | Quantization in the TensorFlow DL framework [1]                                                                                              | 129      |

### **List of Abbreviations**

BFS Breadth-First Search

CNN Convolutional Neural Network

CPU Central Processing Unit

CSDF Cyclo-Static Data Flow

DL Deep Learning

DSE Design Space Exploration

FC Fully Connected

FLOP floating-point operation

FPGA Field-programmable Gate Array

GA Genetic Algorithm

GPU Graphics Processing Unit

HAR Human Activity Recognition

IoT Internet-of-Things

KD Knowledge Distillation

MB MegaBytes

MoC Model of Computation

MPSoC Multi-Processor System-on-Chip

NAS Neural Architecture Search

xvi List of Abbreviations

ONNX Open Neural Network Exchange Format

SBRS Scenario-Based Run-time Switching

SDF Synchronous Data Flow

SOTA State Of The Art

SSR Scenario Switch Request

TPU Tensor Processing Unit

UAV Unmanned Aerial Vehicle

### **Chapter 1**

### Introduction

In N recent years, the field of Deep Learning (DL) [33] has received great attention. This new and rapidly developing field has achieved state-of-the-art results in solving problems in areas such as image processing, computer vision, speech recognition, machine translation, medical information processing, robotics and control, bio-informatics, natural language processing, and many others [4]. One of the most popular DL algorithms are Convolutional Neural Networks (CNNs) [56]. Nowadays, CNNs are the front-runners of image processing and computer vision tasks such as image segmentation, classification, and object detection in both academia and industry [4]. The success of CNNs is due to their ability to automatically, effectively, and adaptively extract and process high- and low-level abstractions from multi-dimensional (2D and 3D) data such as images or video. This capability is mostly associated with the CNNs architecture, inspired by the biological processes in the visual cortex of an animal [55].

A CNN consists of a set of interconnected elements, called *neurons*. The connected neurons exchange data: each neuron accepts input data, provided by other neurons or external sources, and generates data for other neurons. To generate its output data, a neuron applies a mathematical *operator* such as convolution, dot product, pooling, and others [59] to its input data. To perform the operator, the neuron uses a set of *parameters*, also referred as *weights*. The values of the weights are obtained via *training*: a computationally intensive procedure, through which a CNN processes large volumes of data and learns how to perform its respective task. The neurons performing the same operator form hierarchically organized groups called *layers*. Typically, a CNN has one input layer, one output layer, and one or more hidden layers. The input layer receives the CNN input data (e.g. an image) and passes it to

the first hidden layer. The hidden layers transform the input data using the respective operators, and pass the data from the input layer to the output layer. Finally, the output layer produces the CNN output (e.g. an image classification result). A simplified example of a CNN, performing image classification, is shown in Figure 1.1. The CNN has one input layer, one output layer, and six hidden layers. The number of layers in the CNN and the number of neurons per layer are often referred as the CNN *depth* and *width*, respectively.

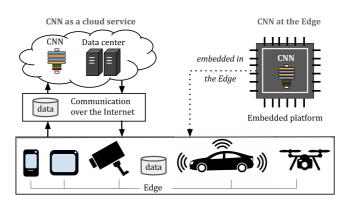

The state-of-the-art CNNs are characterized with large width (hundreds of neurons per layer) and depth (hundreds to thousands of layers). They have millions of parameters and perform billions of computations, requiring large amount of hardware platform resources for their deployment and execution. Therefore, CNNs are usually deployed on high-performance platforms: GPU clusters and data centres. For applications, deployed on *Edge platforms* (mobile phones, tablets, cameras, etc.), CNNs are typically provided as cloud services. Execution of a CNN as a cloud service is shown in Figure 1.2 (on the left). To use a CNN provided as a cloud service, an application deployed at the Edge communicates with a server over the Internet. First, the application sends a request to the cloud server. The request contains data collected at the Edge, e.g., images from a CCTV camera. Then, a CNN deployed on a high-performance platform in the cloud processes the data (e.g., performs classification of the images) and sends the result back to the Edge platform.

It is important to note that the communication between the cloud server and the Edge platform takes place over the Internet. Because of this, execution of CNNs as cloud services suffers from low responsiveness and has privacy issues. This is unacceptable for many CNN-based applications. For example,

Figure 1.1: CNN

**Figure 1.2:** *Execution of CNNs as cloud services and at the Edge*

CNN-based navigation in self-driving cars [24] cannot tolerate variable and large response delays occurring due to the communication between the car and a server. These delays can lead to incorrect navigation of the car and, subsequently, endanger the life of passengers. Another example is applications in medicine [62] that use CNNs to analyse private data of patients. These applications cannot send their data over the Internet because this could lead to private data leakages and violation of patients' privacy rights. To address these concerns, many modern CNN-based applications shift the execution of CNNs to the Edge. Execution of a CNN at the Edge is shown in Figure 1.2 (on the right). When executed at the Edge, CNNs are deployed close to the source of data (e.g. camera or sensors) and to the rest of the CNN-based application (e.g. camera software, which collects the application data). They do not require communication over the Internet and ensure high application responsiveness and security. In this thesis, we focus on deployment and execution of CNNs at the Edge.

## 1.1 Accuracy and platform-aware characteristics of a CNN

Execution of a CNN is characterized by accuracy and platform-aware characteristics. The *accuracy* of a CNN (typically measured in %) is the fraction of correct predictions generated by the CNN from the total number of predictions generated by the CNN. It is the main quality metric of a CNN which quantifies the CNN's ability to perform its respective task, e.g., to classify images correctly. The higher the CNN accuracy is, the better the CNN is at performing its respective task.

The *platform-aware characteristics* characterize the execution of a CNN on a target platform. The most common platform-aware characteristics of a CNN are:

- *throughput* (typically measured in frames per second, fps), i.e., the amount of data samples (e.g. images) processed per second;

- *latency* (typically measured in seconds, s), i.e., the time taken by a CNN to process one input sample (e.g. one image);

- energy cost (typically measured in Joules), i.e., the total amount of energy, required by a CNN to process one input sample;

- *memory cost* (typically measured in MegaBytes, MB), i.e., the total amount of memory, required to deploy and execute a CNN.

# 1.2 Requirements posed on a CNN executed at the Edge

While execution of CNNs at the Edge is desirable and beneficial, it is also very challenging due to numerous requirements posed on the CNNs by the CNN-based applications and target edge platforms. These requirements concern the characteristics of a CNN introduced in Section 1.1. With respect to these characteristics, the most common requirements, posed on CNNs executed at the Edge, are:

- *high accuracy*: the CNNs should be able to perform their tasks very well;

- *high throughput*: applications, such as CNN-based navigation in self-driving cars [24], require CNNs to process their input data streams fast, i.e., to have high throughput;

- *low latency*: many applications, such as navigation in drones [53], require CNNs to have low latency, i.e., as small as possible delay between accepting an input and providing the respective output;

- *low memory cost*: typical edge platforms, used for CNN execution, have limited amount of memory available. Thus, to be deployed and executed on these platforms, CNNs should have low memory footprint;

- *low energy cost*: the energy budget of edge platforms, especially battery-powered ones such as drones [58], is very limited. Thus, CNNs executed on such platforms should have low energy consumption.

# 1.3 Current trends in the design of CNNs executed at the Edge

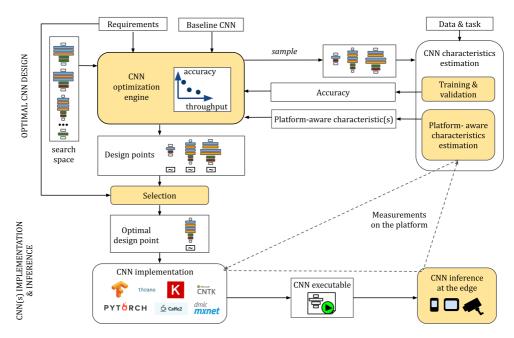

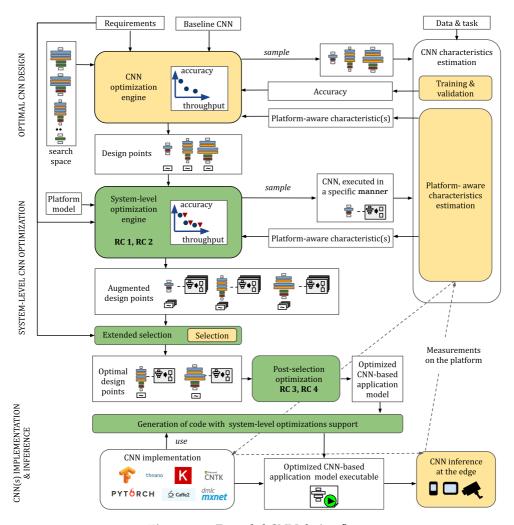

State-of-the-art methodologies for designing CNNs executed at the Edge typically follow the design flow shown in Figure 1.3. The heart of the design flow is the *CNN optimization engine* which performs automated search for optimal CNN architecture and weights. To perform the search, the CNN optimization engine uses techniques such as platform-aware Neural Architecture Search (NAS) [9,25,34,38,46,92,105] and CNN compression [41,99,106]. As inputs, the CNN optimization engine accepts: 1) A set of requirements posed on the CNN. The typical requirements posed on a CNN executed at the Edge are introduced in Section 1.2; 2) A *search space* which determines how the architecture of a

**Figure 1.3:** Current trends in the design and inference of CNN-based applications executed at the Edge

CNN can be constructed, i.e., which operators can be used by the CNN layers, which connections exist among the neurons of the layers, how many neurons and layers can a CNN have, etc. Also, it determines which CNN architectures are valid. Often specified as a set of rules, the search space defines a very large or even unbound set of valid CNNs that are able to solve the desired task; 3) (Optionally) A *baseline CNN*: a well-known, typically hand-crafted CNN, proven to solve the required task with high accuracy. The baseline CNN determines how the search is initialized, i.e., which CNNs are considered at the first step of the search. If no baseline CNN is specified, the CNN optimization engine initializes the search with CNNs randomly selected from the search space.

After the search is initialized with the first sample set of CNNs, the CNN optimization engine starts to explore the search space. The sample CNNs are passed to the *CNN characteristics estimation* component, which estimates the accuracy and platform-aware characteristics of the CNNs and returns the estimations back to the CNN optimization engine. The estimation of the CNN accuracy typically involves *training* and *validation* of the CNN. During the training, the CNN processes large volumes of data and learns how to perform

its task. During the validation, the CNN is applied to new data, unseen during the CNN training, and the CNN accuracy is computed [78]. The estimation of the platform-aware characteristics of a CNN involves either direct measurements on the target edge platform [105], or analytical formulas [34], or a combination of measurements on the platform together with analytical formulas [105]. It is worth noting that most of the approaches used for estimation of the platform-aware characteristics employ the combined estimation. Therefore, these approaches enable for more efficient (in terms of time and labour) estimation compared to only measurements on the platform, and more precise estimation compared to only analytical formulas [54,60,103].

Based on the received estimations, the input requirements, and the employed search/optimization strategy, the CNN optimization engine tries to improve the characteristics of the sample CNNs by altering the architecture and (possibly) the amount of CNNs. Typical alterations of a CNN architecture include changing the size (width and depth) of the CNN, adding and removing connections between the CNN neurons, reducing the precision of the CNN data and weights, and others [9,25,41,99,106]. The updated sample CNNs are then forwarded again for characteristics estimation. Thus, the exploration of the search space is a cycle, where every iteration involves sampling of CNNs and estimation of the CNNs' characteristics. The cycle continues until either a certain number of iterations is performed or a special condition is met (e.g., characteristics of the CNNs no longer improve). The result of the exploration is a set of CNNs, characterized with different architecture, weights, accuracy, and platform-aware characteristics. Hereinafter, we refer to these CNNs as to design points. The design points are passed to the selection component which chooses a single optimal design point from these CNNs.

The optimal design point is *implemented*, i.e., represented as an executable application and deployed on the target edge platform. The implementation and deployment of a CNN on an edge platform is a complex task requiring indepth knowledge in the fields of Deep Learning (DL) and Embedded Systems Design. Fortunately, this task can be greatly simplified through the use of DL frameworks such as Keras [19], Pytorch [75], Tensorflow [1], TensorRT [72] and others [74]. These frameworks provide a highly abstract user-friendly API for implementation and deployment of CNNs at the Edge together with a library of highly optimized operators performed by the CNN layers. The deployed CNN is ready for its *inference* phase, at which the CNN performs its respective task on the real-world data collected at the Edge.

# 1.4 Limitations of the state-of-the-art design flow for CNNs executed at the Edge

In this section, we highlight two limitations that exist in the design flow shown in Figure 1.3. Also, we show the negative impact of these limitations on the design of CNNs executed at the Edge.

#### 1.4.1 Limitation 1

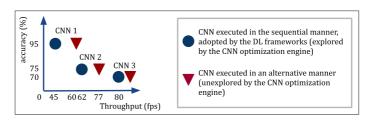

The first limitation concerns the search for design points performed by the CNN optimization engine. As mentioned in Section 1.3, the CNN optimization engine explores CNNs with different architectures and weights and tries to find CNNs that are optimal in terms of the characteristics introduced in Section 1.1. To estimate the characteristics of the CNNs, the CNN optimization engine relies on the CNN characteristics estimation component. At this point, the CNN characteristics estimation component and the CNN optimization engine adopt Limitation 1: a CNN is assumed to be executed sequentially, i.e., layer-by-layer. This sequential manner of CNN execution is widely accepted by the DL frameworks [1, 19, 72, 74, 75] and is often used to execute CNNs. Nonetheless, layer-by-layer execution is not guaranteed to be optimal with respect to every edge platform and every set of requirements posed on a CNN. Recent works [22,44,45,48,50,101,110] show that there are alternative (non-sequential) manners to execute a CNN at the Edge. Moreover, these works show that a CNN may have better characteristics when executed in an alternative manner than when executed layer-by-layer. However, alternative manners of CNN execution are not explored by the CNN optimization engine. Thus, due to Limitation 1, the existing methodologies for designing CNNs, executed at the Edge, may miss optimal design points. We illustrate this in Figure 1.4 where we show three example CNNs, characterized with accuracy and throughput, and associated with two manners of CNN

**Figure 1.4:** CNNs associated with alternative manners of execution

execution: 1) the sequential manner, accepted by the DL frameworks and assumed by the CNN optimization engine (shown as round points); 2) an alternative (non-sequential) manner, optimal with respect to the target edge platform and requirement of high throughput, posed on the CNNs (shown as triangle points). The accuracy of the CNNs does not depend on the manner the CNNs are executed, and therefore the accuracy is the same for a round point and a triangle point, associated with the same CNN. For example, the accuracy of CNN 1 is 95% irrespective of the manner CNN 1 is executed. The throughput of the CNNs is higher (i.e., better) when a CNN is executed in the non-sequential manner, optimal with respect to the target edge platform and requirements posed on the CNN - see the triangle points in Figure 1.4. Thus, these CNNs have better characteristics (same accuracy and better throughput) when they are executed in the non-sequential manner (triangle points), than when they are executed in the sequential manner (round points). However, due to **Limitation 1** mentioned above, the triangle points are missed by the CNN optimization engine.

#### 1.4.2 Limitation 2

The second limitation concerns the selection of the final CNN from the set of design points, performed by the selection component shown in Figure 1.3. Limitation 2 is formulated as follows: currently, from the set of design points provided by the CNN optimization engine, only one design point (CNN) is selected to perform the required task in a CNN-based application. With respect to the posed requirements, the selected CNN is characterized with certain accuracy and platform-aware characteristics that remain unchanged during the CNN-based application run-time. As a consequence, the needs of CNN-based applications, affected by changes in the application environment during run-time, cannot be optimally served. To illustrate this we give an example of a CNN-based road traffic monitoring application [53], which needs vary at the application run-time. The example application is executed on a drone. While flying, the drone takes images of the road and performs CNN-based recognition on these images. If there is a car accident or a traffic jam, the drone reports to the human operator. Depending on the situation on the roads and the level of the drone battery, the example application poses different requirements on the CNN. If the traffic is heavy, the application requires the CNN to have high throughput and high accuracy to process its input data, which typically means high energy consumption. During a traffic jam, when the high throughput is not required, or in case the battery of the drone is running low, the application would function optimally if the CNN

has reduced energy consumption at the cost of decreased throughput. If the example CNN-based application uses only one CNN to perform road traffic monitoring, it can either use a CNN with high throughput, high accuracy, and high energy cost, needed for a heavy-traffic application scenario, or use a CNN with reduced energy cost, as well as reduced accuracy and throughput. If the application uses a CNN with high throughput, high accuracy, and high energy cost, it optimally serves the application needs when the traffic is heavy, but does not optimally serve the application needs during a traffic jam or when the drone battery is low. Analogously, if the application uses a CNN with reduced energy cost, as well as reduced accuracy and throughput, it optimally serves the application needs during a traffic jam or when the drone battery is low, but not when the traffic is heavy. Thus, if the application uses only one CNN, the needs of the application cannot be optimally served during run-time in a changing application environment.

### 1.5 Research contributions

In this thesis, we try to relax the two limitations, outlined in Section 1.4, concerning the state-of-the-art CNN design flow shown in Figure 1.3. By relaxing the limitations, we try to reduce the negative impact of the limitations on the design of CNNs executed at the Edge. To this end, we extend the state-of-the-art CNN design flow shown in Figure 1.3 and explained in Section 1.3. The extended design flow is shown in Figure 1.5. The new components are shown in dark green. The extended design flow is one of our important research contributions. To realize the extended design flow, we propose other important research contributions (RC), summarized in Section 1.5.1, Section 1.5.2, Section 1.5.3, and Section 1.5.4, and denoted in Figure 1.5 as RC 1, RC 2, RC 3, and RC 4, respectively.

To relax **Limitation 1**, we extend the design flow with the *system-level optimization engine*. The system-level optimization engine accepts as an input the design points (CNNs), produced by the CNN optimization engine and assumed to be executed sequentially (layer-by-layer). The system-level optimization engine searches for alternative (non-sequential) manners to execute the input CNNs, thereby trying to find optimal design points missed by the CNN optimization engine. Along with the input CNNs, the system-level optimization engine accepts requirements posed on the CNNs and an edge platform model. The edge platform model which will be explained in details in Section 3.4 provides simplified, yet accurate description of a target edge platform to aid the search. As an output, the system-level optimization engine

Figure 1.5: Extended CNN design flow

produces a set of *augmented design points* which contains the input CNNs associated with multiple alternative manners of execution. An example set of augmented design points is shown in Figure 1.4 and explained in Section 1.4. As shown in Figure 1.5, we place the system-level optimization engine after the CNN optimization engine. We note that the system-level optimization engine can also be placed within the CNN optimization engine. However, such positioning leads to a problem: it requires modifications of existing platform-aware NAS and CNN compression techniques and tools, used by the CNN optimization engine. Thus, it violates the principle of software architecture

modularity [80] and greatly complicates the reuse of existing platform-aware NAS and CNN compression techniques and tools. To avoid this problem, we place the system-level optimization engine after the CNN optimization engine. To realize the system-level optimization engine, in this thesis, we propose and utilize two novel methodologies that explore alternative manners of CNN execution: the methodology for high-throughput CNN inference, summarized in Section 1.5.1 and the methodology for low-memory CNN inference, summarized in Section 1.5.2. In Figure 1.5, the methodologies are denoted as research contributions **RC 1** and **RC 2**, respectively. It is worth noting that, while the two proposed methodologies are important for finding optimal design points, the capabilities of the system-level optimization engine are not limited to these methodologies. To enrich the performed system-level optimizations, the system-level optimization engine may integrate other complimentary methodologies such as methodologies proposed in [101] and [93].

To relax **Limitation 2**, we extend the design flow with the *extended selection* component and the post-selection optimization component. The extended selection component enables for selection of multiple pareto-optimal [18] design points (CNNs) along with the selection of the single optimal design point, offered by the (original) selection component. The post-selection optimization component determines how to optimally use multiple design points to best serve the needs of a CNN-based application. The post-selection optimization component introduces run-time adaptivity into a CNN-based application affected by changes in the application environment at run-time, and performs joint CNNs memory optimization of multiple design points (CNNs) used by a CNN-based application. As an output, the post-selection optimization component produces the final CNN-based application model which embeds the functionality of the CNNs used by the application as well as the system-level optimizations introduced into the application. To realize the post-selection optimization component, we propose and utilize two novel methodologies: the methodology for run-time adaptive inference of CNN-based applications, summarized in Section 1.5.3, and the methodology for joint memory optimization of multiple CNNs, summarized in Section 1.5.4. In Figure 1.5, the methodologies are denoted as research contributions RC 3 and RC 4, respectively.

Finally, we extend the design flow with a component that performs *generation of code with system-level optimizations support*. The code generation component accepts as an input the optimized CNN-based application model, produced by the post-selection optimization component, and implements this model. We introduce the code generation component because the optimized

CNN-based application model cannot be implemented using only the DL frameworks that generate CNN-based application code in the state-of-the-art design flow shown in Figure 1.3. More precisely, the existing DL frameworks do not support the system-level optimizations (e.g., alternative manners of CNN execution and run-time adaptivity) embedded into the optimized CNN-based application model as explained above. Therefore, we extend the design flow with the code generation component which uses: 1) the existing DL frameworks to implement the CNNs functionality; 2) custom system-level design tools to implement the system-level optimizations. As an output, the code generation component provides an executable file with implementation of the input CNN-based application model. Although the code generation component is not presented as a separate research contribution in this thesis, it is used for implementation of the CNN-based applications and evaluation of the methodologies summarized in Section 1.5.1, Section 1.5.2, Section 1.5.3, and Section 1.5.4.

### 1.5.1 RC1: Methodology for high-throughput CNN inference

In this section, we summarize our novel methodology for high-throughput CNN inference at the Edge. The proposed methodology is based on our publication [67] and is explained in details in Chapter 3. The methodology exploits two types of parallelism, data-level parallelism and task-level parallelism, available in a CNN, to efficiently distribute (map) the computations within the CNN to the computational resources of an edge platform. The CNN distribution (mapping) is considered efficient if it ensures high CNN throughput. To find an efficient CNN mapping, our proposed methodology uses a Genetic Algorithm (GA) [85]. Exploitation of task-level (pipeline) parallelism together with data-level parallelism is the main novel feature of our proposed methodology. This feature distinguishes our methodology from the existing DL frameworks, introduced in Section 1.3, that utilize only task-level (pipeline) parallelism or only data-level parallelism, available in a CNN, to ensure high CNN throughput. Thanks to the combined use of task- and data-level parallelism, our proposed methodology takes full advantage of all computational resources that are available on the edge platform, and ensures very high CNN throughput. To evaluate our proposed methodology, we perform experiments where we apply our methodology to real-world CNNs from the Open Neural Network Exchange Format (ONNX) models zoo [7] and execute the CNNs on the NVIDIA Jetson TX2 edge platform [71]. We compare the throughput demonstrated by the CNNs mapped on the Jetson TX2 platform using: 1) our proposed methodology; 2) the best-known and state-of-the-art TensorRT DL

framework [72] for the Jetson TX2 edge platform. The experimental results shown that 1.36% to 42% higher throughput is achieved, when the CNNs are mapped using our methodology. We note that our proposed methodology considers edge platforms with computational resources composed of CPUs and GPUs because such platforms are most often used to execute applications, requiring high CNN throughput [32, 109]. However, extending our proposed methodology to other types of edge platforms (e.g., FPGA-based platforms [32]) is straightforward due to the modularity and generality of our methodology.

### 1.5.2 RC2: Methodology for low-memory CNN inference

In this section, we summarize our novel methodology for low-memory CNN inference at the Edge. The proposed methodology is based on our publication [65] and is explained in details in Chapter 4. To ensure low memory cost of the CNN inference, the methodology splits the data, processed by layers of a CNN, in parts and efficiently reuses the edge platform memory, allocated to store the data parts. Processing data by parts is the key novel feature of our proposed methodology. It enables our methodology to reduce the CNN-based application memory footprint without affecting the main CNN quality metric, i.e., the CNN accuracy. This compares favourably with the most common CNN memory reduction methodologies such as pruning and quantization [41,99,106] that reduce the CNN inference memory footprint at the cost of decreased CNN accuracy. However, data processing by parts may cause CNN execution time overheads (e.g., CNN layers may require time to switch among the data parts), leading to CNN throughput decrease. Thus, the proposed methodology reduces the amount of memory occupied by a CNN at the cost of reduced CNN throughput. The experimental results show that taking real-world CNNs from the ONNX models zoo [7] and applying our memory reduction methodology to these CNNs, the CNNs memory cost is reduced by 2.8% to 38% when compared to the memory reduction achieved by the state-of-the-art TensorRT DL framework [72].

## 1.5.3 RC3: Methodology for run-time adaptive inference of CNN-based applications

In this section, we summarize our novel methodology for run-time adaptive inference of CNN-based applications. The proposed methodology is based on our publication [64] and is explained in details in Chapter 5. The methodology enables to adapt a CNN-based application to changes in the application

environment during run-time. It is based on the concept of scenarios [15], widely used in embedded systems design. According to this concept, an application can have different internal operation modes, called *scenarios*, each with its own typical characteristics or/and functionality. During run-time, the application can switch among the scenarios, thereby adapting its characteristics or functionality to changes in the application environment. In our scenario-based run-time switching (SBRS) methodology, a scenario is a CNN designed to conform to a specific set of requirements in terms of accuracy and platform-aware characteristics. An application can have multiple scenarios that conform to different application needs. During run-time, the application can switch among the scenarios, thereby adapting its characteristics to its needs. To enable for run-time adaptivity, our SBRS methodology represents a CNN-based application as a novel SBRS model of computation (MoC) which embeds the functionality of the application scenarios as well as mechanisms for run-time adaptivity. Additionally, the methodology proposes an SBRS transition protocol which ensures high application responsiveness during the scenarios switching. The experimental results, where we apply our methodology to three real-world applications from two different domains, show that our SBRS methodology: 1) Adapts a CNN-based application to changes in the environment, thereby ensuring optimal service to the needs of the application at any given point in time; 2) Enables for fast switching between the application scenarios due to our novel SBRS transition protocol; 3) Outperforms the most relevant existing methodology called MSDNet [39].

## 1.5.4 RC4: Methodology for joint memory optimization of multiple CNNs

In this section, we summarize our novel methodology for joint memory optimization of multiple CNNs. The proposed methodology is based on our publication [66] and is explained in details in Chapter 6. As mentioned earlier, to relax Limitation 2, our extended design flow allows a CNN-based application to use multiple CNNs instead of one CNN to perform its functionality. However, this may dramatically increase the application memory cost, while as explained in Section 1.2, low memory cost is required for CNN-based applications executed at the Edge. Thus, execution of a multi-CNN application (an application using multiple CNNs) at the Edge may require aggressive optimizations to reduce the application memory cost. Typically, these optimizations are performed using methodologies such as pruning and quantization [41,99,106]. These methodologies reduce the number or precision of CNN parameters, thereby reducing the CNN memory cost. However, at

high CNN memory reduction rates, these methodologies decrease the CNN accuracy, while as mentioned above, high CNN accuracy is very important for many CNN-based applications. To achieve high CNN memory reduction and avoid substantial decrease of CNN accuracy, the CNN pruning and quantization methodologies can be combined with the CNN memory reuse methodologies such as the methodologies in [47] and [76]. Orthogonal to the pruning and quantization methodologies, the CNN memory reuse methodologies reuse the platform memory allocated to store intermediate CNN computational results, produced by the CNN layers. Thus, these methodologies further reduce the application memory cost without decreasing the CNN accuracy. However, these methodologies account for the state-of-the-art CNN design flow shown in Figure 1.3, and thus adopt Limitation 1 and Limitation 2, outlied in Section 1.4. Due to Limitation 1, these methodologies do not account for non-sequential manners of CNN execution, and are often unfit for CNNs executed in a non-sequential manner. Due to Limitation 2, these methodologies can reuse platform memory within a CNN, but not among multiple CNNs, thereby missing opportunities for inter-CNN memory reuse. To address these issues, we propose our methodology for joint memory optimization of multiple CNNs. Unlike the existing memory reuse methodologies, our proposed methodology reuses memory among multiple CNNs, and is suitable for CNNs executed in a non-sequential manner. To evaluate our proposed methodology, we perform experiments where we apply our methodology to six real-world state-of-the-art CNN-based applications. The experimental results show that our methodology enables for up to 6 times memory reduction, compared to deployment of CNN-based applications with no memory reduction and 10% to 30% memory reduction, compared to other CNN memory reuse methodologies. Additionally, the experimental results demonstrate that our methodology can be efficiently combined with orthogonal methodologies such as CNN pruning and quantization.

### 1.6 Thesis organization

Below, we give an outline of this thesis, summarizing the contents of the following chapters. **Chapter 2** presents the background, i.e., concepts necessary to understand the contributions of this thesis. Chapter 3 to Chapter 6 contain the main contributions of this thesis. Each chapter is organized in a self-containing manner, meaning that each chapter contains a more specific introduction to the research problem and contribution, a related work, the proposed solution methodology, an experimental evaluation, and a concluding

discussion.

**Chapter 3** presents our novel methodology for high-throughput CNN inference. This chapter is based on our publication [67].

**Chapter 4** presents our novel methodology for low-memory CNN inference. This chapter is based on our publication [65].

**Chapter 5** presents our novel methodology for run-time adaptive inference of CNN-based applications. This chapter is based on our publication [64].

**Chapter 6** presents our novel methodology for joint memory optimization of multiple CNNs. This chapter is based on our publication [66].

Finally, **Chapter 7** ends this thesis by providing a summary and concluding remarks for the research work presented in this thesis.

### **Chapter 2**

### **Background**

N this chapter, we present an overview of concepts essential to understand 1 the contributions of this thesis. In Section 2.1, we present the CNN model used to represent a CNN in this thesis. In Section 2.2, we describe the CNN deployment and inference at the Edge, briefly introduced in Section 1.3 because in this thesis, we study and propose novel methodologies for efficient CNN deployment and inference at the Edge. In Section 2.3, we introduce a typical edge platform used to execute CNNs inference. Namely, we introduce the well-known and state-of-the-art NVIDIA Jetson TX2 platform [71], used to perform experiments in this thesis. In Section 2.4, we explain the task- and data-level parallelism available in a CNN. We exploit the aforementioned types of parallelism to ensure efficient inference of CNNs at the Edge. In Section 2.5, we briefly describe the Cyclo-Static Data Flow (CSDF) [10] and the Synchronous Data Flow (SDF) [57] models of computation, widely used in the Embedded Systems community to represent applications executed at the Edge. Unlike the CNN model, introduced in Section 2.1, the SDF model and the CSDF model explicitly specify the parallelism, available within an application (or a part of an application such as a CNN), and enable for modelling of various manners of application execution. In this thesis, we use the CSDF model and the SDF model to represent an augmented design point (i.e., a CNN, executed in a specific manner) briefly introduced in Section 1.5. Finally, in Section 2.6, we describe the basic concepts of a Genetic Algorithm (GA): a well-known heuristic approach, widely used for finding optimal solutions for complex Design Space Exploration (DSE) problems. Some of the methodologies, presented in this thesis, are based on a GA.

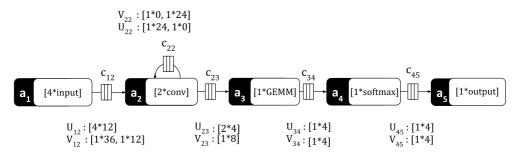

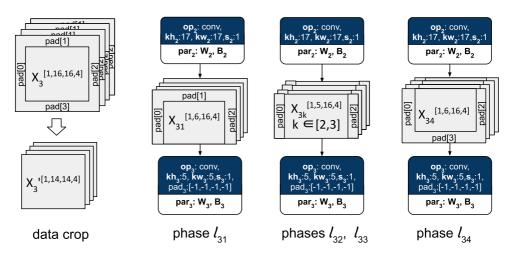

#### 2.1 CNN model

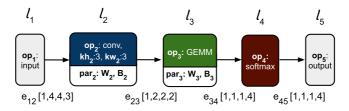

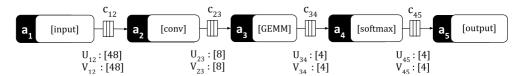

A Convolutional Neural Network (CNN) is commonly represented as a directed acyclic computational graph CNN(L,E) with a set of nodes L, also called layers, and a set of edges E. An example of a CNN model with a set of layers  $L = \{l_1, l_2, l_3, l_4, l_5\}$  and a set of edges  $E = \{e_{12}, e_{23}, e_{34}, e_{45}\}$  is shown in Figure 2.1.

Figure 2.1: CNN model

The CNN model specifies transformations over the CNN input data (e.g. an image), that result into the CNN output data (e.g. an image classification result). The transformations are specified by the set of layers L. Edges in the set E specify data dependencies between the layers and determine the flow of data in a CNN. The detailed explanation and formal definition of a layer  $l_i \in L$  and an edge  $e_{ij} \in E$  of the CNN model are given in Section 2.1.1 and Section 2.1.2, respectively.

### 2.1.1 Layer in the CNN model

Every layer  $l_i$  in the CNN model represents part of the CNN functionality. It accepts as an input some data, produced by other layers, transforms this data using a mathematical operator, and provides output data. Formally, we define layer  $l_i$  as a set of attributes, summarized in Table 2.1. Column 1 lists the attributes; Column 2 provides a description of each attribute; Column 3 lists limitations, posed on the attribute by the CNN model; Column 4 shows the *default* value of an attribute, i.e., the value assigned to the attribute which is not defined explicitly. We note that some of the attributes (e.g., attributes  $l_i$  and  $O_i$  shown in Rows 4 to 5 in Table 2.1) only take the default value. Below, we explain the attributes of layer  $l_i$ , summarized in Table 2.1, using as an example layer  $l_2$  shown in Figure 2.1.

Attributes  $type_i$  and  $op_i$  (Rows 2 to 3 in Table 2.1) specify the type and performed operator of layer  $l_i$ , respectively [4]. These attributes determine the main difference between the layers of a CNN. The most common types of

2.1. CNN model 19

**Table 2.1:** Attributes of layer  $l_i$

| attribute         | description  | limitations                            | default value                             |

|-------------------|--------------|----------------------------------------|-------------------------------------------|

| tuna              | layer        | supported by the                       | for known <i>op</i> <sub>i</sub>          |

| type <sub>i</sub> | type         | CNN model (see Table 2.2)              | see Table 2.2                             |

| on.               | operator     | restricted by                          |                                           |

| $op_i$            | operator     | $type_i$ (see Table 2.2)               | _                                         |

| $I_i$             | input edges  | $I_i \subseteq E : \forall e_{ji} \in$ | $E, e_{ji} \in I_i$                       |

| $O_i$             | output edges | $O_i \subseteq E : \forall e_{ij} \in$ | $E: e_{ij} \in O_i$                       |

| $X_i$             | input data   | see Equat                              | ion 2.1                                   |

| $Y_i$             | output data  | see Equat                              | ion 2.2                                   |

| $\Theta_i$        | sliding      | has smaller or equal                   | window of size                            |

| $\bigcup_{i}$     | window       | size compared to $X_i$                 | $kh_i \times kw_i$                        |

|                   |              | $0 < kh_i \le X_i.h;$                  | $X_i$ .h if $type_i \in \{data,FC\}$ ,    |

| l-h               | kernel       | typically $kh_i = kw_i$ ;              | else 1                                    |

| $kh_i$            | height       | $kh_i = X_i.h$ if                      |                                           |

|                   |              | $type_i \in \{data,FC\}$               |                                           |

|                   |              | $0 < kw_i \le X_i.w;$                  | $X_i$ . $w$ if $type_i \in \{data,FC\}$ , |

| lean              | kernel       | typically $kw_i = kh_i$ ;              | else 1                                    |

| $kw_i$            | width        | $kw_i = X_i.w$ if                      |                                           |

|                   |              | $type_i \in \{data,FC\}$               |                                           |

|                   |              | $s_i = 1 \text{ if } op_i \notin$      |                                           |

| $s_i$             | stride       | {conv, max pool,                       | 1                                         |

|                   |              | average pool}                          |                                           |

| $pad_i$           | padding      | an array of four                       | [0,0,0,0]                                 |

| puui              | padding      | integer numbers                        | [0,0,0,0]                                 |

| par <sub>i</sub>  | (trainable)  | a set of parameters,                   | Ø                                         |

| Puli              | parameters   | specific for CNN layer [4]             | <u> </u>                                  |

**Table 2.2:** Most common CNN layer types and operators

| layer type           | operators                                |

|----------------------|------------------------------------------|

| convolutional        | conv                                     |

| pooling              | (global) max pool, (global) average pool |

| activation           | ReLU, thn, sigmoid                       |

| data                 | input, output                            |

| fully connected (FC) | GEMM, MatMUL, dot                        |

| loss                 | softmax                                  |

| normalization        | BatchNormalization, LRN                  |

| arithmetic           | add                                      |

| transformation       | concat                                   |

layers and operators performed by layers of these types are shown in Table 2.2. For example, layer  $l_2$  shown in Figure 2.1 has  $type_2 = convolutional$  and performs operator  $op_2 = conv$ . Operator  $op_2$  performed by layer  $l_2$  is explicitly specified in Figure 2.1, thus the type of layer  $l_2$  is determined using Table 2.2.

Attributes  $I_i$  and  $O_i$  (Rows 4 to 5 in Table 2.1) specify the input and output edges of layer  $l_i$ , respectively. For example, layer  $l_2$  shown in Figure 2.1 has input edges  $I_2 = \{e_{12}\}$  and output edges  $O_2 = \{e_{23}\}$ .

Attributes  $X_i$  and  $Y_i$  (Rows 6 to 7 in Table 2.1) specify the input and output data of layer  $l_i$ , respectively. These attributes always take the default value, computed using Equation 2.1 and Equation 2.2.

$$X_{i} = \begin{cases} e_{ji}.data : e_{ji} \in I_{i} & \text{if } |I_{i}| = 1\\ \{e_{ji}.data\}, \forall e_{ji} \in I_{i} & \text{otherwise} \end{cases}$$

(2.1)

$$Y_{i} = \begin{cases} e_{ij}.data : e_{ij} \in O_{i} & \text{if } |O_{i}| > 0\\ \emptyset & \text{otherwise} \end{cases}$$

(2.2)

The value of attribute  $X_i$  is computed using Equation 2.1, where  $e_{ji}.data$  is the data accepted by layer  $l_i$  and associated with input edge  $e_{ji} \in I_i$  of layer  $l_i$ ;  $|I_i|$  is the total number of input edges of layer  $l_i$ . Typically, layer  $l_i$  has one input edge, i.e.,  $|I_i|=1$ . In this case, input data  $X_i$  of layer  $l_i$  is the data  $e_{ji}.data$ , associated with the only input edge  $e_{ji}$  of layer  $l_i$ . For example, layer  $l_2$  shown in Figure 2.1 has one input edge  $e_{12}$ , and has input data  $X_2=e_{12}.data$ . However, some layers may accept as an input data coming from multiple input edges (e.g., layers performing operator concat [4]) or accept no input data (e.g., layers performing the operator input [4]). Layers that accept no input data have  $|I_i|=0$  and  $X_i=\emptyset$ .

Analogously, the value of attribute  $Y_i$  is computed using Equation 2.2, where  $e_{ij}.data$  is the data produced by layer  $l_i$  and associated with output edge  $e_{ij} \in O_i$  of layer  $l_i$ ;  $|O_i|$  is the total number of output edges of layer  $l_i$ . Typically, layer  $l_i$  has at least one output edge and produces data  $Y_i \neq \emptyset$ , broadcasted to every output edge of layer  $l_i$ . For example, layer  $l_2$  shown in Figure 2.1 produces output data  $Y_2 = e_{23}.data$  onto its output edge  $e_{23}$ . However, some layers (e.g., layers performing the operator output [4]) do not produce data. These layers have  $|O_i| = 0$  and  $Y_i = \emptyset$ .

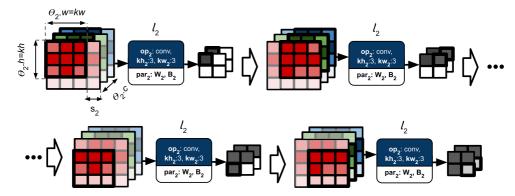

Attributes  $\Theta_i$ ,  $kh_i$ ,  $kw_i$ ,  $s_i$ , and  $pad_i$  (Rows 8 to 12 in Table 2.1) are the *hyper-parameters* of layer  $l_i$  [4]. These attributes, obtained during the CNN design, specify how the layer processes its input data. To process its input data  $X_i$ , layer  $l_i$  moves along  $X_i$  with sliding window  $\Theta_i$  and stride  $s_i$ , applying operator  $op_i$  to the area of  $X_i$ , covered by  $\Theta_i$ . The sliding window  $\Theta_i$  has

2.1. CNN model 21

**Figure 2.2:** Processing of input data  $X_2$  by layer  $l_2$

smaller or equal size, compared to  $X_i$ . The height and width of window  $\Theta_i$  are typically equal to the kernel height  $kh_i$  and kernel width  $kw_i$  of layer  $l_i$ , while the number of channels of  $\Theta_i$  is typically equal to the number of channels of  $X_i$  [4]. The areas, covered by  $\Theta_i$ , can overlap. Figure 2.2 shows an example, where layer  $l_2$  shown in Figure 2.1 processes its input data by four parts, covered by sliding window  $\Theta_2$  of size 3 x 3 x 3 pixels, and stride  $s_2 = 1$  pixel.

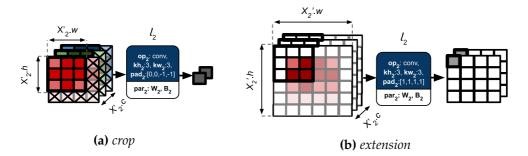

Before processing its input data, layer  $l_i$  may crop or extend its input data  $X_i$  to data  $X_i'$  with padding [4]. Typically, this is done to ensure that the input data of layer  $l_i$  can be covered by sliding window  $\Theta_i$  of layer  $l_i$  integer number of times [4]. We specify the padding of layer  $l_i$  as attribute  $pad_i$  (Row 12 in Table 2.1).  $pad_i$  is an array of four integer numbers. Elements of  $pad_i$ , referred as  $pad_i[0]$ ,  $pad_i[1]$ ,  $pad_i[2]$ , and  $pad_i[3]$ , respectively, specify the crop/extension of the height and width of data  $X_i$  as given in Equation 2.3 and Equation 2.4, respectively.

$$X'_{i}.w = pad_{i}[0] + X_{i}.w + pad_{i}[2]$$

(2.3)

$$X_i'.h = pad_i[1] + X_i.h + pad_i[3]$$

(2.4)

By default, layer  $l_i$  has  $pad_i = [0,0,0,0]$ , which means that layer  $l_i$  does not crop or extend its input data  $X_i$  before processing. Figure 2.3 shows an example where layer  $l_2$  crops (see Figure 2.3 (a)) and extends (see Figure 2.3 (b)) its input data  $X_i$  with padding  $pad_2 = [0,0,-1,-1]$  and  $pad_2 = [1,1,1,1]$ , respectively.

Beside the hyper-parameters, layer  $l_i$  has (trainable) parameters such as weights and biases [4], specified as attribute  $par_i$  (Row 13 in Table 2.1). As mentioned in Chapter 1, these parameters of layer  $l_i$  are obtained during the

Figure 2.3: Padding

CNN training and are used by operator  $op_i$  of layer  $l_i$ . For example, layer  $l_2$  has parameters  $par_2$  composed of weights  $W_2$  and biases  $B_2$ , used to perform  $op_2 = conv$ .

#### 2.1.2 Edge in the CNN model

Every edge  $e_{ij} \in E$  in the CNN model specifies a data dependency between layers  $l_i$  and  $l_j$  of a CNN, such that the data produced by layer  $l_i$  is accepted as an input by layer  $l_j$ . Formally, we define edge  $e_{ij}$  as a tuple  $(l_i, l_j, data)$ , where data is the data produced by layer  $l_i$ , accepted by layer  $l_j$ , and associated with edge  $e_{ij}$ . The data associated with edge  $e_{ij}$  is stored in a multidimensional array called tensor [4]. In this thesis, every data tensor has the shape [batch, h, w, ch], where batch, h, w, ch are the batch size [4], the height, the width, and the number of channels of the tensor, respectively. An example of edge  $e_{12} = (l_1, l_2, data)$  is shown in Figure 2.1. Edge  $e_{12}$  represents the data dependency between layers  $l_1$  and  $l_2$ , where layer  $l_2$  accepts as an input the data produced by layer  $l_1$ . Edge  $e_{12}$  is annotated with shape [1,4,4,3]. This means that the data tensor, exchanged between layers  $l_1$  and  $l_2$ , and associated with edge  $e_{12}$  has batch size = 1, height and width = 4, and number of channels = 3.

# 2.2 CNN deployment and inference at the Edge

The CNN inference is a process of applying the CNN to real-world data (e.g., images) and obtaining the CNN output (e.g., results of the input images classification). Nowadays, the CNN inference can be performed on a wide variety of hardware platforms. In this thesis, we concentrate on the CNN inference performed on edge (mobile and embedded) platforms, presented in Section 2.3.

Before the CNN inference can start, the CNN is *deployed* on a target platform, i.e., some memory of the platform is allocated to the CNN. The total amount of memory (in bytes), allocated to a CNN is computed as:

$$m = m_{par} + m_{buf} (2.5)$$

where  $m_{par}$  is the memory, required to store the CNN parameters (weights and biases) and computed using Equation 2.6;  $m_{buf}$  is the memory, required to store the CNN intermediate computational results and computed using Equation 2.7.

$$m_{par} = \sum_{i \in [1,|L|]} |par_i| * par\_size$$

(2.6)

In Equation 2.6,  $|par_i|$  is the total number of parameters, associated with layer  $l_i \in L$  of the CNN;  $par\_size$  is the size of one parameter in bytes;

$$m_{buf} = \sum_{B_k \in B} B_k.size \tag{2.7}$$

In Equation 2.7, B is a set of *buffers*, i.e., the memory segments, allocated to store the intermediate computational results of a CNN [76]. Every buffer  $B_k \in B$  has one or several CNN edges  $e_{ij}$  allocated to it. Buffer  $B_k$  stores data  $e_{ij}.data$ , exchanged between CNN layers  $l_i$  and  $l_j$  during the CNN inference and is characterized with size (in bytes) computed as:

$$B_k.size = max_{e_{ij} \in B_k.edges} \{ |e_{ij}.data| * token\_size \}$$

(2.8)

In Equation 2.8,  $e_{ij} \in B_k.edges$  is an edge, storing data in buffer  $B_k$ ;  $|e_{ij}.data|$  is the total number of data elements (tokens), exchanged through edge  $e_{ij}$ ;  $token\_size$  is the size of one token in bytes.

A CNN deployed on an edge platform can start its inference phase when the CNN can utilize the memory and the computational resources available on the platform to perform the CNN functionality, i.e., to execute all the layers in the CNN. Every layer can be executed on processors, such as CPUs, GPUs and/or FPGAs [17], available in the platform. If a platform has parallel processors (accelerators), such as GPUs or FPGAs, computations within the layer can be represented as one or multiple kernels [17] and offloaded on these accelerators by the CPUs. Otherwise, these computations are performed on the CPUs. If the computations within a CNN layer are offloaded on an accelerator with local memory, e.g., a GPU, the CNN layer input data and parameters, required to perform the computations, are copied from the main memory into

the local memory of the accelerator and the results of the computation are copied back to the main memory.

The layers of a CNN are executed in a specific order, determined by the data dependencies within the CNN and the manner the CNN is executed. Typically, the CNN layers are executed in a *sequential manner*, where the CNN execution is represented as |L| computational steps and at every i-th computational step, CNN layer  $l_i \in L$  is executed. However, as it will be explained in Section 2.4, a CNN can also be executed in *alternative* (non-sequential) manners, that involve exploitation of task-level (pipeline) parallelism, where the layers of the CNN are executed in parallel (pipelined) fashion. In this thesis, we consider both sequential and non-sequential manners of CNN execution. To represent a CNN, executed in a specific manner, we use the CSDF and SDF models of computation, presented in Section 2.5.

# 2.3 Edge platform used for CNN inference

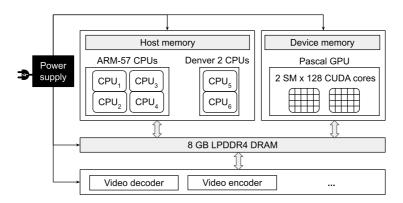

Modern edge platforms used to execute the CNN inference are complex systems that host a large number of specific hardware components: processors, memory, power supply elements, sensors and others [32, 109]. Figure 2.4 shows a simplified structure of the NVIDIA Jetson TX2 edge platform [71]: one of the best-known edge platforms used to execute CNNs.

To perform computations within a CNN, an edge platform may host multiple heterogeneous processors such as central processing units (CPUs), graphics processing units (GPUs), field-programmable gate arrays (FPGAs), and/or Tensor Processing Units (TPUs) [32, 109]. For example, the Jetson TX2 platform shown in Figure 2.4 hosts a double-core Denver 2 CPU and a

**Figure 2.4:** *Jetson TX2 edge platform*

quad-core ARM Cortex A57 CPU as well as an integrated Pascal GPU with a total of 256 CUDA cores. When the inference of a CNN is executed on the Jetson TX2 platform, computations within the CNN are typically performed on the GPU.

The memory infrastructure of an edge platform is used to store the CNN data and parameters, required for proper CNN inference. It typically consists of a *main memory*, accessible by all processes available on the platform, and a set of *local memories*, only accessible by specific processor(s). For example, the memory infrastructure of the Jetson TX2 platform shown in Figure 2.4 consists of the 8 GB LDDR4 DRAM, accessible by all the processors, available on the platform, as well as the *host\_memory* and *device\_memory*, i.e., the local memories, accessible only by the CPUs and the GPU, respectively.

The power supply elements of an edge platform provide power to all components available on the platform. Some edge platforms carry batteries that provide an autonomous limited power supply to the edge device. The Jetson TX2 platform, however, does not have a battery and requires an external power supply.

Finally, other components, available on the platform, e.g., video encoders and decoders, are used to collect data and facilitate parts of a CNN-based application other than the CNN itself.

# 2.4 Task- and data-level parallelism available in a CNN

As a computational model the CNN model is characterized with large amount of available parallelism. This parallelism can be exploited to speed-up the CNN inference and to efficiently utilize computational resources of an edge platform, where the CNN is executed.

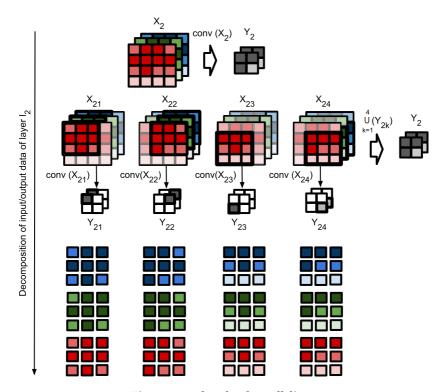

The most widely exploited type of parallelism available within CNNs is the *data-level parallelism*, illustrated in Figure 2.5. This type of parallelism involves the same computation, e.g., Convolution, performed by a CNN layer over the CNN layer input data partitions. Efficient utilization of data-level parallelism allows to speed-up the inference of a CNN by accelerating the execution of individual CNN layers. This type of parallelism is exploited by the majority of existing Deep Learning (DL) frameworks, such as Keras [19], Pytorch [75], Tensorlow [1], TensorRT [72] and others [74]. The data-level parallelism, available within layer  $l_i$  of a CNN can be explicitly expressed by decomposition of the layer input data tensor  $X_i$  into a set of K sub-tensors  $\{X_{i1}, X_{i2}, ..., X_{iK}\}$ , where: 1) all sub-tensors  $X_{ik}, k \in [1, K]$  can be processed in parallel by operator  $op_i$ . When layer  $l_i$  applies operator  $op_i$  to  $X_{ik}$ , it produces

Figure 2.5: data-level parallelism