# **Fault-tolerant satellite computing with modern semiconductors** Fuchs, C.M.

#### Citation

Fuchs, C. M. (2019, December 17). Fault-tolerant satellite computing with modern semiconductors. Retrieved from https://hdl.handle.net/1887/82454

Version: Publisher's Version

License: License agreement concerning inclusion of doctoral thesis in the

Institutional Repository of the University of Leiden

Downloaded from: <a href="https://hdl.handle.net/1887/82454">https://hdl.handle.net/1887/82454</a>

Note: To cite this publication please use the final published version (if applicable).

#### Cover Page

## Universiteit Leiden

The handle <a href="http://hdl.handle.net/1887/82454">http://hdl.handle.net/1887/82454</a> holds various files of this Leiden University dissertation.

**Author**: Fuchs, C.M.

Title: Fault-tolerant satellite computing with modern semiconductors

**Issue Date:** 2019-12-17

# Fault-Tolerant Satellite Computing with Modern Semiconductors

ISBN: 978-94-028-1766-9

# Fault-Tolerant Satellite Computing with Modern Semiconductors

#### Proefschrift

ter verkrijging van de graad van Doctor aan de Universiteit Leiden, op gezag van Rector Magnificus prof.mr. C.J.J.M. Stolker, volgens besluit van het College voor Promoties te verdedigen op dinsdag, 17 december 2019 klokke 11:15 uur door

Christian Martin Fuchs

Geboren te Linz, Oostenrijk in 1984

Promotor: Prof. Dr. A. Plaat

#### Promotiecommissie:

Dr. H. Quinn Los Alamos National Laboratory,

Los Alamos, USA

Prof. Dr. X. Wen Kyushu Institute of Technology, Japan

Dr. M.S. Gorbunov Scientific Research Institute of System Analysis,

Russian Academy of Sciences, Moscow, Russia

Prof. Dr. J.J. Liou National Tsing Hua University,

Hsinchu, Taiwan

Prof. Dr. S. Wu Shanghai Jiao Tong University,

Shanghai, China

Dr. M. Kenworthy

Prof. Dr. S. Manegold

Dr. E. Bakker

Prof. Dr. H. Wijshoff

## Contents

| Space: The Final Frontier                                |     |  |  |  |  |

|----------------------------------------------------------|-----|--|--|--|--|

| Space. The Time Tronsler                                 |     |  |  |  |  |

| 1 Introduction                                           |     |  |  |  |  |

| 1.1 Problem Statement                                    |     |  |  |  |  |

| 1.2 Research Questions                                   |     |  |  |  |  |

| 1.3 Thesis Organization                                  |     |  |  |  |  |

| 2 A Brief Introduction to Spaceflight and Fault Toleran  | ice |  |  |  |  |

| Thesis Motivation and Legitimization                     |     |  |  |  |  |

| 2.1 Spacecraft and Satellite Miniaturization             |     |  |  |  |  |

| 2.2 Early CubeSat Reliability and Motivation             |     |  |  |  |  |

| 2.3 Nanosatellites Today and Legitimization              |     |  |  |  |  |

| 2.4 Fault-Tolerant Computer Architecture                 |     |  |  |  |  |

| 3 The Space Environment                                  |     |  |  |  |  |

| Physical Fault Profile and Operational Considerations    | s   |  |  |  |  |

| 3.1 The Impact of the Space Environment on Electronics   |     |  |  |  |  |

| 3.2 Technology Readiness and Standardization             |     |  |  |  |  |

| 3.3 Operational Constraints for Satellite Computers      |     |  |  |  |  |

|                                                          |     |  |  |  |  |

| A Fault Tolerance Architecture for Modern Semiconductors |     |  |  |  |  |

| $Stage \ 1 \ {\it \& Architecture \ Overview}$           |     |  |  |  |  |

| 4.1 Introduction                                         |     |  |  |  |  |

| 4.2 Related Work                                         |     |  |  |  |  |

| 4.3 Fault Tolerance through Software                     |     |  |  |  |  |

| 4.4 Stage 1: Short-Term Fault Mitigation                 |     |  |  |  |  |

| 4.5 Stage 2: MPSoC Reconfiguration & Repair              |     |  |  |  |  |

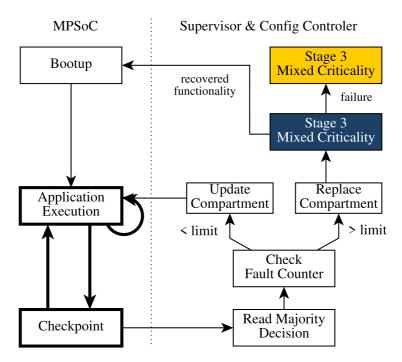

| 4.6 Stage 3: Applied Mixed Criticality                   |     |  |  |  |  |

| 4.7 Platform Architecture                                |     |  |  |  |  |

| 4.8 Discussions                                          |     |  |  |  |  |

| 4.9 Conclusions                                          |     |  |  |  |  |

| 4.10 Annex: Worst-Case Performance Estimation            |     |  |  |  |  |

| 5 MPSoC Management and Reconfiguration                   |     |  |  |  |  |

| Stage 2                                                  |     |  |  |  |  |

| 5.1 Introduction                                         |     |  |  |  |  |

ii CONTENTS

|   | 5.2          | Debugging and Reliability                                                                                                        | 75              |  |  |  |  |  |

|---|--------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|--|--|--|

|   | 5.3          | Implementation Details                                                                                                           | 76              |  |  |  |  |  |

|   | 5.4          | Use Cases beyond Debugging                                                                                                       | 82              |  |  |  |  |  |

|   | 5.5          | Discussions                                                                                                                      | 87              |  |  |  |  |  |

|   | 5.6          | Conclusions                                                                                                                      | 87              |  |  |  |  |  |

| • | 73 AT *      |                                                                                                                                  |                 |  |  |  |  |  |

| 6 |              | Mixed Criticality and Resource Pooling Stage $3$                                                                                 |                 |  |  |  |  |  |

|   | 6.1          | Introduction                                                                                                                     | <b>89</b><br>90 |  |  |  |  |  |

|   | 6.2          | Background                                                                                                                       | 90              |  |  |  |  |  |

|   | 6.3          | Related Work                                                                                                                     | 91              |  |  |  |  |  |

|   | 6.4          | System Overview & Requirements                                                                                                   | 92              |  |  |  |  |  |

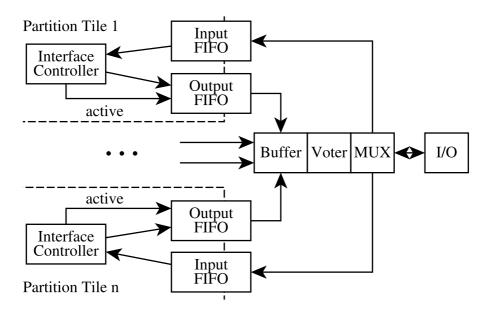

|   | 6.5          | System Architecture Review                                                                                                       | 94              |  |  |  |  |  |

|   | 6.6          | Spare Resource Pooling                                                                                                           | 97              |  |  |  |  |  |

|   | 6.7          | Adapting to Varying Mission Requirements                                                                                         | 98              |  |  |  |  |  |

|   | 6.8          | Discussions                                                                                                                      | 103             |  |  |  |  |  |

|   | 6.9          | Conclusions                                                                                                                      | 103             |  |  |  |  |  |

|   |              |                                                                                                                                  |                 |  |  |  |  |  |

| 7 |              | table Data Storage for Miniaturized Satellites  mory Fault Tolerance                                                             | 105             |  |  |  |  |  |

|   | 7.1          | Introduction                                                                                                                     | 106             |  |  |  |  |  |

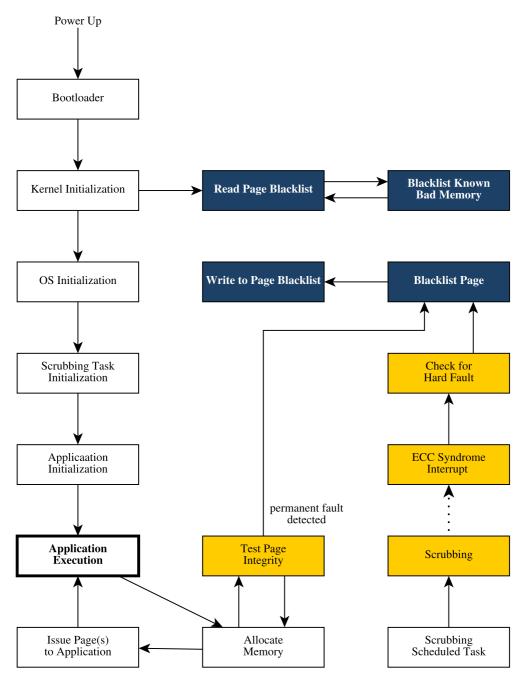

|   | 7.1          | Data Integrity as Foundation of Fault Tolerance                                                                                  | 107             |  |  |  |  |  |

|   | 7.2          | Volatile Memory Consistency                                                                                                      | 107             |  |  |  |  |  |

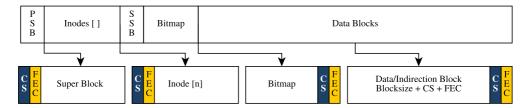

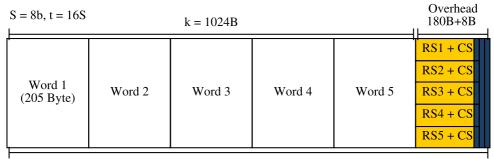

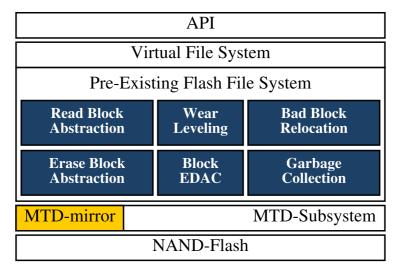

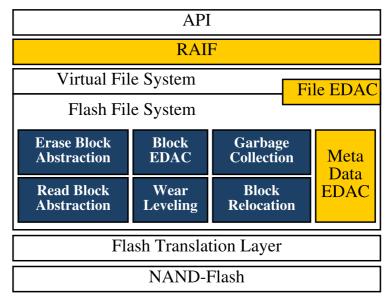

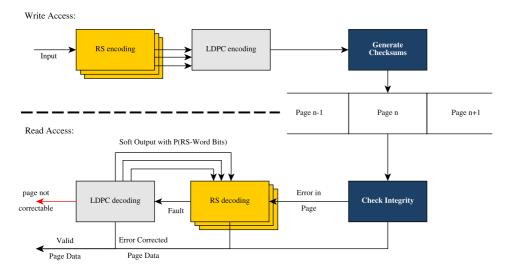

|   | 7.3          | A Radiation-Robust Filesystem for Space Use                                                                                      | 115             |  |  |  |  |  |

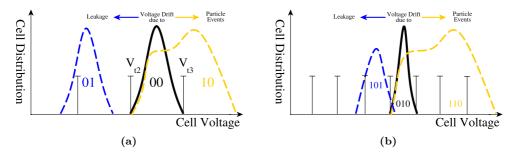

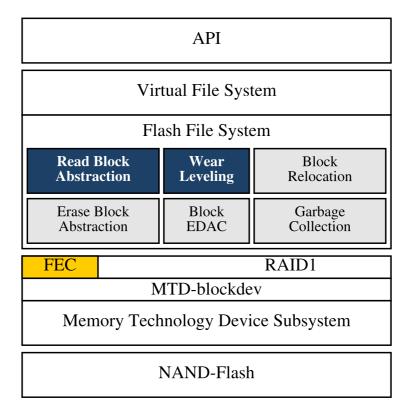

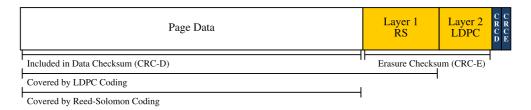

|   | $7.4 \\ 7.5$ | High-Performance Flash Memory Integrity                                                                                          | $113 \\ 122$    |  |  |  |  |  |

|   | 7.6          | Conclusions                                                                                                                      | 131             |  |  |  |  |  |

|   | 1.0          | Conclusions                                                                                                                      | 101             |  |  |  |  |  |

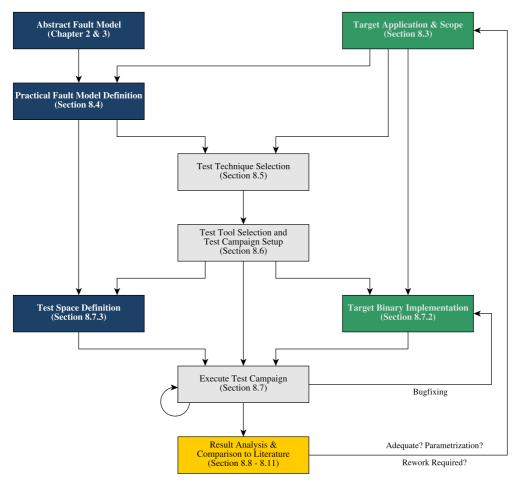

| 8 |              | Validating Software-Implemented Fault Tolerance                                                                                  |                 |  |  |  |  |  |

|   | -            | tematic Fault Injection                                                                                                          | 133             |  |  |  |  |  |

|   | 8.1          | Introduction                                                                                                                     | 134             |  |  |  |  |  |

|   | 8.2          | Related Work                                                                                                                     | 136             |  |  |  |  |  |

|   | 8.3          | Target Implementation                                                                                                            | 138             |  |  |  |  |  |

|   | 8.4          | Obtaining a Practical Fault Model                                                                                                | 139             |  |  |  |  |  |

|   | 8.5          | Suitable Fault-Injection Techniques                                                                                              | 140             |  |  |  |  |  |

|   | 8.6          | Test Campaign Setup                                                                                                              | 142             |  |  |  |  |  |

|   | 8.7          | Executing a Test Campaign                                                                                                        | 143             |  |  |  |  |  |

|   | 8.8          | Results & Interpretation                                                                                                         | 150             |  |  |  |  |  |

|   |              | ArchC MPSoC vs. FIES Result Comparison                                                                                           | 153             |  |  |  |  |  |

|   |              | Comparison to Literature                                                                                                         | 154             |  |  |  |  |  |

|   |              | Discussions                                                                                                                      | 155             |  |  |  |  |  |

|   | 8.12         | Conclusions                                                                                                                      | 157             |  |  |  |  |  |

| 9 |              | nbining Hardware and Software Fault Tolerance                                                                                    |                 |  |  |  |  |  |

|   | _            | h-Level System Design                                                                                                            | 159             |  |  |  |  |  |

|   | 9.1          | $Introduction \dots \dots$ | 160             |  |  |  |  |  |

|   | 9.2          | Background & Related Work                                                                                                        | 160             |  |  |  |  |  |

|   | 9.3          | A Hybrid Fault Tolerance Approach                                                                                                | 161             |  |  |  |  |  |

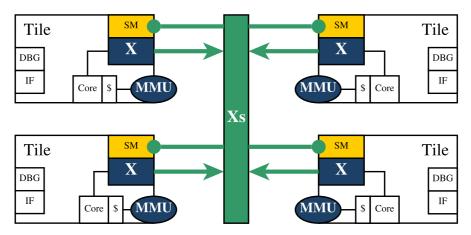

|   | 9.4          | The MPSoC Architecture                                                                                                           | 163             |  |  |  |  |  |

|   | 9.5          |                                                                                                                                  | 167             |  |  |  |  |  |

CONTENTS

|               | 9.6<br>9.7                                           | Implementation Considerations                                                                        | 169<br>170                                    |

|---------------|------------------------------------------------------|------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| 10            | Prac<br>10.1<br>10.2<br>10.3<br>10.4<br>10.5<br>10.6 | Board Computer Integration and MPSoC Implementation extical Design Verification on FPGA Introduction | 171<br>172<br>173<br>175<br>187<br>189<br>192 |

| 11            | $11.1 \\ 11.2$                                       | Clusions and Outlook Conclusions                                                                     | 195<br>195<br>197<br>199                      |

| Bil           | bliog                                                | raphy                                                                                                | 202                                           |

| Ne            | derla                                                | andse Samenvatting                                                                                   | 229                                           |

| 中,            | 文摘罗                                                  | ਜ਼ੁੱ<br>ਵ                                                                                            | 235                                           |

| 中             | 文摘罗                                                  | 要(繁體)                                                                                                | 239                                           |

| 日表            | 本語⊄                                                  | の要約                                                                                                  | 243                                           |

| $\mathbf{Re}$ | sum                                                  | en en Español                                                                                        | 247                                           |

| Pe            | зюм                                                  | е на Русском Языке                                                                                   | <b>253</b>                                    |

| En            | glish                                                | Summary                                                                                              | <b>25</b> 9                                   |

| Lis           | st of                                                | Selected Publications                                                                                | 263                                           |

| Cu            | ırricı                                               | ılum Vitae                                                                                           | 265                                           |

| Ac            | knov                                                 | vledgments                                                                                           | 269                                           |

vi CONTENTS

### Preface

#### Space: The Final Frontier

Humankind has been fascinated by the stars, and planets of our solar system, probably since before our species developed complex language. Many cultures have considered them to be ancestors, spirits of nature, and deities guiding our life and influencing our world. As humankind developed, people chose to see their heroes in the constellations, and these curious objects in the sky sometimes even were considered gods. Knowing what these gods wanted or liked could help a society prosper, or could doom it. Even more were we intrigued by the Sun, our neighboring planets, the Moon.

Technology has always been critical in our quest to understand our environment, and our world. Today, we are dependent upon the availability and correct functioning of our technology. It has enabled us to transform nature, but also to damage it and most likely change it for generations. And we are using technology even in our attempts to repair some of that same damage we inflict through it. Without technology, modern societies and our every day life would be unthinkable.

Humans are curious, and using our technology, we began exploring space just recently, considering the timescale of human existence. We operate vast telescopes on the ground and in space, which help us answer the most fundamental questions about how we came to be and where we are going. A few decades ago, we began launching satellites into space, which we today use for science, commerce, and education. Two superpowers conducted a great race to the Moon just a few decades ago, arrived there, took pictures, and then returned home. Today, this race is being rerun with more participants, resulting maybe in an extension to Mars, or better and more productively, to the Galilean Moons of Jupiter.

Satellites allow us to communicate with any point on the surface of the Earth in real-time, and with Mars with more than 10 minutes delay. Weather forecasts, communication services, flight information, and geolocation systems today are possible only due to information transmitted, or relayed by satellites. In many aspects, our modern life would be unimaginable without them.

We have outgrown our homeworld and its limited pool of resource already in many aspects, and most likely we even have to go to space to survive, like a young bird leaving its nest. Within the next few generations, we will reach out into space, begin to understand whatever we may find there, and utilize the vast resources which we may find within our solar system for the benefit of all. To design, construct, test, and operate the spacecraft that we will require we depend upon modern computer technology and electronics.

Electronics and semiconductor technology are indispensable in spacecraft design,

2 CONTENTS

and microprocessors can be found in all major satellite subsystems. Spacecraft and computers represent the peak of our technology, the application of all our skills in engineering, and the result of all the combined interdisciplinary scientific knowledge we have as a species. The reliability of these components is mission critical; and directly or indirectly, lives depend upon them, even in unmanned spaceflight. Scientists and engineers therefore seek to invent, develop, and utilize computer designs which can guarantee sufficient robustness and reliability for a space mission. The topic of this thesis is to enable the use of modern computer technology manufactured in fine technology nodes, which at the time of writing can not be used aboard spacecraft in a reliable manner.

## Chapter 1

### Introduction

#### Brief Abstract

Modern semiconductor technology has enabled the development of miniaturized satellites, which are cheap to launch, low-cost platforms for a broad variety of scientific and commercial instruments. Especially very small satellites (<100kg) can enable space missions which previously were technically infeasible, impractical or simply uneconomical. However, as discussed in Chapter 2, they suffer from low reliability. Especially the smallest such satellites are typically not considered suitable for critical and complex multi-phased missions, as well as for high-priority science missions for solar-system exploration and astronomical applications [1]. The on-board computer (OBC) and related electronics constitute a significant part of such spacecraft, and in related work, e.g., [2], were responsible for a majority of post-deployment failures, which are further discussed also in Chapter 3.

Indeed, the modern embedded and mobile-market semiconductors used aboard nanosatellites lack the fault tolerance (FT) capabilities of computer-architectures for larger spacecraft. Due to budget, energy, mass, and volume restrictions in miniaturized satellites, existing FT solutions developed for such larger spacecraft can not be adopted. Today, there exist no fault-tolerant computer architectures that could be used aboard nanosatellites powered by embedded and mobile-market semiconductors, without breaking the fundamental concept of a cheap, simple, energy-efficient, and light satellite that can be manufactured en-mass and launched at low cost [3].

To overcome this limitation, in this thesis, we develop a new approach to achieve fault tolerance for miniaturized satellite computers based upon modern semiconductors. The method we use to approach this challenge is to first consider protective measures proposed by science as theoretical concepts, as well as measures that are in use today in the space industry and other industries in Chapters 2, 3, and 4. We consider how these can be utilized to systematically protect each component of a spacecraft's OBC, as well as the software run on it.

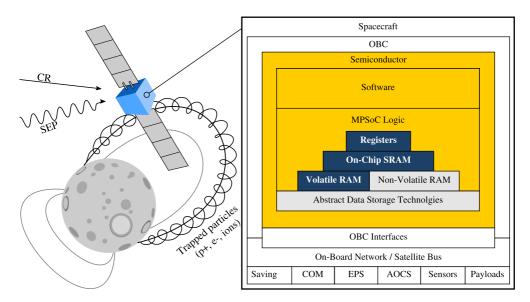

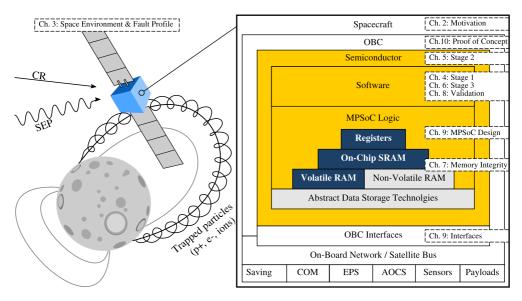

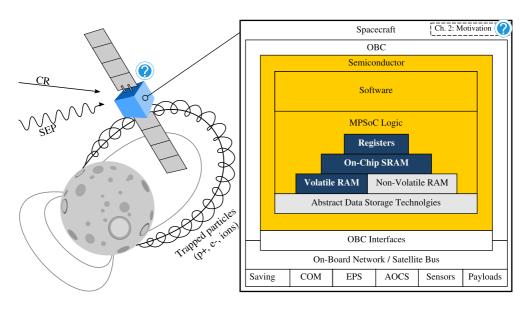

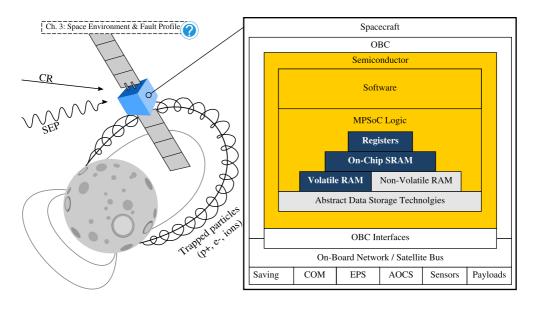

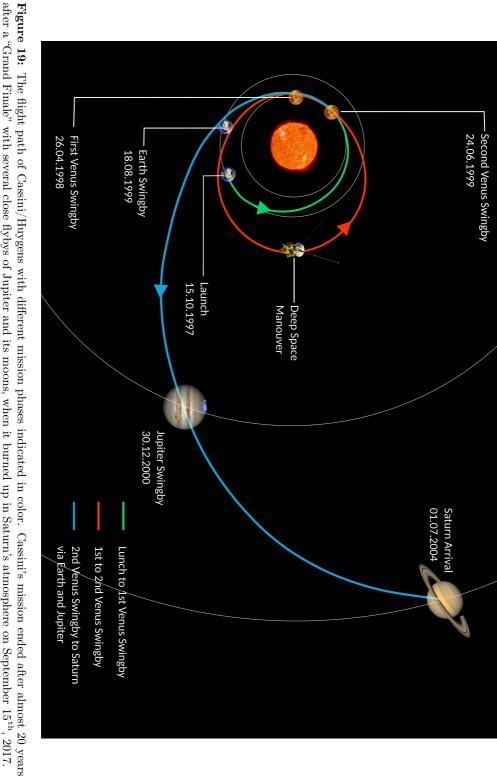

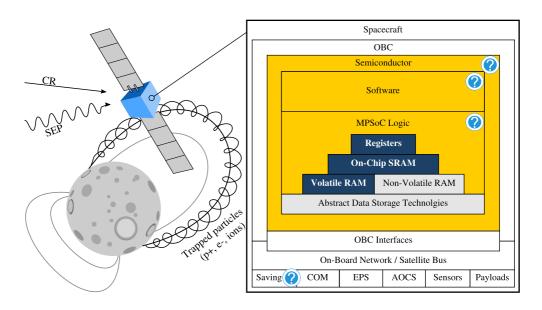

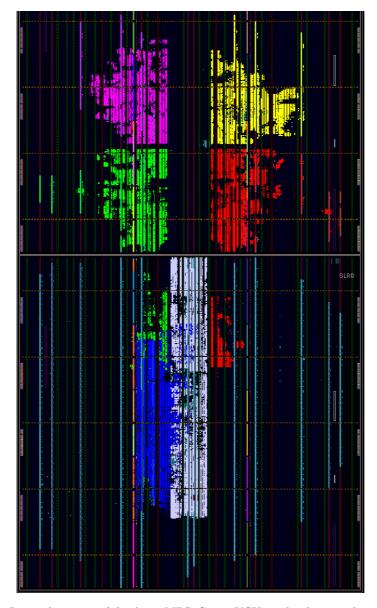

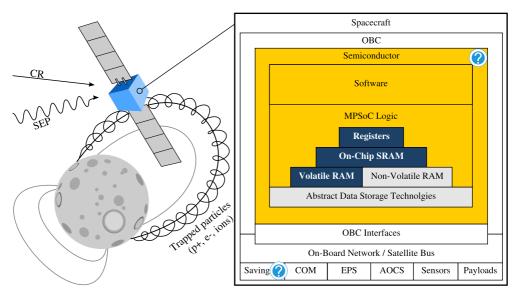

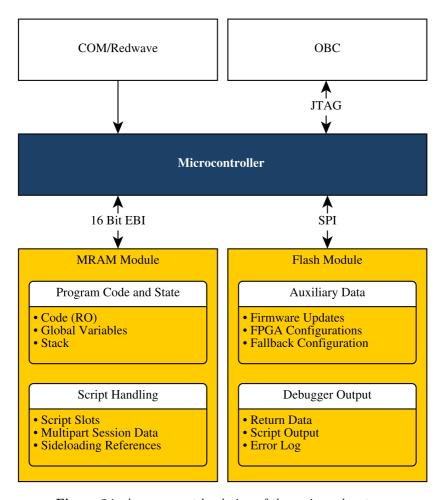

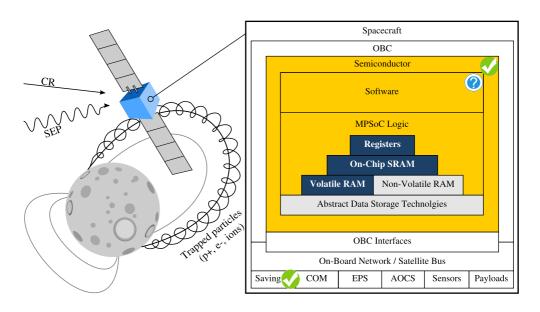

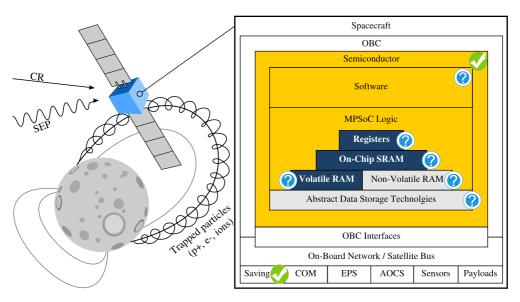

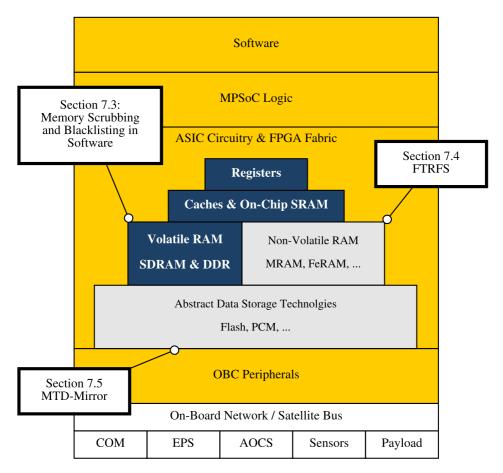

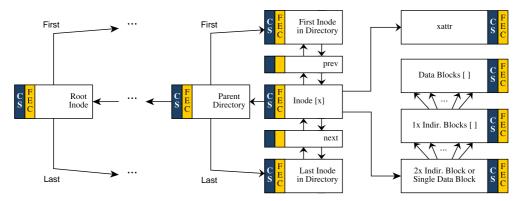

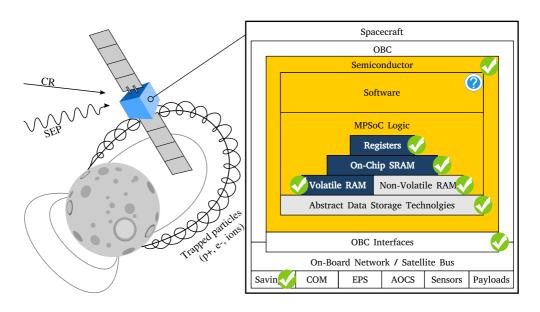

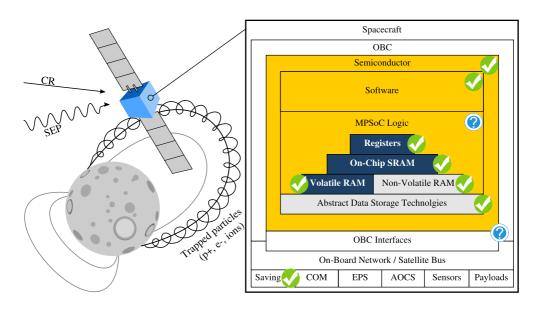

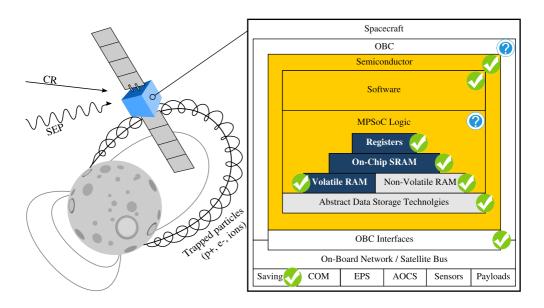

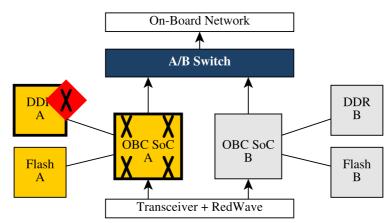

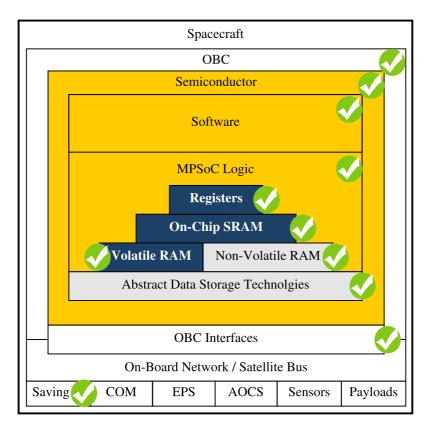

A high-level schematic of the components making up a satellite on-board computer is depicted in Figure 1. For each OBC component indicated in this figure, we develop fault tolerance measures that can be used to protect them and describe them in the different chapters of this thesis. To assure that these concepts are effective, we develop them specifically considering the application constraints and requirements of a

Figure 1: A high-level component model of an OBC, and the other subsystems within a satellite interacts with.

satellite operating in the space environment. Based on these concepts, we propose the hypothesis that fault tolerance can be achieved through hardware-software co-design, for which we produce a theoretical design in the form of a three-stage fault tolerance architecture.

We show that by systematically protecting critical key-component of the OBC using software measures, synergies between different fault tolerance measures can be achieved. These synergies enable us to protect the system as a whole more effectively, efficiently and in a way that is economical and feasible even for small-scale professional CubeSat developers and academic teams working on scientific spacecraft and instruments with a limited project budget. We test our hypothesis through fault-injection and provide statistics on the results, and implement a proof-of-concept for this system architecture in a reconfigurable logic device (FPGA).

Our ultimate objective is to allow a suitable miniaturized satellite design to reliably achieve a minimum of 2 years of on-orbit operation. At the time of writing, miniaturized satellite computer components do not include sophisticated fault tolerance capabilities, and may fail at any point in time during a space mission. In contrast to large spacecraft, they therefore can not be designed to achieve a specific mission lifetime, but designs function as long as no critical faults occur. Therefore, these missions are kept brief, as is further discussed in Chapters 2 and 3, thus implying risk acceptance instead of risk mitigation and risk handling.

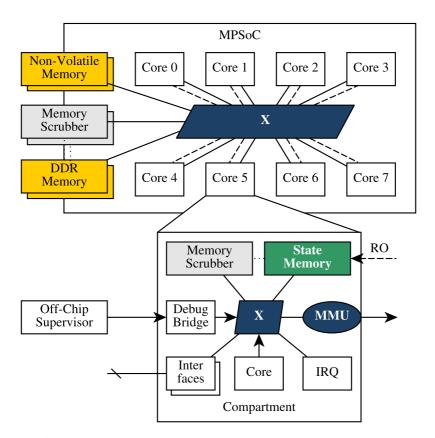

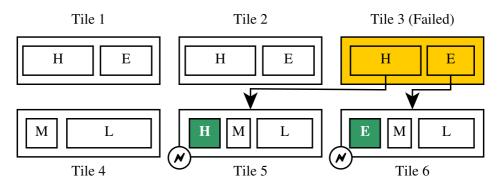

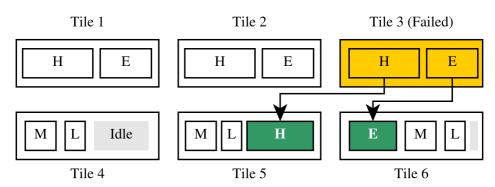

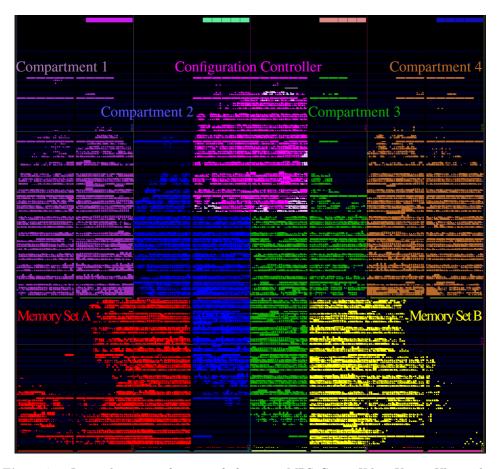

We realize fault tolerance in software and assure an on-board computer's long-term robustness by exploiting partial FPGA-reconfiguration (see Chapter 5) and mixed criticality aspects (see Chapter 6), and develop a multiprocessor System-on-Chip (MP-SoC) architecture through hardware-software co-design (see Chapter 4). Hence, this computer architecture also provides spacecraft designers with the capabilities necessary to achieve a given mission lifetime by adjusting our architecture's parameters, such as the necessary level of replication of software run on the system, provisioning

CHAPTER 1 5

of spares, scrubbing periods, and error correction coding strength.

The MPSoC requires no custom-written IP-cores (library logic) and can be assembled from well tested commercial-off-the-shelf (COTS) components, and powerful embedded and mobile-market processor cores, yielding a non-proprietary, and open system architecture. The resulting computer architecture consists only of conventional consumer-grade hardware, commodity processor cores, standard parts, and openly available standard library IP.

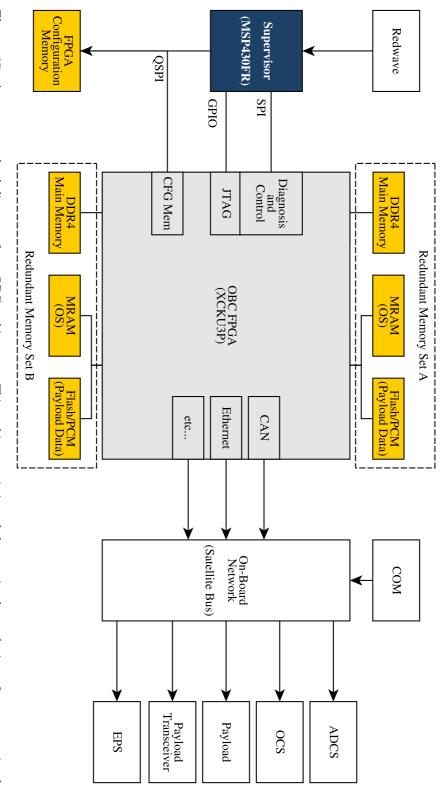

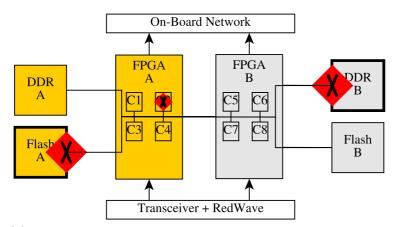

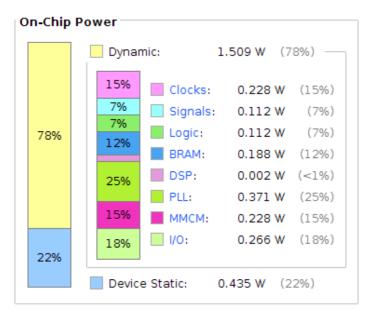

In the final chapter of this thesis, we provide a proof-of-concept implementation of this MPSoC for three FPGAs, the Xilinx Kintex Ultrascale+ KU3P (the smallest of its class), KU11P, and the Xilinx Kintex Ultrascale KU60. Our implementation for KU3P requires only 1.94W total power consumption, which is well within the power budget range achievable aboard 2U CubeSats. To our understanding, this is the first scalable and COTS-based, widely reproducible OBC solution which can offer strong fault tolerance even for 2U CubeSats.

#### 1.1 Problem Statement

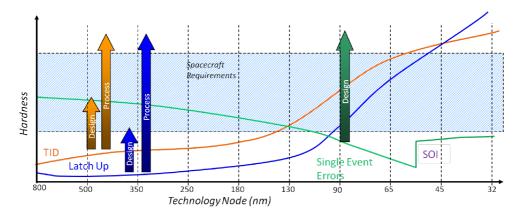

Hardware-based fault tolerance measures for large satellites are effective for older, large-feature-size technology nodes which have fallen out of use in the mobile-market and the IT industry decades ago [4]. Modern mobile-market COTS processors depend upon manufacturing in low-feature size technology nodes, and can not be manufactured anymore using old technology nodes. Traditional hardware-implemented fault tolerance techniques diminish in effectiveness and efficiency with shrinking feature size [5]. This has left a protective gap due to a lack of fault-tolerant solutions, and the reliability of such miniaturized satellites is insufficient for critical missions, which is further discussed in Chapter 3.

Countless novel academic fault tolerance concepts have been proposed over the years, which, in theory, could be used to protect modern computer systems. But at the time of writing, there is a significant gap between fault tolerance research, and its applications to spacecraft of all classes, as discussed as part of related work in Chapters 4, 6, and 8. Many of the concepts mentioned there have low technological maturity and do not meet practical application constraints for a use within a real computer system, regardless of the intended operating environment [1]. Software-implemented fault tolerance concepts have thus until today been ignored by the space industry due to lacking maturity, perceived complexity, doubts about their effectiveness and testability [1].

In this thesis we therefore explore how fault tolerance can be achieved for computer systems manufactured in state-of-the-art technology nodes with low power-usage, and small feature-size through scientific means. We do this in collaboration with the European Space Agency, supported by a Networking Partnership Program grant. In this thesis we address the following problem:

RQ0 Can a fault tolerance computer architecture be achieved with modern embedded and mobile-market technology, without breaking the mass, size, complexity, and budget constraints of miniaturized satellite applications?

#### 1.2 Research Questions

To show that it is indeed possible to address the problem stated in RQ0 in an affirmative way, we develop a fault-tolerant system architecture which can do exactly that. Systematically for each component in a satellite's on-board computer, we develop specific measures to address challenges regarding fault tolerance. These components are also depicted in Figure 1. However, we do not try to apply fault tolerance everywhere in the system as, as this would inflate system complexity and fault potential. Instead, we place fault tolerance measures strategically within the system to handle and cover faults where these can be addressed best at a system level.

In this thesis, we investigate the following research questions throughout the different chapters:

- RQ1 Considering the design constraints of nanosatellites, can a fault-tolerant computer architecture be achieved with COTS components?

(Chapter 4)

- RQ2 How can the correct functionality of a CubeSat's FPGA-based on-board computer be assured and verified, and its lifetime extended?

(Chapter 5)

- RQ3 Can a satellite computer architecture enable novel functionality for a satellite computer, that improves satellite computing beyond just offering better fault tolerance and an increased lifetime?

(Chapter 6)

- RQ4 Can commercial memories be retrofitted with error detection and correction in software, to substitute for hardware measures, and to what extent? (Chapter 7)

- RQ5 How can its software-implemented fault tolerance measures of a hardware-software hybrid architecture be tested and validated?

(Chapter 8)

- RQ6 Can such a computer architecture be practically implemented within the size, energy, and budget constraints of nanosatellite applications? (Chapters 9 & 10)

These questions are discussed in this thesis. To do so, we develop a fault-tolerant computer architecture for irradiated environments which can offer protection for on-board computer systems based upon modern semiconductors. Through implementation, testing via fault-injection, and the construction of a proof-of-concept implementation on FPGA, we show that this approach is technically feasible with contemporary technology.

The key contribution of this thesis is a computing concept that can allow future critical commercial and high-priority science missions to be done at low cost, to enable REAL progress in satellite miniaturization to take us as a species to the stars. My hope is that this thesis is the beginning of something new and significant, and in the coming years I plan to advance this technology from its current proof-of-concept state to maturity. To do so, radiation testing, long-term testing, as well as on-orbit demonstration aboard a CubeSat will be necessary.

CHAPTER 1 7

Figure 2: Chapter guide for this thesis.

#### 1.3 Thesis Organization

A brief outline of the subsequent chapters follows, with a visual chapter guide depicted in Figure 2.

## Chapter 2: A Brief Introduction to Spaceflight and Fault Tolerance

The research upon which this thesis is based is interdisciplinary. It relies upon concepts and results from several different fields, including computer engineering, nuclear science, electrical engineering, physics and astronomy, as well as space engineering. In this chapter, we provide a brief introduction to our application, its design constraints, as well as fault-tolerant computer architecture. We further provide an overview over the current status of small satellite space missions, as well as a review on satellite failures in the past and at the time of writing. This chapter therefore serves also as motivation and legitimization for our research, including mission success and failure statistics, which underline the lack of reliability of very small satellites today.

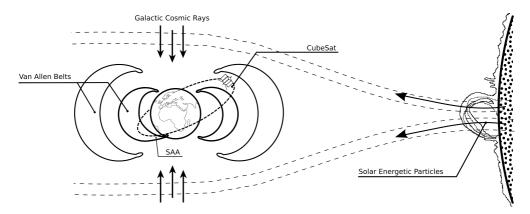

#### Chapter 3: The Space Environment

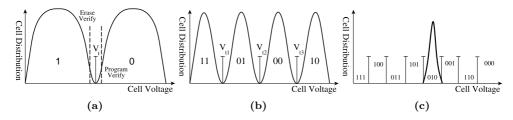

A satellite's on-board computer has to cope with unique challenges, requiring a general understanding of the physical effects of a spacecraft's operating environment. Hence, for the understanding of the fault profile and application constraints for this thesis, in this chapter we provide an in-depth discussion of the space environment and its effects. We discuss the physical design restrictions aboard spacecraft, and operational considerations. Most importantly we discuss the impact of radiation on semiconductors, and how it can be mitigated.

#### Chapter 4: A Fault Tolerance Architecture for Modern Semiconductors

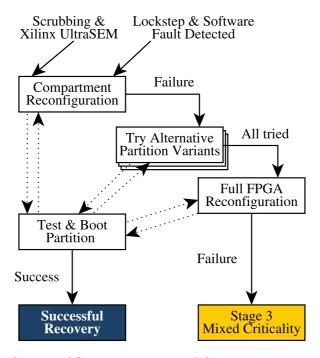

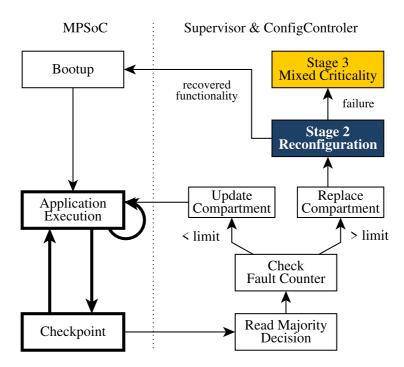

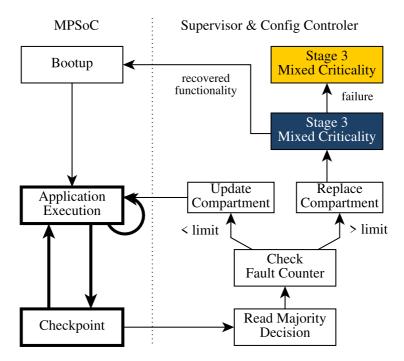

In this chapter, we describe a non-intrusive, integral, flexible, hardware-software-hybrid approach which enable the use of modern MPSoCs for spaceflight meeting real-world constraints. Neither traditional hardware- nor software-based FT solutions can offer the functionality necessary to guarantee fault tolerance for state-of-the-art SoCs used in miniaturized satellite OBCs. We achieve fault-detection, isolation and recovery through the use of a co-designed fault tolerance architecture consisting of multiple interlinked protective measures. In combination, they form a fault tolerance architecture which can guarantee strong fault coverage even during space missions with a long duration, for which we provide an early proof-of-concept implementation. The research in this chapter was published in the proceedings of the *IEEE Asian Test Symposium (ATS)* [Fuchs9].

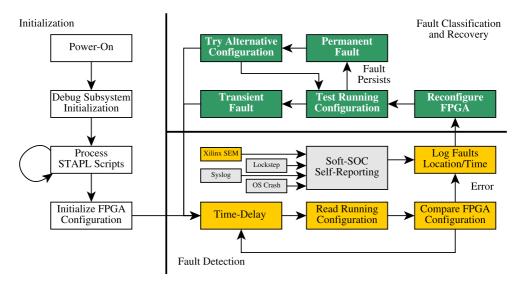

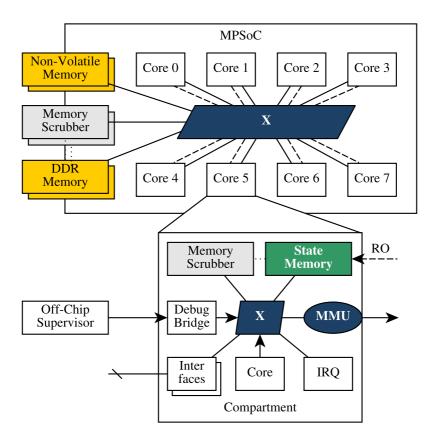

#### Chapter 5: MPSoC Management and Reconfiguration

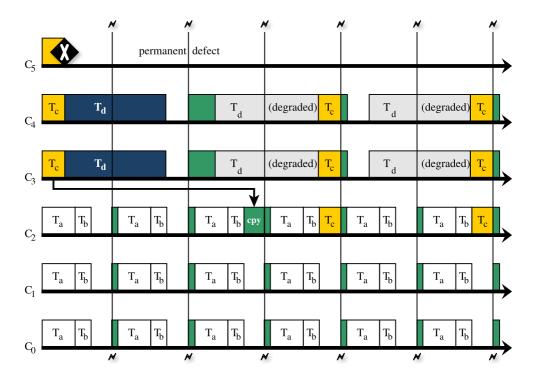

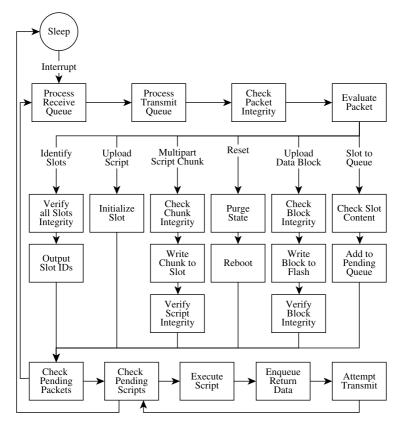

In this chapter, we present the concept and proof-of-concept implementation of a subsystem for autonomous chip-level debugging within a CubeSat via JTAG [6]. This concept provides all the necessary functionality needed to implement Stage 2 of the fault tolerance architecture described in Chapter 4. In our multi-stage fault tolerance architecture, remote debugging is one of several tasks this subsystem performs: It is now used to control the coarse-grain lockstep implemented within an MPSoC, and referred to as supervisor in remainder of this thesis. It interacts with an on-chip configuration controller to control partial reconfiguration and error scrubbing for the FPGA's fabric via the internal configuration access port (Xilinx's ICAP). An early version of this chapter was presented in the proceedings of the International Conference on Architecture of Computing Systems (ARCS) [Fuchs11], and an extended paper [Fuchs10] was published in the proceedings of the ESA/CNES Small Satellites, System & Services Symposium (4S).

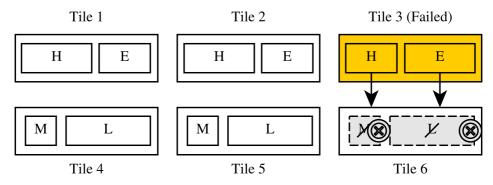

#### Chapter 6: Mixed Criticality and Resource Pooling

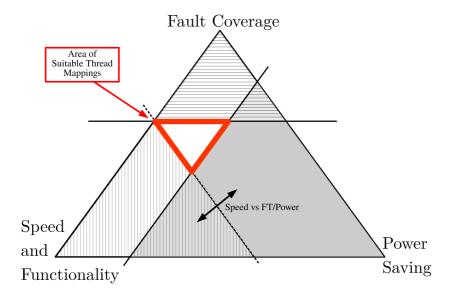

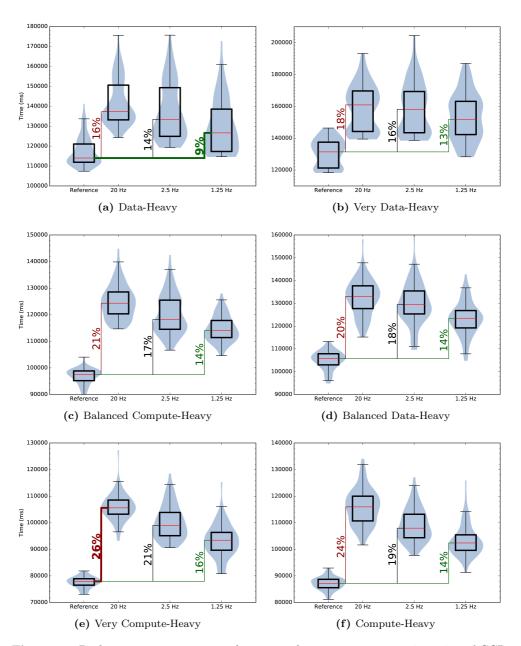

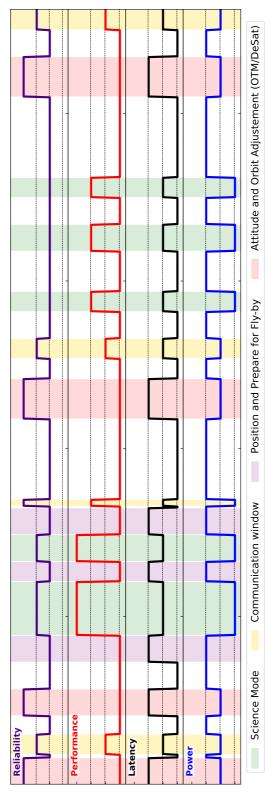

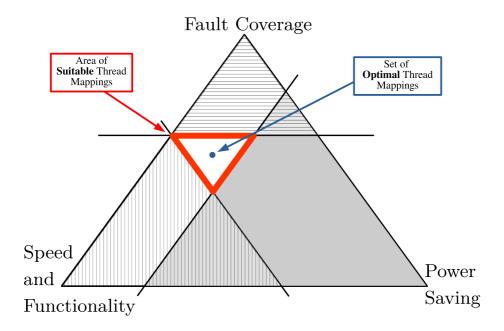

In this chapter, we discuss Stage 3 of our multi-stage fault tolerance architecture, and the advantages it offers not just for miniaturized satellites, but for spacecraft of all weight classes. Our architecture allows a satellite to dynamically adjust the fault tolerance level, compute performance, and energy consumption to meet the varying performance requirements to a satellite computer during long and multi-phased space missions. The operator of a spacecraft can prioritize between processing performance, functionality, fault coverage, and energy consumption. The system can be autonomously adapted to the OBC's thread assignment to retain a functional system core by sacrificing performance or availability of less critical applications. This allows an OBC to to more efficiently handle accumulating permanent faults and to age gracefully. The research in this chapter was published [Fuchs7] in the proceedings of the NASA/ESA Conference on Adaptive Hardware and Systems (AHS).

CHAPTER 1 9

#### Chapter 7: Reliable Data Storage for Miniaturized Satellites

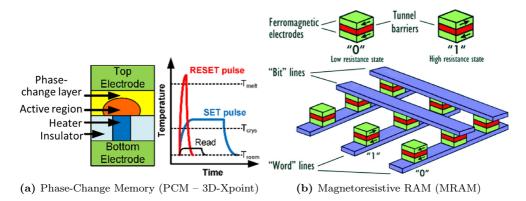

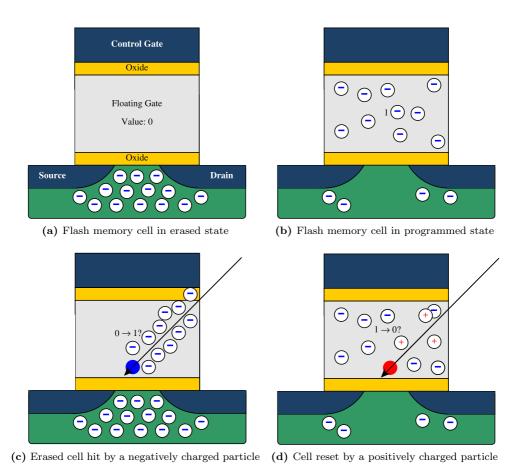

Reliable operation of an OBC can only be guaranteed if the integrity of the OBC's operating system, applications, as well as payload data can be safeguarded. Chapter 7 is therefore dedicated to discussing fault tolerance for the various volatile and nonvolatile memories used aboard miniaturized satellites and within our architecture. The research presented in this chapter was published as finalist paper [Fuchs15] in the proceedings of the AIAA/USU Conference on Small Satellites (SmallSat). It was awarded second place and a research grant in the Annual Frank J. Redd Student Competition. We describe the implementation of FTRFS, a fault-tolerant radiation-robust filesystem for space use. It was published [Fuchs18] in the proceedings of the International Conference on Architecture of Computing Systems (ARCS). Furthermore, a protective concept for flash memory and phase change memory is described in the second part of this chapter. It was published [Fuchs16] in the proceedings of the International Space System Engineering Conference Data Systems In Aerospace (DASIA).

#### Chapter 8: Validating Software-Implemented Fault Tolerance

In this chapter, we test and validate the software-mechanisms that are the foundation of our fault tolerance architecture by injecting faults into an RTEMS implementation of Stage 1. Traditional computer architectures for space applications are validated using system-level testing. This is viable for systems relying on hardware measures, but unsuitable for testing software due to a lack of test coverage and the expanded test-space. For testing software-based FT measures, a realistic test-setup is considered good practice and required to deliver representative fault-injection results. Therefore, a fault-injection campaign was conducted using system emulation through QEMU into a representative ARMv7a-SoC matching our architecture target, ARM's Cortex-A53, and into a RISC-V-based SystemC-model. Our results show that our lockstep implementation is effective and efficient, and we provide a direct comparison to related work. An early version of this chapter was published in the proceedings of the *IEEE Asian Test Symposium (ATS)* [Fuchs5].

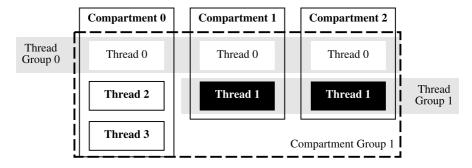

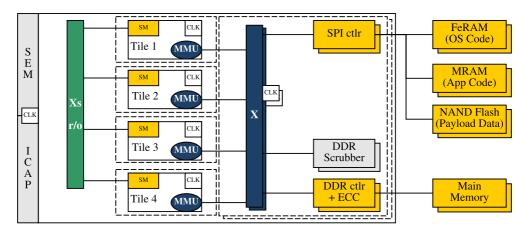

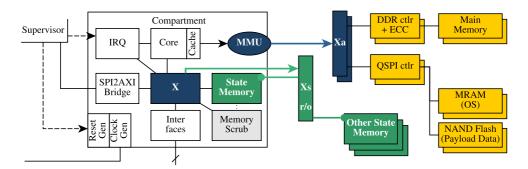

#### Chapter 9: Combining Hardware and Software Fault Tolerance

As optimal platform for our architecture, we developed a compartmentalized MPSoC design for FPGA, where Stage 2's partial reconfiguration functionality can be utilized to recover defective parts of the MPSoC. This architecture is designed to satisfy the high performance requirements of current and future scientific and commercial space missions at very low cost, while offering the strong fault coverage guarantees necessary for missions with a long duration. We describe the topology of our multiprocessor System-on-Chip (MPSoC), and show how it can be assembled in its entirety from only well tested COTS components with commodity processor cores. The MPSoC can be implemented using only COTS hardware and extensively validated library IP, requiring no custom logic or space-proprietary processor cores. The research in this chapter was published [Fuchs6] in the proceedings of the IEEE Conference on Radiation and Its Effects on Components and Systems (RADECS).

## Chapter 10: On-Board Computer Integration and MPSoC Implementation

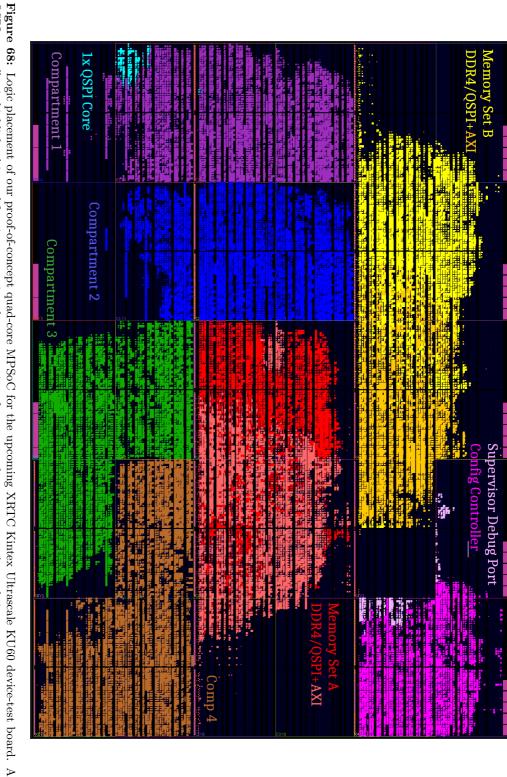

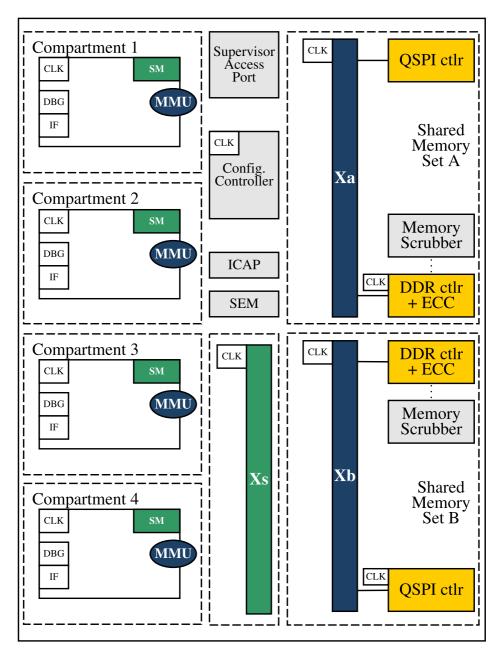

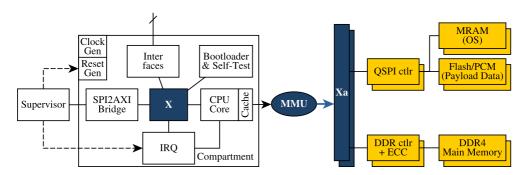

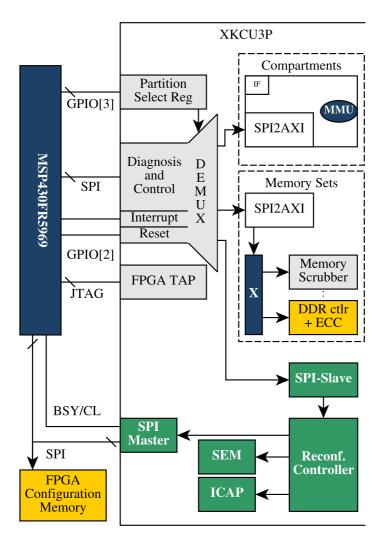

In the final research chapter of this thesis, we discuss practical implementation results for our MPSoC design. We provide detailed resource utilization results for this MPSoC for 3 different FPGAs: Xilinx Kintex Ultrascale+ KU3P (the smallest of its class), KU11P, and the Xilinx Kintex Ultrascale KU60, for which we are collaborating within the Xilinx Radiation Testing Consortium to achieve a suitable device-test platform for radiation testing in the future. We provide statistics on power consumption, and show that even between two FPGA generations power consumption can be reduced drastically through the use of more modern and efficient technology nodes. This serves as proof-of-concept for our architecture. This chapter is based on two publications [Fuchs1,Fuchs2] in the proceedings of to the IEEE International Symposium on Defect and Fault Tolerance in VLSI and Nanotechnology Systems (DFT) and the AIAA/USU Conference on Small Satellites (SmallSat).

## Chapter 2

# A Brief Introduction to Spaceflight and Fault Tolerance

#### Thesis Motivation and Legitimization

The research upon which this thesis is based does not come from one single field of science, but is interdisciplinary. It relies upon concepts and results from several different fields, including computer engineering, nuclear science, electrical engineering, physics and astronomy, as well as space engineering. In this chapter, we provide a brief and informal introduction to our application, its design constraints, as well as fault-tolerant computer architecture. We further provide an overview over the current status of small satellite space missions, as well as a review on satellite failures in the past and at the time of writing. This chapter therefore serves also as motivation and legitimization for our research, including mission success and failure statistics, which underline the lack of reliability of very small satellites today.

#### 2.1 Spacecraft and Satellite Miniaturization

In this section, a brief introduction into the different kinds of satellites and satellite miniaturization itself is given, to provide general understanding for readers who are not familiar with this field. This section is meant as to give sufficient background information on the application for the research discussed in this thesis.

Satellites can be differentiated by mass in several classes. When thinking of space stations, satellites, and deep-space probes, we usually imagine large structures floating in space, weighing multiple tons, powered by vast solar panel arrays, radioisotope thermoelectric generators, or fission reactors [7]. Certainly, many early scientific, commercial, and military satellites were very large spacecraft. These are sometimes designed to operate for several decades in space. However, today, modern semiconductor technology, more efficient battery and photovoltaics, novel propulsion technologies, and robust lightweight materials enable the construction of much smaller, lighter, and cheaper spacecraft.

Spacecraft with a wet mass<sup>1</sup> of less than 500kg are therefore referred to as "miniaturized satellites", and can be constructed dramatically faster than large satellites. In Table 1, an overview over satellite classes and capabilities is given.

At the time of writing, several companies have achieved commercial success by operating large groups of miniaturized satellites in orbit. They have been successfully used to providing real-time earth observation data and help in disaster recovery [8], and in safety- and life-critical services [9] such as airplane traffic tracking and maritime shipping [10]. A broad variety of biological and chemical experiments [11] has been carried out using CubeSat platforms, which are also rather popular for testing and validating novel technologies in space [12, 13]. Several pico- and nanosatellite-based space-observatories [14, 15] have been launched, and nanosatellites were deployed by the Hayabusa 2 space probe at the asteroid 162173 Ryugu [16]. In 2018, 2 interplanetary CubeSats traveled to the planet Mars as part of the MarCO mission [17],

| <sup>1</sup> The mass of the spacecraft including payload and all consumables such as |

|---------------------------------------------------------------------------------------|

|---------------------------------------------------------------------------------------|

|        | Weight |       | Minia-  | Build as    | Classical   | Propulsion | Mission  |

|--------|--------|-------|---------|-------------|-------------|------------|----------|

| Class  | Max    | Min   | turized | CubeSat     | Tech Usable | Available  | Lengths  |

| Large  | -      | 1t    | No      | Absurd      | Yes         | Yes        | Decades  |

| Medium | 1t     | 500kg | No      | Absurd      | Yes         | Yes        | Decades  |

| Small  | 500kg  | 100kg | Yes     | Limiting    | Most        | Yes        | 10 years |

| Micro  | 100kg  | 10kg  | Yes     | Common      | Little      | Yes        | years    |

| Nano   | 10kg   | 1kg   | Yes     | Standard    | No          | Yes        | 1 year   |

| Picro  | 1kg    | 100g  | Yes     | Standard    | No          | Limited    | months   |

| Femto  | 100g   | -     | Yes     | Inefficient | No          | No         | -        |

**Table 1:** Satellites can be classified in a variety of ways, with each type of spacecraft having different capabilities, technological limitations, and the capability to achieve different mission durations. In principle, almost any satellite could be manufactured to be a CubeSat, but only for some this makes sense due to the constraints of this form factor standard.

CHAPTER 2

providing real-time telemetry during the arrival-phase of NASA's InSight Mars Lander. Several miniaturized satellite constellations for technology demonstration, and Earth observation, and positioning, and data relay purposes have been developed [18–21] and launched [8, 22, 23]. At the time of writing, scientists and engineers have even begun to develop CubeSat-based interferometers and composite space telescopes [13] that could outperform even the largest conventional space-observatories, and there are plan to use Nanosatellites even for gravitational-wave measurement [15].

#### 2.1.1 Large Satellites based on Traditional Design Principles

Satellites with a wet mass above 500kg are at this point in time constructed in large projects with vast budgets quasi artisanally. Most "big-space" applications rely upon such satellites. Satellites of 500kg – 1000k are usually classified as medium-sized satellites, heavier spacecraft are designated as a large satellites. Development of such satellites is challenging, system architectures are complex, resulting in long development times, and the need to utilize well tested, proven technology, that is available over a very long period of time. This technology is usually space industry proprietary. Technology readiness, design maturity, and space heritage of a technology through prior use aboard other spacecraft are essential, and often seen a prerequisite for considering a technology for use within this satellite class.

Construction of these satellites in practice often takes many years [24], sometimes even decades [25]. To provide an example, the James Webb Space Telescope (JWST) is designed to have a wet mass of approximately 6620kg. It is a multinational project involving hundreds of stakeholders, and has been in construction for more than 25 years at the time of writing, and its precise date of completion and launch has not been announced yet. The cost of the electronics used aboard such a spacecraft is small compared to the funds required to meet legal requirements, for salaries, tooling, testing, management, certification, insurance, and launch. Spacecraft testing also requires access to specialized facilities [26, 27] including:

- thermal/vacuum chambers to analyze the behavior of the spacecraft in a space-like environment at high or low temperatures (often 173K and 373K) [28],

- radiation testing facilities using radiogenic sources or particle accelerator to simulate the radiation environment a satellite's components have to operate in, and to verify their correct behavior and, if available, effectiveness of fault tolerance measures, and

- a broad variety of other heavy machinery, e.g., to perform mechanical stress and vibration tests.

Most modern major launch vehicles can carry much heavier and bulkier loads than just one satellite [29, 30]. Often a substantial amount of volume and mass remains available which in the early days of spaceflight remained vacant to not endanger the primary payload [31]. To reduce costs, organizations often either sell this excess capacity, or hand the entire launch process over to a "launch broker", which then can combine multiple satellite launches into one "ride-share" launch [29]. An example of a ride-share launch with multiple satellites of various classes is depicted in Figure 3. The main spacecraft launched on a launch vehicle is then referred to as "primary payload", with other, often smaller satellites becoming "secondary payloads". Today

**Figure 3:** A ride-share satellite launch with the Earth observation SmallSat DubaiSat-2 (top center) being the primary payload. Secondary payloads were 4 microsatellites (top left and right, 2 bottom center) and 26 other nanosatellites which are located in the blue deployer boxes. The CubeSat First-MOVE (see Section 2.1.4) is located in the top right deployer.

Image copyright: C. Olthoff at al., Yasny Launch Base, Russian Federation, usage and reprint permissions granted.

even small start-up companies, and universities can bring their spacecraft into orbit at comparably low cost.

#### 2.1.2 Small Satellites

SmallSats, or Minisatellites, weigh between 500 and 100kg, and traditionally were used for brief science and commercial missions. Historically, SmallSat missions used to be shorter than those realized with large satellites [32]. They can be constructed and launched at drastically lower cost, and in general also more quickly. The term SmallSat is colloquially also used to refer to all satellites lighter than 500kg in this field. Due to technological evolution in recent decades, the capabilities of the SmallSats have increased, and today they increasingly much replace larger satellites.

#### 2.1.3 Microsatellites

MicroSats between 100kg and 10kg are today widely used for a variety of low cost commercial and novel scientific missions. The upper and lower boundaries between Nanosatellites, MicroSats, and SmallSats are fluent. MicroSats with a wet mass approaching 100kg differ little from lighter SmallSats, and usually carry fewer or lighter payloads and lighter components (e.g., smaller batteries, lighter and smaller solar cell array structures, ...) [33]. Light MicroSats become similar to a Nanosatellite and may even utilize Nanosatellite form factor standards, while larger ones can offer very similar capabilities to SmallSats. Many missions that a few decades ago required SmallSats can today be performed by MicroSats, which can be manufactured more rapidly and

CHAPTER 2 15

launched at lower cost. Compare also [34] for a market assessment for a corporate view on this increasing down-scaling trend.

#### 2.1.4 Nanosatellites and CubeSats

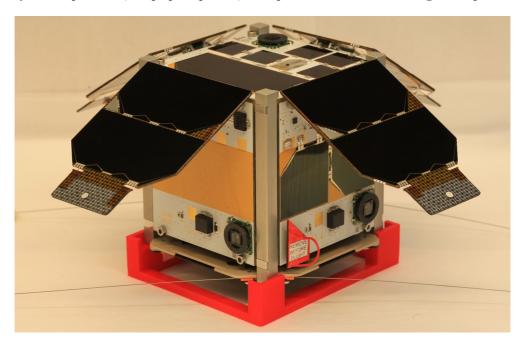

Nanosatellites weigh between 1 and 10kg and became popular for educational projects, especially due to the CubeSat standard. The CubeSat standard was originally intended to cheaply launch student projects into space at the beginning of the 21st century [35]. Today, it has become the standard form factor for Micro-, Nano-, and Picosatellites, and an example of a CubeSat is depicted in Figure 5. It requires a satellite to conform to certain design restrictions, e.g., banning the use of explosive substances within the satellite, and otherwise implies a stackable standard form-factor consisting of 10x10x10cm CubeSat units (U) and a maximum of 1.33 kg per 1U. CubeSats are designed to fit a standardized CubeSat deployer. Figure 4 depicts such a deployer consisting of a spring, and electric latch, which once the latch is released allows CubeSats to be safely be deployed by pushing them out of the box. This enables even heavy 12U or 24U designs (3x2x2 or 4x2x3U stacked) to be launched at reduced cost, and allows testing requirements to be reduced for launch qualification, as the failure of a CubeSat during launch will not interfere with the deployment of other satellites aboard the same launcher.

At the time of creation of the CubeSat standard, nanosatellites were intended to perform only simple and short missions in Low Earth Orbit (LEO), e.g., student education, or on-orbit concept validation. They rely on cheap commodity technologies and COTS components, such as lithium-polymer based batteries, and solar-cells intended for ground use. However, due to the rapidly increasing performance of embedded

Figure 4: A 3U-CubeSat deployer holding First-MOVE (right), and two other 1U CubeSats.

Image copyright: C. Olthoff at al., Yasny Launch Base, Russian Federation, usage and reprint permissions granted.

Figure 5: The 1U-CubeSat First-MOVE.

and mobile-market hardware since the early 2000s, the capabilities of nanosatellites have evolved considerably. At the time of writing, a diverse ecosystem of ready-to-use CubeSat components has developed. A variety of commercial companies of varying technical capabilities provide a customizable solutions of mixed quality, with ample launch opportunities into different orbits being available for 1–12U CubeSats.

The CubeSat First-MOVE (depicted in Figure 5) was one of these educational projects [36]. In 2013, I joined a research group developing this satellite at Technical University Munich, Germany, as a master student. Like many other first-generation educational CubeSats, First-MOVE was designed, constructed, and tested primarily by university students at the PhD, Master, and Bachelor levels. Planning of the First-MOVE mission began in 2006, a time when modern smartphones had just arrived in the consumer market, and construction in earnest began around 2010. It was launched into LEO on November 21<sup>st</sup>, 2013, and its malfunction, which is further described in Section 2.2, was the origin of the author's research on satellite fault tolerance.

#### 2.1.5 Picosatellites and PocketQubes

PicoSats range in weight from between 0.1 to 1kg, and are today used for education or very brief proof-of-concepts. The PocketQube form factor and many 1U CubeSats fall into this category, and the electrical architecture of such PicoSats is often similar or even identical to that of light Nanosatellites. The main difference is lower mechanical complexity, and a further constrained power budget due to reduced solar cell surface (often ranging around or below 5W). In practice, this implies limitations especially for transceivers and payload, which are the main power consumers aboard modern miniaturized spacecraft.

CHAPTER 2 17

#### 2.1.6 Femtosatellites

FemtoSats are the smallest miniaturized satellite form factor and weigh less than 0.1kg. The concept of FemtoSats was theoretical until recently without allowing productive satellite designs that can take a productive role in a space mission. However, in the 2010s, first proof-of-concepts and practical applications have emerged [37]. FemtoSats usually consist of a single PCB using wireless energy harvesting or carrying a single solar cell on one side of the PCB, and electronics on the other [38]. With the emergence of more advanced energy harvesting and battery technologies in the future and an increasing level of semiconductor miniaturization, the basic character of FemtoSats could therefore change. Future FemtoSats will therefore find new niche use-cases, for which these lightest, cheapest, and expendable spacecraft will be optimal.

#### 2.2 Early CubeSat Reliability and Motivation

Miniaturized satellite design is driven by the principle of designing a "good enough" spacecraft to do a job. Most Nanosatellites utilize COTS microcontrollers and application processor SoCs, FPGAs, and combinations thereof [39–41]. These components can offer one to two orders of magnitude more processing performance, are equipped with up to three orders of magnitude more memory, and an abundance of non-volatile storage capacity in comparison to classical space-proprietary components intended for larger satellites, while requiring less energy. Therefore, even a 5kg CubeSats can support a broad variety of commercial payloads and sophisticated scientific instruments, if these can be be fit into a smaller satellite chassis.

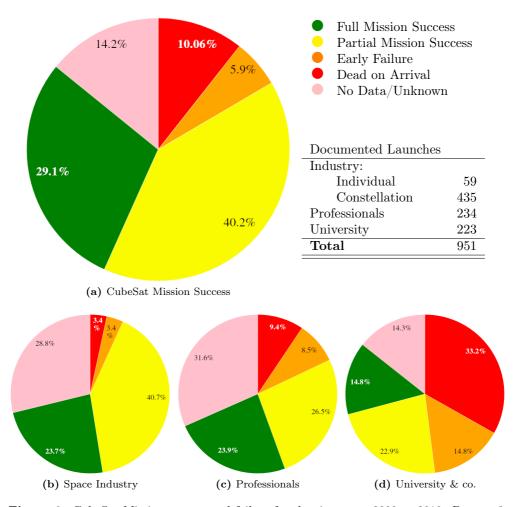

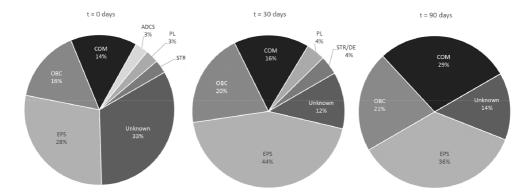

However, miniaturized satellites suffer from lower reliability, which discourages their use in long or critical missions, and for high-priority science. Most nanosatellites launched in the first two decades of the 21st Century (until the time of writing) still experience failure within the first months of their missions [39]. As depicted in Figure 6, even in late 2018 satellite malfunctions and early mission failures are widespread. The First-MOVE CubeSat is also representative in this regard, and we will use it as a case study to showcase the problems that still plaque this field.

#### First-MOVE: A Case Study

As a stereotypical late first-generation CubeSat, First-MOVE's design consisted of several microcontrollers. Its OBC was driven by a ARM926 based ATMEL microprocessor, utilized SDRAM, MRAM and NAND-flash memory, and is overall similar to a contemporary embedded device or smartphone. This fragile system architecture is representative for an entire generation of CubeSats built at that time.

At the time First-MOVE was designed little information was available on which components were expected to perform well in space, and which were likely to fail early on. During the actual construction phase, considerable information on these aspects became available continuously, and so its OBC was adjusted and retrofitted several times. E.g., the introduction MRAM was a retrofit to the original NAND-flash based design, as commercial MRAM was discovered to perform well aboard several earlier first-generation CubeSats. Further information on this First-MOVE's OBC is available in [Fuchs17].

First-MOVE successfully conducted its mission in LEO for two months after launch.

Towards the end of the mission, the OBC began to experience random reboots, which gradually increased over time. As of early 2014, the satellite could no longer be commandeered, and the mission was declared over. Both the funding organization (the german space agency DLR) and the CubeSat community considered the satellite performance and lifetime positive, and as the overall survival rates for CubeSat at that time were very low.

Subsequently, a team of three researchers, one of them being the author of this thesis, conducted a formal review of the First-MOVE project [Fuchs17]. This showed that if First-MOVE's system architecture had been fault-tolerant, the satellite could potentially have been recovered to a safe state. Otherwise, only minor organization issues related to the special setting of academic environments, which is a widespread prob-

**Figure 6:** CubeSat Mission success and failure for the time span 2000 to 2018. Bottom 3 charts show only data for individual CubeSats without satellites in constellations and swarms due to data quality reasons. It is reasonable to assume that developers of unsuccessful CubeSat missions also choose to not share information about the status of their satellites.

Image Credit: Charts produced through the CubeSat Database by Swartwout M. [42]. Military and other sensitive missions are often not publicly documented.

CHAPTER 2

lem in academic satellite and instrumentation projects. A majority of first-generation Nanosatellite failures back then [43] could be attributed to design issues and manufacturing flaws due to developer inexperience (e.g., negative power budgets or dysfunctional communication channels) [39]. At the time of writing, failures caused by inexperience and design flaws have reduced drastically due to project professionalization and an increased staff of full-time developers in small-scale professional projects and academia.

#### 2.3 Nanosatellites Today and Legitimization

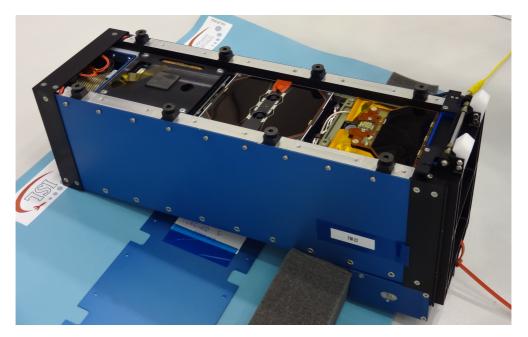

Development on a second satellite, MOVE-II, began in late 2014 and the finished flight model is depicted in Figure 7. Since work on First-MOVE began in 2006, miniaturized satellite development has professionalized and fewer satellites fail due to practical design problems. Instead, the main source of failure aboard CubeSats today are environmental effects encountered in the space environment: radiation, thermal stress, and launch issues [2].

Mission result data shows that technological limitations are the main limiting factor regarding miniaturized satellite reliability at the end of 2018. Figure 6 shows that even experienced, traditional space industry actors who design such satellites "by the book" with quasi-infinite budgets struggle to reach 30% mission success. This lack of reliability and brief mission lifetimes curtails miniaturized satellite usage for critical and long-term space missions, as well as for high-priority science missions for solar system exploration, deep-space probes, and space observatories. During development

Figure 7: The MOVE-II CubeSat, which was part of the author's master thesis research and the design challenges faced during development initiated the research in this thesis.

Image copyright: Langer et al., MOVE-II Team.

of MOVE-II, it became clear to us as spacecraft designers that there were simply no fault-tolerant OBC solutions that could be used to achieve a more reliable satellite design within the constraints of a CubeSat.

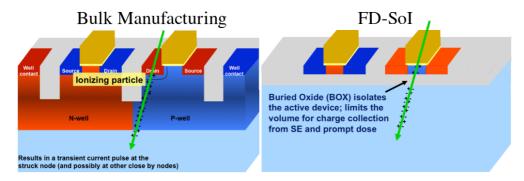

Fault-tolerant computer design for spacecraft still relies upon radiation tolerant special purpose hardware These designs primarily rely upon proprietary fault-tolerant chip designs manufactured in technology nodes with a large feature size (radiation-hardening by design – RHBD) [44] and specialized manufacturing techniques and materials (radiation-hardening by manufacturing and process – RHBM/RHBP) [45]. Often, both of these techniques are combined and a RHBD chip design is manufactured in a RHBD process based with much more coarse feature size than commercial technology. Due to the lower energy efficiency and larger size of and greater distance between transistors, as well as less refined electrical properties, these components also require more energy, and offer less compute power compared to consumer hardware due to decreased clock frequencies and smaller memory sizes.

The use of traditional RHBM/RHBD components at the time of writing is limited to the civilian and military atmospheric aerospace industries, laboratory instrumentation for very large particle experiments run by well funded organizations (e.g., particle accelerators, radiation-testing sites) and traditional space-industry applications in long-term projects where cost considerations are not of primary concern. Especially in nanosatellites, the energy consumption, physical size, and cost of these components are prohibitive, making their use technically impossible and usually uneconomical. Therefore, nanosatellite computing has historically taken two paths: very simple onboard computers (OBCs) based on one single or few microcontrollers and very complex custom-tailored systems. This approach works to a certain extent, as there are a handful of COTS microcontrollers which are designed and manufactured in a way so that they unexpectedly turned out to be radiation hard (radiation-hard by serendipity – RHBS) [46].

At the time of writing, sophisticated fault tolerance capabilities are still absent in Nanosatellites. Instead CubeSat designers try to mitigate faults at the system level using custom mitigation circuitry [47], and thereby achieve "workarounds" to still somehow handle faults encountered in the space environment. The practical effect of this lack of viable fault tolerance techniques and the use of workarounds is reflected in the mission success statistics for miniaturized satellites depicted in Figure 6. However, a few CubeSats have also operated successfully in space for a decade or longer [48]. In practice, this shows that there is no hard technological limitation that would prevent the use of COTS technology in satellite missions with a much longer duration.

Many issues in other fields of spacecraft design can be overcome through engineering-based solutions. Such solutions work well, e.g., for addressing resonance issues, assuring a suitable thermal design and heat-distribution, and for deployable mechanical structures. Engineers therefore attempted to solve the lack of reliability of CubeSats similarly, by constructing custom fault tolerance computer design through component-level redundancy with commodity components. Practical flight results showed that such designs are fragile due to high complexity [39, 49], and tend to perform worse than much simpler designs without fault tolerance capabilities.

Today, nanosatellite designers have to forego fault tolerance in the hope of minimizing failure potential and thereby meeting satellite lifetime requirements for a given space missions by chance [50]. Designers are aware that such satellites may fail at any given point in time during a mission.

CHAPTER 2 21

**Figure 8:** The launch of MOVE-II aboard SpaceX SSO-A: SmallSat Express on December 3<sup>rd</sup>, 2018 from Vandenberg Air Force Base, USA.

Image source: SpaceX SSO-A press material for public use.

MOVE-II was launched into LEO on December 3<sup>rd</sup>, 2018 with Space-X "SSO-A: SmallSat Express" (depicted in 8), where it operates successfully until at the time of writing this thesis. It utilizes only a few basic fault tolerance techniques that were available in commodity embedded components and COTS CubeSat subsystems. Its overall system architecture is still not fault-tolerant. Risk acceptance at this level is a viable approach only for educational, and uncritical, low-priority missions with brief duration. To construct future, more reliable miniaturized satellites, a robust, fault tolerance on-board computer architecture is needed. However, such an architecture do not exist yet, and with the research in this thesis I intend to change that.

#### 2.4 Fault-Tolerant Computer Architecture

Fault tolerance in the most abstract sense, implies the capability of a system to overcome and gracefully handle failures. It is crucial for satellite computer design and a practical necessity to assure reliable operation of a satellite computer during space missions with an extended duration. As described in the previous section, the lack of such functionality within contemporary miniaturized satellites has become a major constraint to increase adoption of these spacecraft.

Fault-tolerant computer architecture, which is discussed briefly in this section, covers only a small part the entire field of fault tolerance and reliability engineering. Among others, systems can be designed to tolerate human error [51] and external attacks, which would require the discussion of aspects of psychology and human interface

design. In the remainder of this section, we discuss fault tolerance modes, measures, and testing from the perspective of computer architecture for spaceflight applications to provide the necessary background for this thesis. A more complete look on the different aspects and sub-fields of fault tolerance are available in literature, e.g., in [52].

Considering fault-tolerant computer architecture, the faults we must protect a system from depend on the application, the environment it operates in, as well as practical operating conditions (e.g., temperature and system load). Besides that, faults can occur due to technological wear and aging, and sometimes by chance. Many protective measures can be used to achieve fault tolerance for computer systems [53,54]. Often, the practical purpose for the application of these techniques is often not fault tolerance itself, but the need to increase scalability [55,56], manufacturing yield [57,58], higher clock frequencies and data throughput [59–61].

Different industries apply different fault tolerance techniques due to a variety of practical reasons, and today often maintain their own, proprietary implementations to tackle their domain-specific challenges. For proprietary fault tolerance implementations in different industrial applications, there is usually no immediate incentive to share and generalize such fault tolerance techniques by themselves, unless they can be patented, commercialized, and thereby protected [62]. This gap in turn is covered by scientists and researchers in industry and academia.

Today there is an entire field of science that tries to generalize application specific fault tolerance techniques, to produce new fault tolerance concepts through recombination. Unfortunately, this recombination is often done without considering the original application and its boundary conditions. As we show in Chapters 4 and 6, academic research and publications covering this topic are kept very abstract and do not consider a specific real-world application anymore. This works well for certain fields of science and even some fault tolerance topics<sup>2</sup>. However, for practical applications to system-architecture this is not the case, as generic solutions without proper boundary conditions and a realistic fault profile, can usually not be applied anymore to a real system. Today, academic fault tolerance research has produced a vast amount of publications and generated many theoretical concepts. But, only a handful of fault tolerance concepts envisioned by academic fault tolerance research have been implemented and tested in practice, and most have been ignored entirely by the industry. One could argue that this is the way science works, but knowingly publishing invalid and research without validation can also be seen as dishonest and only hinders publication of actually valuable research.

The path to validate such concepts is long, time-consuming, costly, and requires large amounts of engineering work [64–66]. The obtained validation results are often not considered publishable by academics, as they require a high degree of labor just to achieve one brief paper, while multiple theoretical journal publications could be produced in their stead. Industrial users are aware of such research [67], but are often skeptical. In the space industry, for example, concerns regarding validity, testability, verifyability and a perceived general lack of maturity of academic research has caused an entire industry to conservatively use very old technology [1].

When designing fault-tolerant systems, we must consider an application's operating environment, its fault profile, and system design constraints [68]. Generic fault tol-

<sup>&</sup>lt;sup>2</sup>E.g.: erasure codes and performance overhead calculations to achieve quality of service under faults [63] can largely be discussed without a specific application in mind, as long as key parameters match.

CHAPTER 2 23

erance concepts can serve as building blocks to design a comprehensive fault-tolerant architecture, assuming they are validated in a realistic manner.

### 2.4.1 Terminology and Fault Tolerance Objectives

Today, scientists and engineers use the terms ECC, EDAC, FDIR, and error correction almost interchangeably, while reliability, redundancy, fault tolerance, and robustness are surrounded by a shroud of marketing. In practice, error detection and correction (EDAC), fault-detection, isolation, and recovery (FDIR), redundancy, and failover all are distinct tools. They can be applied to achieve different kinds of fault tolerance, e.g., computational correctness, continuous non-stop operation, failover, and simple error correction.

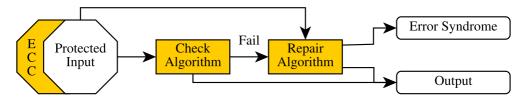

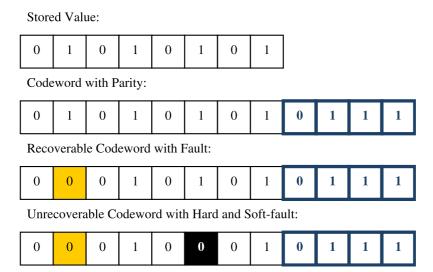

Error detection and correction (EDAC) implementations usually utilize one or multiple erasure codes [69] to implement error correction coding (ECC), which allows errors in stored and transmitted data to be corrected. EDAC is efficient only for protecting the integrity of frequently access data, and may do so passively in the background without requiring a computer system to actively handle a fault in software. These limitations can be mitigated only in combination with other design measures such as error scrubbing and by generating error syndromes to notify the system about a fault [70].

FDIR instead assures that a fault-induced error is not just detected and corrected, but also that side-effects are isolated and resolved (e.g. discussed in [71] for space applications). In contrast, in case EDAC logic encounters errors when decoding data, it may inform the system about the result through an ECC syndrome and corrects data passing through. FDIR does not necessarily imply computation correctness, usually utilizes fault tolerance measures to achieve error detection and correction, but otherwise implies only that a fault is corrected and the system is restored to a working state.

Fail-over, in contrast, can be implemented as one-shot measure, e.g., with simple redundancy as discussed in [72], by falling from a primary to a secondary system instance and do not have to assess correctness, but only need be capable to detect faults. One of the most common applications for this approach is RAID1 with 2 memories or disks [72], but similar applications exist for avionics and network architecture in spaceflight and atmospheric aerospace applications [73].

### 2.4.2 Fault Detection and Correctness

To facilitate fault detection, we can exploit algorithmic measures as well as result comparison achieved through component replication (spatial redundancy) or repeat-execution (temporal redundancy). With algorithmic approaches detected errors can be reconstructed using parity data (informational redundancy) information, or by utilizing an alternative result generated through spatial or temporal redundancy. We refer to this type or error correction as forward error correction (FEC) [74]. Alternatively, backwards error correction (BEC) can be achieved with temporal redundancy and algorithmic measures, and implies message retransmission or re-execution of a failed operations [75].

### Algorithmic Fault Detection and Informational Redundancy

The algorithmic approach exploits an inherent property of a system to detect faults. It can only be used if there is an inherent property in a system or protected data that can be used to judge the occurrence of a fault [76,77]. Fault detection then does not imply the ability of the system to determine a correct result, but only the ability to asses if the protected data or system is faulty.

Algorithmic fault detection often exploits informational redundancy, but it may also use other inherent mathematical properties of data or logic-design properties of a system [77]. To a limited extent, algorithmic fault-detection can also be used to protect a program's data and control flow, e.g., by computing or modifying checksums for each executed instruction passing through a CPU's pipeline [78]. However, this requires a non-standard processor pipeline [79], a custom compiler toolchain [80], and therefore is feasible only for embedded software with a very specific structure.

**Figure 9:** An example of algorithmic redundancy where extra algorithmic information is indicated separately as ECC. This extra information could also be an inherent property of the input data, instead of separate.

### **Spatial Redundancy**

When utilizing spatial redundancy, we can realize fault-detection by comparing the output of multiple redundantly implemented system modules or equivalent but differently implemented variants of a subsystem run in parallel. Spatial redundancy can be implemented at all scales: for individual transistors and circuits, sets of logic, logic blocks, IP-cores, IP-core groups, ICs, components, to even an entire computer. At

Figure 10: An example of spatial redundancy with 3 replicated modules in a TMR setup.

CHAPTER 2 25

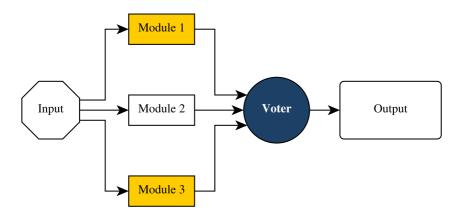

different scales spatial redundancy will offer different protective properties and different a level of scalability. A simple implementation of spatial redundancy requires replication of the actually protected modules as depicted in Figure 10.

We refer to systems consisting of N modules collectively as NMR systems. With 2 redundant modules, we can detect faults through supervision or in conjunction with a watchdog, to which we refer to as dual modular redundancy (DMR). We can determine correctness through a simple majority vote, for which at least 3 modules are needed (triple modular redundancy – TMR). These systems can be scaled up to realize 2k+1 redundancy, as an odd-number of modules is needed to avoid a draw during voting. With more than 3 modules, more sophisticated voting concepts can be realized which then do no longer require a centralized and guaranteed-correct voting oracle [81] or allow a distributed majority decision [82]. An NMR systems can also be outfitted with spare modules to handle multiple subsequent transient faults or permanent faults.

### Temporal Redundancy

Temporal redundancy implies re-execution of an operation multiple times in sequence, and example of which is depicted in Figure 11. Like in spatial redundancy, this is often done in 2k+1 setups to assure error correction. This favors checkpoint implementation in software and the use of software diversity [83]. It is suitable for protecting applications where failed results can be discarded, individual operations can be repeated, or where an application as a whole can be restarted in a side-effect free manner. For most control systems and software running on general purpose computers, however, this is not the case.

The use of temporal redundancy introduces a degree non-determinism to an applications application, which can conflict with a requirements for real-time guarantees [84]. Thus, temporal redundancy concepts usually can only be applied to real-time systems unless the protected software implements a very specific structure [85]. Protection of applications at the scale of an operating systems, and programs with a complex program state or structure may incur a high performance overhead [86]. Due to the time-dependent nature of temporal redundancy, this form of redundancy is vulnerable to faults occurring in bursts or groups [87].

#### Task Schedule:

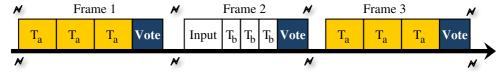

Figure 11: Task schedule of a temporal redundancy where every scheduled task  $(T_n)$  is executed 3 times with majority voting.

### Fault Detection Granularity

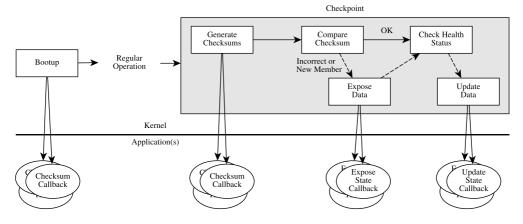

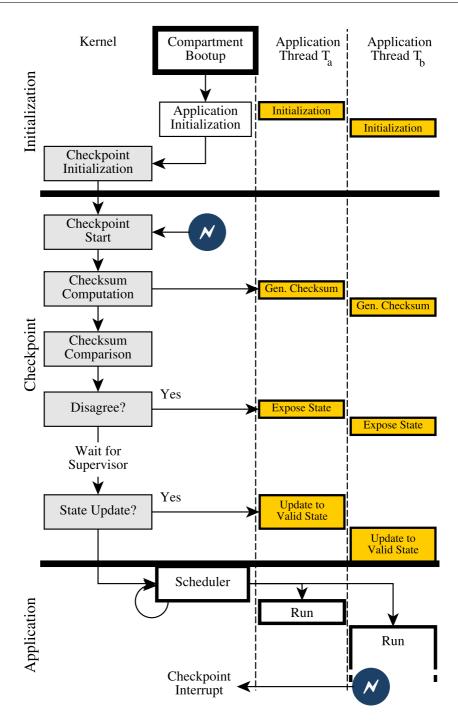

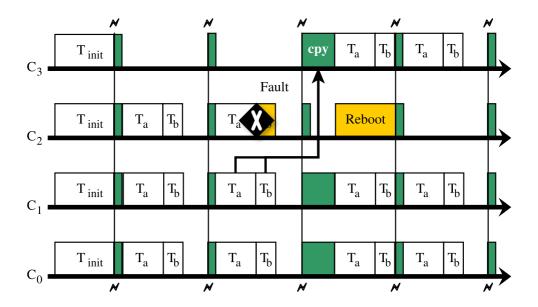

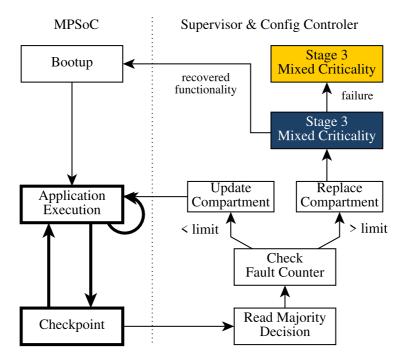

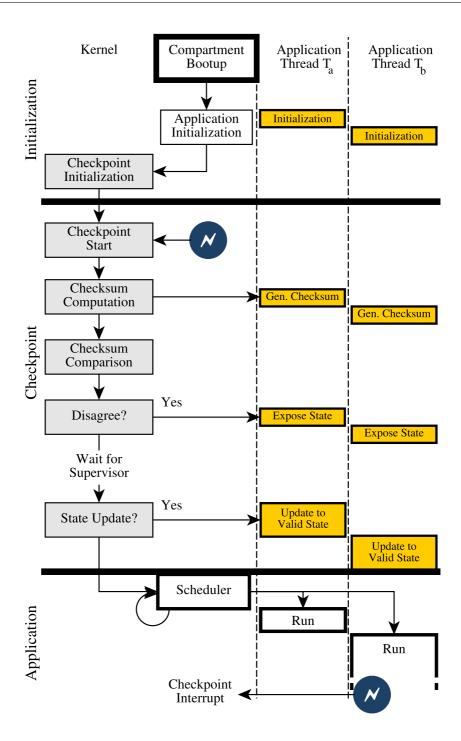

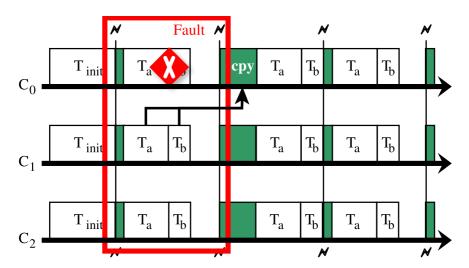

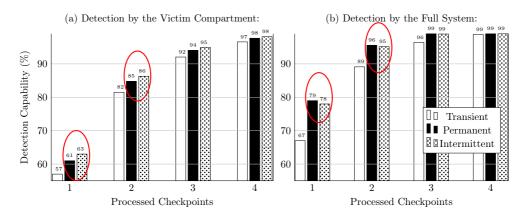

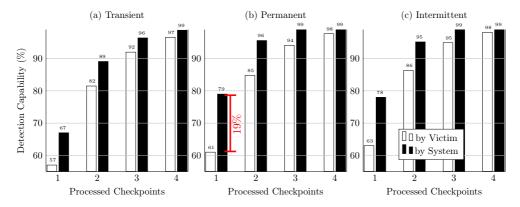

The granularity and frequency for performing voting in spatial and temporal redundancy, as well as erasure coding parameters should be chosen based on the expected fault model and environmental conditions.