# Improved hard real-time scheduling and transformations for embedded Streaming Applications

Spasic, J.

## Citation

Spasic, J. (2017, November 14). *Improved hard real-time scheduling and transformations for embedded Streaming Applications*. Retrieved from https://hdl.handle.net/1887/59459

| Version:         | Not Applicable (or Unknown)                                                                                                            |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| License:         | <u>Licence agreement concerning inclusion of doctoral thesis in the</u><br><u>Institutional Repository of the University of Leiden</u> |

| Downloaded from: | https://hdl.handle.net/1887/59459                                                                                                      |

Note: To cite this publication please use the final published version (if applicable).

Cover Page

# Universiteit Leiden

The following handle holds various files of this Leiden University dissertation: <u>http://hdl.handle.net/1887/59459</u>

Author: Spasic, J. Title: Improved hard real-time scheduling and transformations for embedded Streaming Applications Issue Date: 2017-11-14 Improved Hard Real-Time Scheduling and Transformations for Embedded Streaming Applications

Jelena Spasić

### Improved Hard Real-Time Scheduling and Transformations for Embedded Streaming Applications

#### PROEFSCHRIFT

ter verkrijging van de graad van Doctor aan de Universiteit Leiden, op gezag van Rector Magnificus Prof.mr. C.J.J.M. Stolker, volgens besluit van het College voor Promoties te verdedigen op dinsdag 14 november 2017 klokke 13:45 uur

door

Jelena Spasić geboren te Trgovište, Servië in 1984

| Promotor:            | Prof. dr. Joost N. Kok       | Universiteit Leiden        |

|----------------------|------------------------------|----------------------------|

| <b>Co-Promotor:</b>  | Dr. Todor P. Stefanov        | Universiteit Leiden        |

| Promotion Committee: | Prof. dr. Alix Munier Kordon | Université de Paris - LIP6 |

|                      | Prof. dr. Petru Eles         | Linköpings Universitet     |

|                      | Dr. Andy Pimentel            | Universiteit van Amsterdam |

|                      | Prof. dr. Aske Plaat         | Universiteit Leiden        |

|                      | Prof. dr. Jaap van den Herik | Universiteit Leiden        |

|                      | Prof. dr. Harry Wijshoff     | Universiteit Leiden        |

Improved Hard Real-Time Scheduling and Transformations for Embedded Streaming Applications Jelena Spasić. -Dissertation Universiteit Leiden. - With ref. - With summary in Dutch.

Copyright © 2017 by Jelena Spasić. All rights reserved.

Cover designed by Miloš Ačanski.

This dissertation was typeset using LATEX.

ISBN 978-94-6299-783-7 Printed by Ridderprint, Ridderkerk, The Netherlands.

Mojoj porodici To my family

# Contents

| Та | ble o       | f Conte        | ents                                                                                                    | vii      |

|----|-------------|----------------|---------------------------------------------------------------------------------------------------------|----------|

| Li | st of [     | Figures        |                                                                                                         | xi       |

| Li | st of '     | Tables         | :                                                                                                       | xiii     |

| Li | st of       | Abbrev         | viations                                                                                                | xv       |

| 1  | Intr<br>1.1 | oductio        |                                                                                                         | 1<br>3   |

|    | 1.1         | 1.1.1          | s in the Design of Embedded Streaming Systems<br>Platform Trend: Multi-Processor System-on-Chip (MPSoC) | 3        |

|    | 1.2         | 1.1.2<br>Desig | Design Trend: Model-based Design Methodology<br>n Requirements and Basic Approaches to Meet the Re-     | 5        |

|    |             | quirer         | nents                                                                                                   | 7        |

|    |             | 1.2.1          | Timing Requirements                                                                                     | 7        |

|    | 1 0         | 1.2.2          | Energy Requirements                                                                                     | 9<br>10  |

|    | 1.3         | 1.3.1          | em Statement                                                                                            | 10<br>10 |

|    |             |                | Problem 2                                                                                               | 10       |

|    |             |                | Problem 3                                                                                               | 10       |

|    |             | 1.3.4          | Problem 4                                                                                               | 12       |

|    | 1.4         |                | rch Contributions                                                                                       | 13       |

|    | 1.5         |                | S Outline                                                                                               | 15       |

| 2  | Bac         | kgroun         | d                                                                                                       | 17       |

|    | 2.1         | Datafl         | low Models-of-Computations (MoCs)                                                                       | 17       |

|    |             | 2.1.1          | Cyclo-Static Dataflow (CSDF)                                                                            | 18       |

|    |             | 2.1.2          | Polyhedral Process Network (PPN)                                                                        | 20       |

|    | 2.2         | Real-T         | Time Scheduling Theory                                                                                  | 22       |

|    |             | 2.2.1          | Task Model                                                                                              | 22       |

|   |      | 2.2.2 System Model                                             | 23 |

|---|------|----------------------------------------------------------------|----|

|   |      | 2.2.3 Real-Time Scheduling Algorithms                          | 23 |

|   |      | 2.2.4 Uniprocessor Schedulability Analysis                     | 24 |

|   |      | 2.2.5 Multiprocessor Schedulability Analysis                   | 27 |

| 3 | Har  | d Real-Time Scheduling Framework                               | 31 |

|   | 3.1  | Problem Statement                                              | 32 |

|   | 3.2  |                                                                | 32 |

|   | 3.3  | Related Work                                                   | 33 |

|   | 3.4  | Motivational Example                                           | 35 |

|   | 3.5  |                                                                | 37 |

|   |      |                                                                | 37 |

|   |      | 0                                                              | 41 |

|   |      | 0                                                              | 44 |

|   |      | 0                                                              | 46 |

|   |      |                                                                | 47 |

|   |      | •                                                              | 52 |

|   | 3.6  | 0                                                              | 54 |

|   |      |                                                                | 55 |

|   |      |                                                                | 59 |

|   |      |                                                                | 61 |

|   | 3.7  |                                                                | 63 |

| 4 | Exp  | loiting Parallelism in Hard Real-Time Systems to Maximize Per- |    |

|   | -    |                                                                | 65 |

|   | 4.1  |                                                                | 66 |

|   | 4.2  |                                                                | 67 |

|   | 4.3  |                                                                | 67 |

|   | 4.4  |                                                                | 69 |

|   | 4.5  |                                                                | 72 |

|   | 4.6  | 0 I                                                            | 75 |

|   | 4.7  |                                                                | 78 |

|   | 1.7  |                                                                | 79 |

|   |      |                                                                | 80 |

|   |      | 0                                                              | 82 |

|   | 4.8  | 1 , 6                                                          | 82 |

| 5 | Exp  | loiting Parallelism in Hard Real-Time Systems to Minimize En-  |    |

|   | ergy |                                                                | 85 |

|   | 5.1  |                                                                | 86 |

|   |      |                                                                |    |

|    | 5.2        | Contributions                                            |           |

|----|------------|----------------------------------------------------------|-----------|

|    | 5.3        | Related Work                                             |           |

|    | 5.4        | Motivational Example                                     | 90        |

|    | 5.5        | System Model                                             | 93        |

|    | 5.6        | Energy Model                                             | 94        |

|    | 5.7        | The Proposed Energy Minimization Approach                | 95<br>05  |

|    |            | 5.7.1 The Data-Parallel Energy Minimization Algorithm    | 95        |

|    |            | 5.7.2 Task Classification for Energy Minimization        | 98        |

|    | <b>–</b> 0 | 5.7.3 Task Mapping for Energy Minimization               | 99<br>102 |

|    | 5.8        | Evaluation                                               | 103       |

|    |            | 5.8.1 Comparison with [CKR14], [LSCS15], [SDK13] on Het- | 104       |

|    |            | erogeneous MPSoCs                                        | 104       |

|    |            | 5.8.2 Comparison with [Lee09] on Heterogeneous MPSoCs.   | 106       |

|    |            | 5.8.3 Comparison on Homogeneous MPSoC                    |           |

|    | <b>F</b> 0 | 5.8.4 Overhead and Time Complexity Analysis              | 109       |

|    | 5.9        | Discussion                                               | 110       |

| 6  | An .       | Accurate Energy Modeling of Streaming Systems            | 111       |

|    | 6.1        | Problem Statement                                        | . 111     |

|    | 6.2        | Contributions                                            | 112       |

|    | 6.3        | Related Work                                             | 113       |

|    | 6.4        | System Model                                             | 115       |

|    |            | 6.4.1 Application Model                                  | 115       |

|    |            | 6.4.2 Platform Model                                     | 116       |

|    |            | 6.4.3 Application-to-Platform Mapping                    |           |

|    | 6.5        | Energy Model                                             | 118       |

|    |            | 6.5.1 Model Formulation                                  | 118       |

|    |            | 6.5.2 Derivation of Model Parameters                     |           |

|    | 6.6        | Evaluation of the Energy Model                           |           |

|    | 6.7        | Discussion                                               | 130       |

| 7  | Sun        | nmary and Conclusions                                    | 133       |

| Bi | bliog      | graphy                                                   | 137       |

| Sa | men        | vatting                                                  | 153       |

| т; | et of      | Publications                                             | 156       |

|    |            |                                                          | 130       |

| Cı | urricu     | ılum Vitae                                               | 159       |

# Acknowledgments

161

# **List of Figures**

| 1.1<br>1.2        | An MPSoC platform example                                                                                                                                                                             | 4<br>6         |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 2.1<br>2.2        | A CSDF graph <i>G</i>                                                                                                                                                                                 | 19<br>21       |

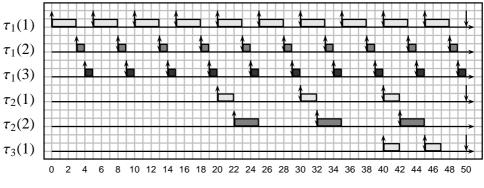

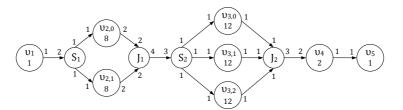

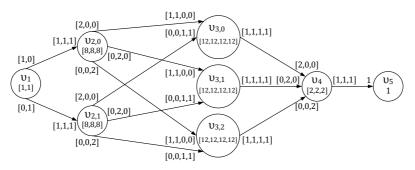

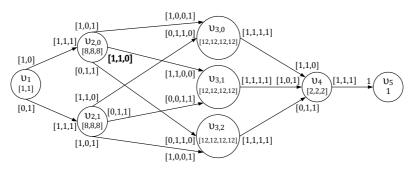

| 3.1<br>3.2<br>3.3 | (a) The SPS and (b) ISPS of graph <i>G</i> in Figure 2.1 The periodic schedule $\sigma$ for the CSDF graph <i>G</i> shown in Figure 2.1. Production and consumption curves on edge $e_u = (v_i, v_j)$ | 36<br>41<br>50 |

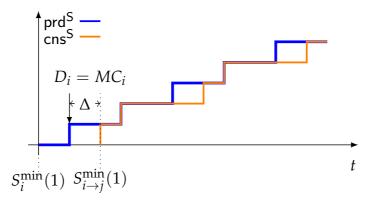

| 4.1               | An SDF graph G                                                                                                                                                                                        | 69             |

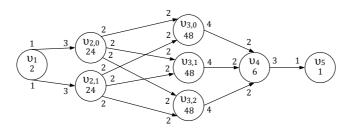

| 4.2               | Equivalent graphs of the SDF graph in Figure 4.1 by unfolding actor $v_2$ by factor 2 and $v_3$ by factor 3                                                                                           | 70             |

| 4.3               | Unfolding channel $e_2$ from the graph in Figure 4.1 by using Algorithm 3 when $\vec{f} = [1, 2, 3, 1, 1]$ .                                                                                          | 74             |

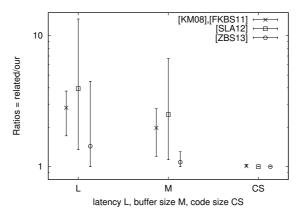

| 4.4               | Comparison of our unfolding transformation to the approaches in [KM08], [FKBS11], [SLA12], [ZBS13].                                                                                                   | 80             |

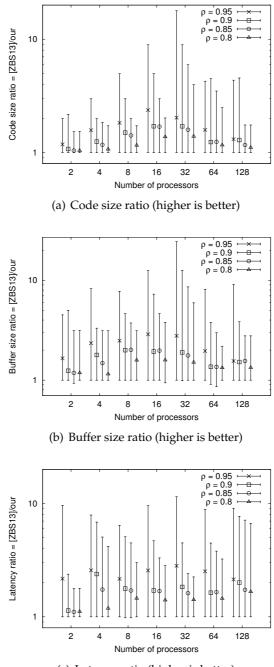

| 4.5               | Results of performance evaluation of our proposed approach<br>in comparison to the approach in [ZBS13]                                                                                                | 81             |

| 4.6               | Results of time evaluation of our proposed approach in com-<br>parison to the approach in [ZBS13]                                                                                                     | 83             |

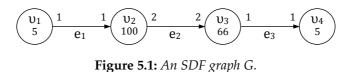

| 5.1               | An SDF graph G.                                                                                                                                                                                       | 91             |

| 5.2               | A CSDF graph <i>G</i> ' obtained by unfolding SDF graph <i>G</i> in Figure 5.1 with $\vec{f} = [1, 2, 2, 1]$ .                                                                                        | 91             |

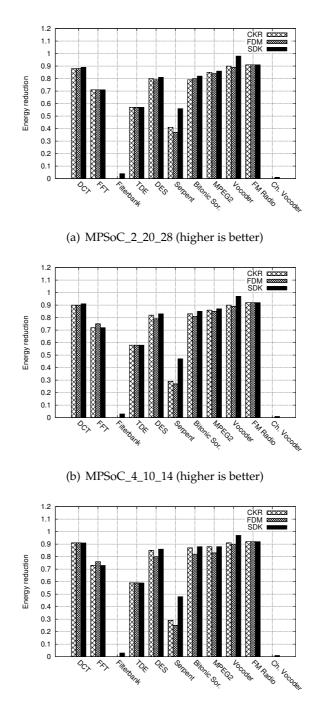

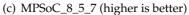

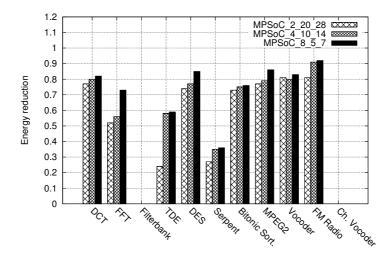

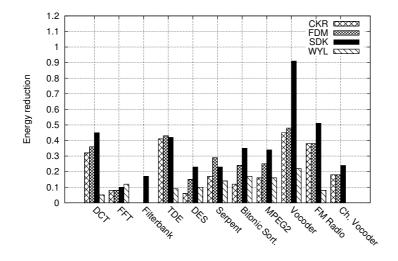

| 5.3               | Comparison of our proposed DPEM approach with related approaches on heterogeneous MPSoCs                                                                                                              | 105            |

| 5.4               | Comparison between DPEM and WYL on heterogeneous MP-                                                                                                                                                  |                |

| 5.5               | SoCs                                                                                                                                                                                                  | 107<br>108     |

|                   |                                                                                                                                                                                                       |                |

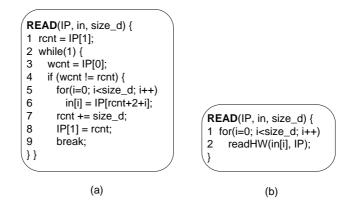

| 6.1 | The read primitive implemented in software (a) and hardware |       |

|-----|-------------------------------------------------------------|-------|

|     | (b)                                                         | 115   |

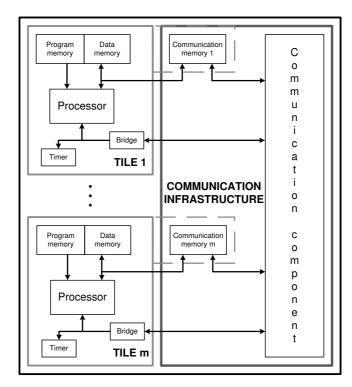

| 6.2 | The architecture template of MPSoC platforms                | . 117 |

# **List of Tables**

| 2.1        | Summary of mathematical notations                                                                                                               | 17  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.1        | Throughput, latency and number of processors for <i>G</i> under different scheduling schemes.                                                   | 36  |

| 3.2        | Benchmarks used for evaluation.                                                                                                                 | 54  |

| 3.3        | Comparison of different scheduling approaches.                                                                                                  | 58  |

| 3.4        | Time complexity (in seconds) of different scheduling approaches.                                                                                | 58  |

| 3.5        | Time complexity (in seconds) for the calculation of number of                                                                                   | -0  |

| 0 (        | processors.                                                                                                                                     | 58  |

| 3.6        | Performance of the ISPS approach under different latency con-<br>straints                                                                       | 63  |

| 4.1<br>4.2 | Results for <i>G</i> transformed by different transformation approaches.<br>Results for <i>G</i> transformed and mapped on 2 processors by dif- | 71  |

|            | ferent approaches                                                                                                                               | 71  |

| 4.3        | Benchmarks used for evaluation.                                                                                                                 | 79  |

| 5.1        | Different MPSoC designs for G in Figure 5.1.                                                                                                    | 91  |

| 5.2        | 8                                                                                                                                               | .03 |

| 6.1        | Accuracy of the energy model for CB, ShB and P2P MPSoC platforms                                                                                | 29  |

| 6.2        | Accuracy of the energy estimation when contention is not con-                                                                                   | .30 |

# **List of Abbreviations**

| ADF  | Affine Dataflow                   |

|------|-----------------------------------|

| BF   | Best-Fit                          |

| BFD  | Best-Fit Decreasing               |

| CDP  | Constrained-Deadline Periodic     |

| CPU  | Central Processing Unit           |

| CSDF | Cyclo-Static Dataflow             |

| DCT  | Discrete Cosine Transform         |

| DLP  | Data-Level Parallelism            |

| DM   | Deadline Monotonic                |

| DPEM | Data Parallel Energy Minimization |

| DSE  | Design Space Exploration          |

| EDF  | Earliest Deadline First           |

| EE   | Energy Efficient                  |

| ESL  | Electronic System-Level           |

| FF   | First-Fit                         |

| FFD  | First-Fit Decreasing              |

| FFID | First-Fit Increasing Deadlines    |

| FIFO | First-In First-Out                |

| FPGA  | Field-Programmable Gate Array                       |

|-------|-----------------------------------------------------|

| GPU   | Graphics Processing Unit                            |

| HSDF  | Homogeneous SDF                                     |

| ICP   | Integer Convex Programming                          |

| IDP   | Implicit-Deadline Periodic                          |

| ILP   | Integer Linear Programming                          |

| ISA   | Instruction-Set Architecture                        |

| ISPS  | Improved Strictly Periodic Scheduling               |

| ISS   | Instruction Set Simulators                          |

| ITRS  | International Technology Roadmap for Semiconductors |

| KPN   | Kahn Process Network                                |

| LLF   | Least Laxity First                                  |

| LP    | Linear Programming                                  |

| LTE   | Long-Term Evolution                                 |

| MIDCP | Mixed Integer Disciplined Convex Programming        |

| MJPEG | Motion JPEG                                         |

| MoC   | Model of Computation                                |

| MPSoC | Multi-Processor System-on-Chip                      |

| NoC   | Network-on-Chip                                     |

| NP    | Non-deterministic Polynomial-time                   |

| PE    | Performance Efficient                               |

| PLP   | Pipeline-Level Parallelism                          |

| PM    | Power Management                                    |

| PPN   | Polyhedral Process Network                          |

| PS   | Periodic Scheduling          |

|------|------------------------------|

| RM   | Rate Monotonic               |

| RSD  | Reed Solomon Decoder         |

| RTA  | Response Time Analysis       |

| RTL  | Register-Transfer-Level      |

| SDF  | Synchronous Data Flow        |

| SPS  | Strictly Periodic Scheduling |

| STS  | Self-timed Scheduling        |

| TLP  | Task-Level Parallelism       |

| VFS  | Voltage-Frequency Scaling    |

| VLE  | Variable Length Encoder      |

| WCET | Worst-Case Execution Time    |

| WF   | Worst-Fit                    |

| WFD  | Worst-Fit Decreasing         |

# Chapter 1

# Introduction

I N the modern-day world, electronics is not only a tool for survival but an integral part of almost every aspect of human lives. Everything from our home appliances, cars, tablets to our cell-phones uses electronics or electronic components in some way. Constantly improving, the electronics technology is making life faster, easier and more convenient for people. Modern electronics technology is rapidly changing the way people communicate and transmit data and information. Thus, it is possible and common today to execute work related tasks remotely. Health-care systems have also benefited a lot from electronics technology. There, electronics technology is helping doctors accurately diagnose and treat illnesses in a timely manner. For example, in Philips Healthcare, live image guided intervention has been used in treatment of structural heart diseases. Using electronics in home automation received popularity in the past decades. People have the capability to control almost everything in their "smart homes" from heating, air conditioning, and lighting, to kitchen appliances and security systems.

Even though electronics technology has been used in all of the above cases, in each case it has its dedicated purpose within a larger system it has been embedded into, hence the name "embedded electronics". Embedded electronics, that is, **embedded systems**, are tightly coupled to the environment in which they operate. They collect information about the environment through sensors and control that environment through actuators, hence embedded systems must provide real-time guarantees, that is, a correct on-time output [Mar06]. Given that embedded systems are dedicated towards a certain application, they are designed to implement well-defined set of functionalities. In addition, having that many embedded systems are battery-operated they have to be efficient in terms of energy consumption and resource usage.

An important class of embedded systems are embedded streaming systems. Embedded streaming systems process a long, potentially infinite, stream of input data coming from the environment. Each data item is processed for a limited time. The processing operations on different data items are selfcontained and there is little control flow between the operations. The result of the processing is a long, potentially infinite, stream of output data fed into the environment. Usually, streaming applications must process a large amount of data within short periods of time. Thus, efficiency, in terms of both throughput and latency, is of primary concern in the design of embedded streaming systems. The throughput represents the rate at which output data items are produced, while the latency represents the time interval between the arrival of a data item to the application input and the production of the corresponding data item at the application output. Examples of streaming applications include audio beamforming, video encoding and decoding, image and signal processing, network protocol processing, navigation, computer vision, and others.

One of the key properties of embedded streaming systems is that their correct functionality depends not only on the correct result but also on the time at which the result is produced. Such systems, where the timing is critical to the correct functionality, are called **real-time systems**. Real-time systems can be classified into **hard** and **soft** systems. A hard real-time system is one where not meeting the timing requirements leads to a system failure, which, in life-critical systems, may have catastrophic consequences. In contrast, in soft real-time systems, not meeting the timing requirements does not lead to a failure but to degraded system performance that can be tolerated given that the timing miss rates are below a certain threshold. Classifying a system into hard or soft real-time depends usually on the overall system requirements and the environment where the system is deployed.

As examples of real-time embedded streaming systems, today we have increasing number of various autonomous mobile systems that need to interact and respond to their dynamic environment extremely fast. These include very complex systems such as self-driving cars and planes, but also modern "toys" such as drones. In recent years, drones have been used extensively as data collectors in many areas. For example, drones have been used in law enforcement for surveillance, tracking and rescue operations. They have been used for monitoring purposes in agriculture and farming, archaeological and land surveying, for delivery purposes in healthcare, crowd monitoring and control, and other cases of monitoring and control. They can carry various types of equipment including live-feed video cameras, infrared cameras, inertial, position and heat sensors. The large amount of data which should be collected and (pre-)processed, the battery-powered operation nature, and the need to react in a short time create demand for designing a high-performance energy-efficient real-time embedded streaming systems. In the next section, we discuss the current trends in designing such systems.

# 1.1 Trends in the Design of Embedded Streaming Systems

As introduced earlier, there is a demand in modern embedded streaming systems for high performance, in terms of high application throughput and short application latency, and a demand for real-time and energy-efficient execution. In addition, the complexity of applications running on embedded platforms increases [EJ09]. Therefore, we discuss below the trends in designing such complex embedded streaming systems to meet all the demands.

### 1.1.1 Platform Trend: Multi-Processor System-on-Chip (MPSoC)

Following the trend in general purpose systems, embedded streaming systems designers have relied for a long time on improvement of the computational power of uniprocessors to meet the high-performance requirements of streaming applications. The improvements of the computational power were driven by the increase in the clock frequency, advances in the semiconductor technology, that is, technology scaling, and innovations in the architecture (pipelining, out-of-order execution, branch prediction, and others.) [HP06]. However, the monotonically increasing performance curve with the successive generations of uniprocessors flattened in the early 2000s [PDG06]. The reasons for the curve flattening were increased dynamic power consumption and design complexity with the frequency increase and architecture innovations as well as increased static power and power density with the technology scaling [PDG06]. To increase system performance further, such that high-performance requirements of running applications are met, designers went for **multi-processor platforms** as the natural next evolutionary step in staying on the increasing performance curve [HP06]. By using multiple processors, the issue of increased power consumption is partially addressed by lower operating voltage and frequency, thereby decreasing the power consumption while maintaining high system performance through parallel execution. Moreover, nowadays, embedded systems designers integrate multiple processors, memories, interconnections, and peripherals into a **Multi-Processor System-on-Chip (MPSoC)** [JTW05].

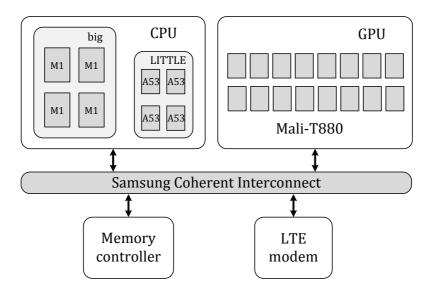

Figure 1.1: An MPSoC platform example.

Usually, an MPSoC contains different kinds of processors dedicated to certain functionalities: Central Processing Unit (CPU) for general purpose processing, Graphics Processing Unit (GPU) for graphical processing, a dedicated processor for wireless communication, and others. The processors communicate with each other through an on-chip communication infrastructure. To enable efficient communication, designers proposed and developed high-performance buses, such as ARM AMBA communication infrastructures [ARM], and Network-on-Chip (NoC) [BDM02] infrastructures, such as Xpipes [BB04] and Æthereal [GDR05]. Figure 1.1 gives an example of an MPSoC, the Exynos 8 Octa 8890 [Sama], which can be found in the Samsung S7 mobile phones. The Exynos 8 Octa has eight CPUs in a big.LITTLE architecture [Gre11]. That is, by integrating CPUs with different power-performance characteristics, namely, performance-efficient Exynos M1 cores (big cores) and energy-efficient Cortex A53 cores (LITTLE cores), this MPSoC provides more than 30% improvement in performance and 10% improvement in power efficiency compared to its predecessor [Sama]. The MPSoC also contains a 16-core GPU for 2D/3D graphical processing. The on-chip LTE modem is used for high-speed wireless data communication. All the processors are connected through a high-performance cache coherent interconnect. In this thesis, we consider such type of MPSoC platforms, efficiently utilizing their CPU part by mapping streaming applications on the CPUs.

#### 1.1.2 Design Trend: Model-based Design Methodology

Driven by constant improvements in the semiconductor technology, MPSoC platforms integrate more and more processing elements on a chip. On the other hand, the complexity of embedded software also increases [EJ09]. In order to design such a complex embedded streaming system in an efficient manner in terms of system quality, design effort and time, designers had to raise the level of design abstraction from *Register-Transfer-Level (RTL)* to system-level [KMN<sup>+</sup>00], [NSD08]. At the system-level, a hardware **platform** is modeled as a set of primitive blocks describing, at a high-level of abstraction, processing elements, memories and interconnects. An **application** is modeled as a set of tasks which can be allocated to hardware resources in many different ways, which means that there are many possible mappings of tasks to platform resources. Once it is determined how the application tasks are going to be allocated to the hardware resources such that all design *constraints* are met, that is, once we have a **mapping** specification, an Electronic System-Level (ESL) synthesis tool [GHP<sup>+</sup>09] generates in an automated way the hardware description at a lower level of abstraction and the software for each processor in a platform.

In order to achieve the desired performance, the applications which are going to execute on the MPSoC platform have to be specified in a way which utilizes the *parallel* processing elements in the platform. In general, identifying parallelism in an application is a difficult step. In addition, designers should determine the mapping and execution order, that is, scheduling, of application tasks to a platform, and code should be generated for each used processor in the platform. In order to perform all these design steps in an efficient way, designers raise the level of abstraction, as introduced earlier, by building high-level models of applications. Then, the designer can use these models to analyze the performance of different applications-to-platform mappings. Such design approach is called **Model-based design** and the models used in such an approach are called **Models of Computation (MoCs)**. A MoC describes in a formal way how an application works. In this thesis, we consider only parallel MoCs because they are suitable for expressing parallelism in an application which is going to be executed on an MPSoC platform. In a parallel MoC, an application is decomposed into tasks which can be executed in parallel. The parallel MoC defines how tasks communicate and synchronize with each other.

Streaming applications have ample amount of parallelism which should be exploited efficiently to satisfy the performance requirements. Researchers have identified three types of parallelism:

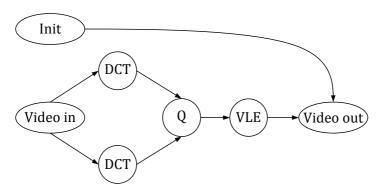

Figure 1.2: Motion JPEG encoder application.

- 1. Task-Level Parallelism (TLP): an application is split into set of tasks which can execute concurrently;

- 2. Data-Level Parallelism (DLP): a task of an application executes in parallel on multiple processing elements where each copy of the task processes its own data stream;

- 3. Pipeline-Level Parallelism (PLP): different iterations of a pair of data producer and consumer tasks execute in parallel.

Usually, an application contains more than one type of parallelism. Task-level parallelism is typically considered first when specifying an application as a set of concurrent tasks. Data-level parallelism is usually used by replicating tasks in an application in order to process more data in parallel and, hence, increase the application performance. However, if consecutive executions of a task depend on each other, data-level parallelism cannot be exploited and pipeline parallelism comes as an important form of parallelism to exploit. Figure 1.2 shows a Motion JPEG (MJPEG) encoder application represented as a set of communicating tasks which can execute concurrently. Here, we can identify examples of all three types of parallelism introduced above: 1) TLP between *Video in* and *Init*; 2) DLP between the two *DCT* tasks; and 3) PLP between different iterations of *VLE* and *Video out*.

It has been identified that *dataflow* MoCs are the most suitable parallel MoCs to express parallelism in streaming applications [TA10]. In a dataflow MoC, an application is represented as a *directed* graph, with graph nodes representing the application tasks and graph edges representing data dependences among the tasks. Thus, the parallelism is explicitly specified in the model. Dataflow MoCs differ among each other in their *expressiveness* and *decidability*. The expressiveness of a model indicates which type of applications can be modeled by the model and how compact the model is [SGTB11]. The

decidability of a model represents the extent to which designers can analyze liveness and performance of an application at compile-time. In general, expressiveness and decidability of MoCs are inversely related, meaning that more expressive MoCs are less decidable, and the opposite; hence the choice of a suitable MoC depends on the problem being addressed. For example, within the Daedalus<sup>RT</sup> [BZNS12] design methodology, the Cyclo-Static Dataflow MoC [BELP96] is used as an analysis model, to analyze design non-functional properties such as throughput, latency, hard real-time behavior, while the Polyhedral Process Network MoC [VNS07] is used as an implementation model. The MoCs considered in this thesis to represent streaming applications are Synchronous Data Flow (SDF) [LM87], Cyclo-Static Dataflow (CSDF) [BELP96] and Polyhedral Process Network (PPN) [VNS07], given in the order of increased expressiveness, hence decreased analyzability. Because of their very good analyzability, we use the SDF and CSDF MoCs to analyze the application throughput, latency, hard real-time behavior and calculate the required size of buffers used to implement inter-task communication. On the other hand, we use the PPN MoC to generate efficient code for processors in an MPSoC and build highly accurate energy model to analyze the energy consumption. A more detailed and complete comparison of different dataflow MoCs is given in [SGTB11].

# 1.2 Design Requirements and Basic Approaches to Meet the Requirements

In Section 1.1.2, it has been explained that model-based design methodologies have been used to design embedded streaming MPSoCs to provide the desired system performance. In this section, we introduce the requirements which are usually put on embedded streaming MPSoCs and the basic approaches proposed by research communities to meet these requirements.

### 1.2.1 Timing Requirements

As mentioned earlier, the performance of a streaming application running on an MPSoC is represented with two metrics: throughput and latency. Usually, embedded streaming MPSoCs execute simultaneously multiple applications and for each application throughput and latency requirements have to be met. In addition, these multiple applications should be **temporally isolated** between each other. This means that an application can be started or stopped at run-time without violating the timing requirements of other running applications. Beside performance requirements, many embedded streaming systems have to process data within a certain time interval, that is, before a *deadline*, meaning that they have hard real-time requirements.

In general, to provide timing guarantees for streaming applications, researchers proposed either analysis approaches on the dataflow MoCs, or they specified applications as periodic real-time tasks, or devised techniques which are mixture of the previous two. In the first case, techniques are devised to provide timing guarantees for streaming applications by performing analysis on a dataflow MoC, for example, techniques proposed in [GGS<sup>+</sup>06], [SGB08], [MB07] and [BMKdD13]. The approach in [GGS<sup>+</sup>06], [SGB08] analyzes an application modeled using the (C)SDF MoC [LM87] by performing state-space exploration of the (C)SDF graph in order to find the application throughput and latency. On the other hand, the approach in [MB07] converts an initial SDF application specification into an equivalent homogeneous SDF (HSDF) specification, and does the performance analysis on the HSDF. However, the state-space of an SDF graph is exponential in the worst case, and the conversion from an SDF into an equivalent HSDF results in an application graph which size grows exponentially in the worst case, hence the analysis approaches in [GGS<sup>+</sup>06] and [MB07] have high time complexity. The approach in [BMKdD13] does application performance analysis on a CSDF graph by formulating the problem of finding performance guarantees as an Integer Linear Programming (ILP) problem. Thus, that approach has high time complexity given that ILP-based approaches suffer from severe scalability issues. All the approaches [GGS<sup>+</sup>06], [MB07] and [BMKdD13], do not provide temporal isolation among applications and need complex design space exploration to find the minimum number of processors in a platform required to provide timing guarantees.

Another way of providing timing guarantees is by specifying applications as *classical real-time tasks* [DB11]. The classical real-time task model [LL73] specifies applications as *independent tasks*. The invocations of tasks are periodic, with constant execution time for each invocation and constant interval between invocations. By using the hard real-time schedulability theories [DB11], the minimum number of processors needed to schedule applications while providing timing guarantees, and temporal isolation between the applications can be determined in a fast analytical way. However, this classical real-time task model does not model data dependencies among tasks usually found in streaming applications.

Recently, several approaches, such as [BS11], [BS13] and [BTV12], have been proposed which combine advantages of the previously mentioned approaches by converting an application specified using a dataflow MoC, hence modeling data dependencies, to real-time tasks, thus enabling temporal isolation and fast calculation of the minimum number of processors to provide timing guarantees. Therefore, in this thesis, we utilize benefits of both dataflow MoCs and real-time task models to further improve the system timing guarantees and the utilization of hardware resources.

#### 1.2.2 Energy Requirements

As indicated in Section 1.1.1, one of the main reasons for the flattening of the performance curve across different generations of uniprocessors was the increased power consumption due to the increased clock frequency to boost performance, and the technology scaling. The idea of using MPSoC platforms partially solved the power consumption issue by allowing performance boost through parallel execution while running processors at a lower frequency. Given that the technology scaling is still one ongoing process which provides more parallel processing resources but also results in larger power dissipation, it has been identified by the International Technology Roadmap for Semiconductors (ITRS) [fSI] that the power and energy consumption are the main problems in the system design. This results in a need for design techniques which target more performance and functionality at constant power density, constrained by thermal issues, and constant energy consumption, constrained by the battery capacity. The inability to manage power dissipation limits the amount of switched-on logic content in a SoC, known as the "dark silicon" issue [EBSA<sup>+</sup>11].

Widely used techniques to reduce the power/energy consumption are Voltage-Frequency Scaling (VFS) and Power Management (PM). VFS reduces the power consumption by adjusting the voltage and operating frequency of processors while PM exploits idle times of processors by putting them to a very low-power sleep mode. In addition, according to ITRS reports, heterogeneous MPSoCs were identified as a promising solution in terms of energy-efficiency [Mit15]. Heterogeneous MPSoCs [Mit15] have been also considered as a promising solution to the dark silicon problem. Especially, the asymmetric multi-core architecture, also known as a single-ISA heterogeneous architecture, was recognized as a good trade-off in terms of energy-efficiency and programming effort [Mit15]. A single-ISA heterogeneous MPSoC consists of cores with different power-performance characteristics but with the same instruction-set architecture (ISA). Apart from containing cores with different power-performance characteristics, such heterogeneous MPSoCs cover large set of power-performance design points through voltage-frequency scaling of the cores [Mit15]. However, with the advent of many-core systems, per-core VFS becomes impractical due to the high hardware cost and area requirement [HM07]. Therefore, to balance the energy saving and the hardware cost, cores are grouped into clusters and cores in each cluster run at the same voltage and frequency level. In addition, it has been recognized by ITRS that the accuracy of power modeling and estimation has to be improved in order to manage the power consumption to extreme limits [Kah13].

# 1.3 Problem Statement

After introducing the trends and requirements in the design of embedded streaming systems in Section 1.1 and Section 1.2, in this section, we formulate the problems addressed in this thesis concerning the design of embedded streaming systems.

### 1.3.1 Problem 1

Meeting the timing requirements is one of the most important design objectives when designing embedded streaming MPSoCs. As explained in Section 1.2.1, there are several research approaches on how to guarantee the timing behavior of streaming applications. Among them, the most appropriate one is the research approach which combines the benefits of dataflow MoC-based analysis and hard real-time analysis. The existing works [BS11], [BS13], [BTV12], following this approach, assume that each execution of an application task takes the same amount of time. However, a common behavior in streaming applications is that different executions of the same application task differ in execution time. When such changing execution nature of an application is hidden by considering one and the same value for the execution time of an application task, the application throughput is underestimated, the application latency overestimated, while the processors in an MPSoC platform are underutilized. Thus, the first problem addressed in this thesis is:

Problem 1: Can we apply the hard real-time scheduling theory for real-time periodic tasks to streaming applications while considering different execution times among different executions of an application task to obtain tighter bounds on throughput and latency and better utilize processors?

### 1.3.2 Problem 2

As introduced in Section 1.1.2, streaming applications contain ample amount of parallelism and can be efficiently represented by using parallel MoCs. How-

ever, the initial parallel application specification often is not the most suitable one for a given MPSoC platform. This is because application developers mainly focus on realizing certain application behavior while the computational capacity and power consumption profile of the MPSoC platform is often not fully taken into account. That is, the initial parallel specification does not expose enough parallelism, particularly in the form of DLP, to better exploit the platform to satisfy timing and energy requirements. To better utilize the underlying MPSoC platform, the initial specification of an application, that is, the initial task graph, should be transformed to an alternative one that exposes more DLP while preserving the same application behavior. This can be achieved through an unfolding transformation where the tasks from the initial graph are replicated, in an equivalent graph, a certain number of times. Special care should be taken during the unfolding transformation to avoid all unnecessary overheads caused by data management among replicas. Moreover, having more tasks' replicas than necessary results in an inefficient system due to overheads in code and data memory, scheduling and inter-tasks communication. Thus, the right amount of DLP, depending on the underlying MPSoC platform, should be determined in a parallel application specification to achieve maximum performance and timing guarantees. Therefore, the second problem we address in this thesis consists of two sub-problems. The first sub-problem is:

Problem 2a: How to convert an initial application graph into input-output equivalent graph while avoiding unnecessary overheads caused by data management among task replicas?

The second sub-problem follows as:

Problem 2b: How many times to replicate each task in the initial application graph, such that the obtained equivalent graph exposes the right amount of parallelism that maximizes the utilization of the available processors in an MPSoC platform while meeting all timing requirements?

#### 1.3.3 Problem 3

Apart from timing requirements, energy consumption requirements are very important requirements to be met for proper functioning of embedded systems. As introduced in Section 1.2.2, the ITRS proposed heterogeneous parallel processing and frequency islands as design innovations to address the power/energy consumption requirements. In particular, the asymmetric multi-core architecture was recognized by both academia and industry as a good platform for design of energy-efficient embedded systems. Some examples of commercial asymmetric cluster MPSoCs are Samsung Exynos 5 Octa

SoC [Samb], nVidia Tegra X1 [NVI15], which include ARM big.LITTLE [Gre11] integrating high-performance cores into big clusters and low-power cores into LITTLE clusters. As mentioned in Section 1.3.2, when developing an application, application designers often do not have the timing and energy behavior of a platform in mind. Hence, it may happen that an application consists of highly imbalanced tasks in terms of the task workload, that is, task utilization. Especially, in cluster heterogeneous MPSoCs, when several tasks are mapped onto the same cluster, the task with the heaviest utilization will determine the required voltage and frequency of the whole cluster and will significantly increase the energy consumption of the other tasks mapped on the same cluster. When task replication, that is, DLP, is applied to application tasks with heavy utilization, their utilization can be decreased while still providing the same application performance. Thus, the third problem, we address in this thesis is: Problem 3: How to map embedded streaming applications under timing requirements by utilizing per-cluster VFS and task replication to reduce the energy consumption of a system?

#### 1.3.4 Problem 4

It was pointed out by ITRS that the accuracy of power/energy modeling is very important for efficient power/energy management [Kah13]. Model accuracy is usually traded-off for modeling and evaluation effort. Energy models used with more analyzable functional models, that is, MoCs, are usually more abstract in order to be more efficient in terms of modeling and evaluation effort and time, hence they try to capture the worst-case energy consumption. Such a model of the energy consumption results in safe but not very accurate estimates when compared with the actual energy consumption measurements on real implementations. Hence, an energy model should be more closely related to the actual running system yet be enough efficient in terms of modeling and evaluation effort and time. More expressive MoCs, as the PPN MoC for example, can give better insight of the final implementation of application tasks on a platform, hence they are often used as implementation models. However, providing timing guarantees by doing analysis on the PPN MoC is rather difficult, if not impossible [Zha15], hence the PPN MoC is used in systems where the timing requirements are not necessarily specified but it is required that the system runs at the best of its capacity (best-effort systems). Therefore, as the forth problem, we investigate:

Problem 4: How to model as accurately as possible the energy consumption of a mapping of an application onto an MPSoC platform while such a system runs at the best of its capacity?

## 1.4 Research Contributions

By addressing the research problems outlined in Section 1.3, in this section, we summarize the research contributions of this thesis.

Contribution 1: Proposing a scheduling approach which converts dataflow MoCs to real-time periodic tasks while considering different execution times for different executions of an application task.

To address the first problem, namely, Problem 1 in Section 1.3.1, we propose a scheduling approach, published in [SLCS15] and [SLCS16], and presented in Chapter 3, to schedule streaming applications modeled as acyclic CSDF graphs on an MPSoC platform. The proposed approach converts each task in a CSDF graph to a set of real-time periodic tasks by deriving task parameters (periods, start times, and deadlines) while considering different execution times for different executions of each task in the CSDF graph. The conversion enables application of many hard real-time scheduling algorithms which offer fast calculation of the required number of processors for scheduling the tasks with a certain guaranteed throughput and latency. In addition, the proposed approach calculates the minimum buffer sizes of the communication channels between the tasks in the CSDF graph such that the converted tasks can be scheduled as periodic real-time tasks. As part of our scheduling approach, we propose a method to reduce the graph latency by carefully selecting the deadlines of the converted real-time periodic tasks. We show, on a set of real-life streaming applications, that our approach leads to equal or higher application throughput and shorter application latency while reducing the number of processors required to schedule a given application, compared to a related approach which does not consider different execution times for different executions of CSDF tasks. However, our approach results in increased memory requirements to implement the communication among the tasks.

#### Contribution 2: Proposing a graph transformation and an approach that uses the transformation to exploit the right amount of parallelism that maximizes the utilization of the available processors in an MPSoC platform while meeting all timing requirements.

We address the second problem, Problem 2a-2b stated in Section 1.3.2, by proposing an unfolding graph transformation for SDF graphs and an algorithm that adapts the exploited parallelism in an application modeled using the SDF MoC according to the resources in an MPSoC by using the unfolding transformation and the hard-real time scheduling approach of CSDF graphs devised within Contribution 1 such that the application performance is maximized and hard real-time behavior guaranteed. Our contribution has been published in [SLS16b] and explained in Chapter 4. In particular, our unfolding

graph transformation carefully distributes data among task replicas, enabling more parallel execution of tasks, and our algorithm determines simultaneously which SDF tasks and how many times to replicate them, and the allocation of tasks to processors in the MPSoC. We show, on a set of real-life streaming applications, that our unfolding graph transformation for SDF graphs results in graphs with the same application throughput, shorter application latency and smaller communication memory compared to related approaches. In addition, we show that our algorithm delivers, in 98% of the conducted experiments, a solution with a shorter latency, smaller communication memory and smaller values for task replication factors compared to a related approach while the same performance and timing requirements are satisfied.

#### Contribution 3: Proposing an approach that exploits the right amount of parallelism in an application and per-cluster VFS to map the application onto a cluster heterogeneous MPSoC such that the energy consumption is minimized and all timing requirements met.

In our third contribution which addresses Problem 3 in Section 1.3.3, we propose a novel algorithm [SLS16a], presented in Chapter 5, to efficiently map real-time streaming applications onto cluster heterogeneous MPSoCs, which are subject to throughput constraints, such that the energy consumption of the cluster heterogeneous MPSoC is reduced by using task replication and per-cluster VFS. By using the hard real-time scheduling approach of CSDF graphs, we devised within Contribution 1, we propose an efficcient way to determine a suitable processor type for each task in an (C)SDF graph such that the energy consumption is minimized and the throughput constraint is met. Then, by using our unfolding graph transformation, devised within Contribution 2, we propose a method to determine a replication factor for each task in an SDF graph such that the distribution of the workload on the same type of processors is balanced, which enables processors to run at a lower frequency, hence reducing the energy consumption. We show, on a set of real-life streaming applications, that our proposed energy minimization approach outperforms related approaches in terms of energy consumption while meeting the same throughput constraints.

Contribution 4: Proposing an accurate energy model for best-effort streaming applications mapped onto heterogeneous MPSoC platforms. To address the problem of accurate power/energy modeling, namely, Problem 4 in Section 1.3.4, we devise an accurate energy model [SS13] for streaming applications modeled by the PPN MoC and mapped onto heterogeneous MP-SoC platforms. The energy model is based on the well-defined properties of the PPN application model. To guarantee the accuracy of the energy model,

values of important model parameters are obtained by real measurements. In addition, our energy model can model different types of communication infrastructures: with and without contention. The accuracy of the proposed energy model is evaluated on FPGA-based MPSoC platforms running two real-life streaming applications against real measurements of the energy consumption from the FPGA. The model and its accuracy and efficiency is presented in Chapter 6.

### 1.5 Thesis Outline

Below we give an outline of this thesis, summarizing the contents of the following chapters.

Chapter 2 gives an overview of the dataflow MoCs considered in this thesis, and some techniques from hard-real time scheduling theories relevant for this thesis.

Chapters 3 to 6 contain the contributions of this thesis. Each chapter is organized in a self-contained way, meaning that each chapter contains more specific introduction to the problem addressed, related work, the proposed solution approach, experimental evaluation, and concluding discussion.

Chapter 3 presents our hard real-time scheduling approach for streaming applications modeled as acyclic CSDF graphs.

Chapter 4 describes our unfolding graph transformation for SDF graphs and our algorithm for finding proper replication factors for each task in an SDF graph, which uses our scheduling framework described in Chapter 3, such that the processing resources are utilized as best as possible, while providing hard real-time guarantees.

Chapter 5 presents our energy-minimization approach which uses our scheduling framework described in Chapter 3 and our unfolding transformation described in Chapter 4 to find task-to-processor type assignment and task replication factors such that the energy consumption is minimized.

Chapter 6 presents our accurate energy model for streaming applications modeled using the PPN MoC and mapped onto MPSoC platforms.

Chapter 7 ends this thesis by providing conclusions regarding the work done within this thesis and discussions on potential future work.

# **Chapter 2**

# Background

THIS chapter introduces the background necessary to understand the contribution of this thesis presented in the following chapters. First, we give in Table 2.1 a summary of the mathematical notations used throughout the thesis. Then, we present the dataflow models considered in this thesis in Section 2.1, while some results from the hard real-time scheduling theory relevant for this thesis are presented in Section 2.2.

| Symbol         | Meaning                                   |

|----------------|-------------------------------------------|

| $\mathbb{N}$   | The set of natural numbers excluding zero |

| $\mathbb{N}_0$ | $\mathbb{N} \cup \{0\}$                   |

| Z              | The set of integers                       |

| <i>x</i>       | The cardinality (size) of a set $x$       |

| x              | The maximum value of <i>x</i>             |

| ž              | The minimum value of <i>x</i>             |

| lcm            | The least common multiple operator        |

| mod            | The integer modulo operator               |

**Table 2.1:** Summary of mathematical notations

## 2.1 Dataflow Models-of-Computations (MoCs)

As mentioned earlier in Section 1.1.2, dataflow MoCs have been used to efficiently express parallelism in streaming applications. In this section, we present the dataflow MoCs considered in this thesis, that is, the CSDF and SDF MoCs are given in Section 2.1.1, and the PPN MoC is given in Section 2.1.2. The CSDF MoC is used to specify streaming applications within the hard real-time scheduling framework proposed in Chapter 3. The SDF MoC is used to specify the input streaming applications in the techniques which exploit parallelism in streaming applications to maximize the resource utilization and minimize the energy consumption, presented in Chapters 4 and 5, respectively. The PPN MoC is used to specify streaming applications within the solution for highly accurate modeling of energy consumption, presented in Chapter 6.

### 2.1.1 Cyclo-Static Dataflow (CSDF)

An application modeled as a CSDF [BELP96] is a directed graph  $G = (\mathcal{V}, \mathcal{E})$  that consists of a set of actors  $\mathcal{V}$  which communicate with each other through a set of communication channels  $\mathcal{E}$ . Actors represent a certain functionality of the application, while communication channels are first-in first-out (FIFO) buffers representing data dependencies and transferring *data tokens* between the actors. A data token is an atomic data object belonging to a stream of data transferred between the actors. We can associate each actor  $v_i \in \mathcal{V}$  in a graph with two sets of actors, the *predecessors set*, denoted by  $\operatorname{prec}(v_i)$ , and the *successors set*, denoted by  $\operatorname{succ}(v_i)$ . These sets are given by:

$$\operatorname{prec}(v_i) = \{ v_i \in \mathcal{V} : \exists e_u = (v_i, v_i) \in \mathcal{E} \}$$

$$(2.1)$$

$$\operatorname{succ}(v_i) = \{ v_j \in \mathcal{V} : \exists e_u = (v_i, v_j) \in \mathcal{E} \}$$

$$(2.2)$$

In addition, we can define for each actor  $v_i \in \mathcal{V}$  in a graph two sets of communication channels, the *input set*, denoted by  $inp(v_i)$ , and the *output set*, denoted by  $out(v_i)$ . The *input set* contains all the input channels to  $v_i$ , while the *output set* contains all the output channels from  $v_i$ . If an actor  $v_i$  receives an input data stream from the environment then  $v_i$  is called *input actor*, and  $v_i$  does not have input channels, that is,  $inp(v_i) = \emptyset$ . Similarly, if an actor  $v_i$  produces an output data stream for the environment then  $v_i$  is called *output actor*, and  $v_i$ does not have output channels, that is,  $out(v_i) = \emptyset$ . A *path*  $w_{i \to j}$  between actors  $v_i$  and  $v_j$  is an ordered sequence of channels connecting  $v_i$  and  $v_j$  denoted as  $w_{i \to j} = \{(v_i, v_k), (v_k, v_l), \cdots, (v_m, v_j)\}$ .

Every actor  $v_i \in \mathcal{V}$  has an *execution sequence*  $[F_i(1), F_i(2), \dots, F_i(\phi_i)]$ of length  $\phi_i$ , that is, it has  $\phi_i$  phases. The *k*th time that actor  $v_i$  is fired, it executes the function  $F_i(((k-1) \mod \phi_i) + 1)$ . As a consequence, the execution time of actor  $v_i$  is also a sequence  $[C_i^C(1), C_i^C(2), \dots, C_i^C(\phi_i)]$  consisting of the worst-case computation time values for each phase. Similarly, every output channel  $e_u$  of an actor  $v_i$  has a predefined token *production sequence*  $[x_i^u(1), x_i^u(2), \dots, x_i^u(\phi_i)]$  of length  $\phi_i$ . Analogously, token consumption on every input channel  $e_u$  of an actor  $v_i$  is a predefined se-

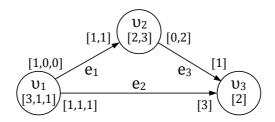

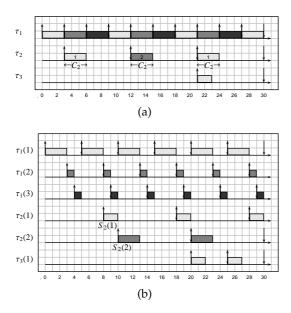

Figure 2.1: A CSDF graph G.

quence  $[y_i^u(1), y_i^u(2), \dots, y_i^u(\phi_i)]$ , called *consumption sequence*. The total number of tokens on a channel  $e_u$  produced by  $v_i$  during its first n invocations and the total number of tokens consumed on the same channel by  $v_j$  during its first n invocations are  $X_i^u(n) = \sum_{l=1}^n x_i^u(((l-1) \mod \phi_l) + 1)$  and  $Y_j^u(n) = \sum_{l=1}^n y_j^u(((l-1) \mod \phi_l) + 1)$ , respectively.

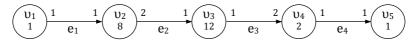

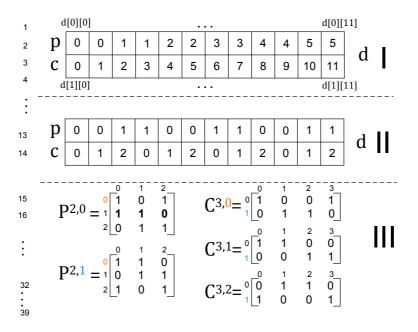

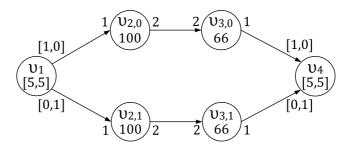

Figure 2.1 shows an example of a CSDF graph. For instance, actor  $v_1$  has 3 phases, that is,  $\phi_1 = 3$ , its execution time sequence (in time units) is  $[C_1^C(1), C_1^C(2), C_1^C(3)] = [3, 1, 1]$  and its token production sequence on channel  $e_1$  is [1, 0, 0].

An acyclic CSDF graph can be partitioned into a number of *levels*, denoted by *L*, in a way similar to topological sort. In that way, all input actors belong to level-1, the actors from level-2 have all immediate predecessors in level-1, the actors from level-3 have immediate predecessors in level-2 and can also have immediate predecessors in level-1, and so on.

An important property of the CSDF model is the ability to derive, at design time, a schedule for the actors. In order to derive a valid static schedule for a CSDF graph at design time, it has to be consistent and live.

**Theorem 2.1.1** (From [BELP96]). In a CSDF graph G, a repetition vector  $\vec{q} = [q_1, q_2, \dots, q_N]^T$  is given by

$$\vec{q} = \mathbf{\Phi} \cdot \vec{r}, \quad with \quad \Phi_{jk} = \begin{cases} \phi_j & \text{if } j = k \\ 0 & \text{otherwise} \end{cases}$$

(2.3)

where  $\vec{r} = [r_1, r_2, \cdots, r_N]^T$  is a positive integer solution of the balance equation

$$\mathbf{\Gamma} \cdot \vec{r} = \vec{0} \tag{2.4}$$

and where the topology matrix  $\Gamma \in \mathbb{Z}^{|\mathcal{E}| \times |\mathcal{V}|}$  is defined by

$$\Gamma_{uj} = \begin{cases} X_j^u(\phi_j) & \text{if actor } v_j \text{ produces on channel } e_u \\ -Y_j^u(\phi_j) & \text{if actor } v_j \text{ consumes from channel } e_u \\ 0 & \text{otherwise.} \end{cases}$$

(2.5)

A CSDF graph *G* is said to be consistent if a positive integer solution  $\vec{r} = [r_1, r_2, \dots, r_N]^T$  exists for the balance equation, Equation (2.4). We call  $\vec{r}$  aggregated repetition vector. The smallest non-trivial aggregated repetition vector  $\vec{r}$  is called *basic aggregated repetition vector*  $\vec{r}$ . Its corresponding repetition vector  $\vec{q}$  is called *basic repetition vector*  $\vec{q}$ . If a deadlock-free schedule can be found, *G* is said to be live.

**Definition 2.1.1.** For a consistent and live CSDF graph *G*, an **actor iteration** is the invocation of an actor  $v_i \in \mathcal{V}$  for  $q_i$  times, a **phase iteration** is the invocation of one phase of an actor  $v_i \in \mathcal{V}$  for  $r_i$  times, and a **graph iteration** is the invocation of *every actor*  $v_i \in \mathcal{V}$  for  $q_i$  times, where  $q_i \in \vec{q}$ , and *every phase* of *every actor*  $v_i \in \mathcal{V}$  for  $r_i \in \vec{r}$ .

For the example CSDF graph *G* shown in Figure 2.1, we can compute the basic repetition vectors  $\vec{r}$  and  $\vec{q}$  by using the equations in Theorem 2.1.1, namely, Equations (2.3), (2.4) and (2.5), as follows:

$$\Gamma = \begin{bmatrix} 1 & -2 & 0 \\ 3 & 0 & -3 \\ 0 & 2 & -1 \end{bmatrix}, \vec{r} = \begin{bmatrix} 2 \\ 1 \\ 2 \end{bmatrix}, \mathbf{\Phi} = \begin{bmatrix} 3 & 0 & 0 \\ 0 & 2 & 0 \\ 0 & 0 & 1 \end{bmatrix}, \text{ and } \vec{q} = \begin{bmatrix} 6 \\ 2 \\ 2 \end{bmatrix}.$$

Two important subsets of the CSDF MoC are the Synchronous Data Flow (SDF) MoC [LM87] and the Homogeneous Synchronous Data Flow (HSDF) MoC [LM87]. All actors in an SDF graph  $G = (\mathcal{V}, \mathcal{E})$  have only one phase, that is, for each  $v_i \in \mathcal{V}, \phi_i = 1$ . In an HSDF graph  $G = (\mathcal{V}, \mathcal{E})$ , in addition to  $\forall v_i \in \mathcal{V}, \phi_i = 1$ , all channels have production and consumption sequences equal to 1, that is, for each  $e_u = (v_i, v_j) \in \mathcal{E}, x_i^u = [x_i^u(1)] = 1, y_i^u = [y_i^u(1)] = 1$ .

### 2.1.2 Polyhedral Process Network (PPN)

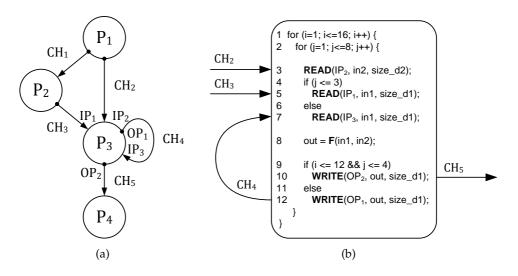

An application modeled as a PPN [VNS07] is a directed graph  $G = (\mathcal{P}, \mathcal{C})$  that consists of a set of processes  $\mathcal{P}$ , which communicate with each other via a set of communication channels  $\mathcal{C}$ . Processes in  $\mathcal{P}$  represent tasks of an application. Channels in  $\mathcal{C}$  are bounded FIFOs and represent one direction of data communication between two processes, that is, a channel  $CH_l = (P_i, P_j)$  represents a data dependency between processes  $P_i$  and  $P_j$ , where  $P_i$  is the producer and  $P_j$  is the consumer process. An example of a PPN consisting of 4 processes which communicate with each other through 5 channels is given in Figure 2.2(a). Each PPN process has a set of *input ports* it reads from and a set of *output ports* it writes to. Process  $P_3$  in the PPN example in Figure 2.2(a) has 3 input ports  $IP_1$ ,  $IP_2$ , and  $IP_3$ , and 2 output ports  $OP_1$  and  $OP_2$ . Channels of a

**Figure 2.2:** *Example of a PPN (a) and the structure of process P3 (b).*

process  $P_i$  connected to its input ports are *input channels* of  $P_i$ , while channels connected to the output ports of  $P_i$  are *output channels* of  $P_i$ .

The synchronization mechanism between the processes in the PPN MoC is *blocking read* from an empty FIFO and *blocking write* to a full FIFO. The execution of a PPN process is defined by using nested *for loops*, that is, the process execution is a set of iterations, called *process domain*. The process domain is represented using the polytope model [Fea96a]. Each PPN process has a precisely defined structure: the process reads data from a subset of its input ports depending on the values of loop iterators; then, it performs a computation on input data that generates output data; and finally, the process writes the output data through a subset of its output ports depending on the values of loop iterators.

Figure 2.2(b) shows the structure of process  $P_3$  in the PPN example given in Figure 2.2(a). Process  $P_3$  reads data from and writes data to channels through read and write primitives **READ**(···) and **WRITE**(···), respectively. The computation behavior of process  $P_3$  is represented by a function **F**(···) in Line 8 in Figure 2.2(b). The process domain of process  $P_3$  is given as the polytope  $D_{P_3} = \{(i, j) \in \mathbb{Z}^2 \mid 1 \le i \le 16 \land 1 \le j \le 8\}$ . Accessing an input port of the PPN process is represented as a subset of the process domain, called *input port domain*. Similarly, accessing an output port of the PPN process is represented through *output port domain*. Process  $P_3$  in Figure 2.2 reads data from input ports  $IP_1$ ,  $IP_2$  and  $IP_3$ . The input port domain of input port  $IP_2$  is equal to process domain  $D_{P_3}$ , while the input port domain of port  $IP_1$  is given as  $D_{IP_1} = \{(i, j) \in \mathbb{Z}^2 \mid 1 \le i \le 16 \land 1 \le j \le 3\}$ . Process  $P_3$  writes data to output ports  $OP_1$  and  $OP_2$ . Domain  $D_{OP_2} = \{(i, j) \in \mathbb{Z}^2 \mid 1 \le i \le 12 \land 1 \le j \le 4\}$  is the output port domain of port  $OP_2$ .

### 2.2 Real-Time Scheduling Theory

In this section, we introduce the real-time periodic task model [DB11] and some important real-time scheduling concepts [DB11] instrumental to the approaches we present in Chapters 3, 4 and 5 of this thesis.

### 2.2.1 Task Model

The majority of the research on real-time scheduling considers a simple model to represent applications running on a hardware platform. In this simple model applications are modeled as a task set  $\mathcal{T} = \{\tau_1, \tau_2, \cdots, \tau_n\}$  of *n* periodic tasks, which can be preempted at any time. A periodic task  $\tau_i \in \mathcal{T}$  is defined by the 4-tuple  $\tau_i = (S_i, C_i, D_i, T_i)$ , where  $S_i$  is the start time of  $\tau_i$  in absolute time units,  $C_i$  is the worst-case execution time (WCET),  $D_i$  is the deadline of  $\tau_i$ in relative time units, and  $T_i$  is the task period in relative time units, where  $C_i \leq D_i \leq T_i$ . Each task  $\tau_i$  executes periodically through a sequence of task invocations, that is, *job releases*, at  $s_{i,k} = S_i + kT_i$ ,  $k \in \mathbb{N}_0$ . Once released, each job  $\tau_{i,k}$ ,  $k \in \mathbb{N}_0$ , of a task  $\tau_i$  must execute  $C_i$  time units before  $s_{i,k} + D_i$ , that is, the job must finish its execution before its deadline  $D_i$ . If  $D_i = T_i$ , then  $\tau_i$  is said to have an *implicit-deadline*. Otherwise, if  $D_i < T_i$ , then  $\tau_i$  is said to have a *constrained-deadline*. If all the tasks in a task set T are implicit-deadline periodic tasks, then task set  $\mathcal{T}$  is an *implicit-deadline periodic* (IDP) *task set*. Otherwise, task set  $\mathcal{T}$  is a constrained-deadline periodic (CDP) task set. Similarly, if all the tasks in a task set  $\mathcal{T}$  have the same start time, then task set  $\mathcal{T}$  is *synchronous*. Otherwise, task set  $\mathcal{T}$  is *asynchronous*. In this thesis, we consider asynchronous task sets.

The **utilization** of task  $\tau_i$ , denoted as  $u_i$ , where  $u_i \in (0, 1]$ , is defined as  $u_i = C_i/T_i$ . For a task set  $\mathcal{T}$ ,  $u_{\mathcal{T}}$  is the total utilization of  $\mathcal{T}$  given by  $u_{\mathcal{T}} = \sum_{\tau_i \in \mathcal{T}} u_i$ . Similarly, the **density** of task  $\tau_i$  is  $\delta_i = C_i/D_i$  and the total density of  $\mathcal{T}$  is  $\delta_{\mathcal{T}} = \sum_{\tau_i \in \mathcal{T}} \delta_i$ . The worst-case response time of task  $\tau_i$ , denoted as  $R_i$ , is defined as the longest time interval from the arrival of a job of task  $\tau_i$ to the completion of job's execution.

The *processor demand bound function* of a task set  $\mathcal{T}$  over a time interval  $[t_1, t_2]$  represents the maximum amount of task execution that can be released

and completed in the time interval  $[t_1, t_2]$ , and is given by [BRH90]:

$$dbf(\mathcal{T}, t_1, t_2) = \sum_{\tau_i \in \mathcal{T}} \max\{0, \left\lfloor \frac{t_2 - S_i - D_i}{T_i} \right\rfloor - \max\{0, \left\lceil \frac{t_1 - S_i}{T_i} \right\rceil\} + 1\} \cdot C_i.$$

(2.6)

### 2.2.2 System Model

To present the important results from the real-time scheduling theory relevant for this thesis, we consider a system composed of a set  $\Pi = \{\pi_1, \pi_2, \dots, \pi_m\}$  of *m* identical processors. However, our contribution approaches, presented in this thesis, are applicable to both homogeneous and heterogeneous MPSoCs, because the processor heterogeneity is captured within the WCET of a task, which will be explained in more detail in Chapter 5. Thus, the results presented in the following section, Section 2.2.3, are applicable to heterogeneous MPSoCs as well.

### 2.2.3 Real-Time Scheduling Algorithms

In this section, we present some important scheduling concepts for scheduling applications modeled as real-time periodic tasks, introduced in Section 2.2.1, on a system modeled as described in Section 2.2.2.

Real-time scheduling algorithms for multiprocessors try to solve two problems [DB11]:

- The *allocation problem*, that is, on which processor a task should execute.

- The *priority problem*, that is, when and in which order each job of a task should execute with respect to jobs of other tasks.

Depending on how they solve the *allocation problem*, scheduling algorithms are classified into:

- *No migration*. Each task is allocated to one processor and no migration is allowed.

- *Task-level migration*. The jobs of a task can execute on different processors. However, each job can execute only on one processor.

- *Job-level migration*. A job can migrate and execute on different processors. However, parallel execution of a job on processors is not allowed.

Scheduling algorithms that allow any job to migrate are called **global** algorithms. On the other hand, algorithms which do not allow migration are called **partitioned** algorithms. Finally, scheduling algorithms that allow migration of jobs released by a subset of tasks among a subset of processors are called **hybrid** algorithms.

Depending on how they solve the *priority problem*, scheduling algorithms are classified into:

- *Fixed task priority*. Each task has a single fixed priority shared by all its jobs. Examples of this class are the Rate Monotonic (RM) [LL73] and the Deadline Monotonic (DM) [LW82] scheduling algorithms.

- *Fixed job priority*. The jobs of a task may have different priorities, but each job has a single static priority. An example of this class is the Earliest Deadline First (EDF) scheduling algorithm [LL73].

- *Dynamic priority*. A single job may have different priorities during its execution. An example of this class is the Least Laxity First (LLF) scheduling algorithm [Leu89], [DK89].