## **Estimation and Optimization of the Performance of Polyhedral Process Networks**

Haastregt, S. van

## Citation

Haastregt, S. van. (2013, December 17). Estimation and Optimization of the Performance of Polyhedral Process Networks. Retrieved from https://hdl.handle.net/1887/22911

| Version:         | Corrected Publisher's Version                                                                                                          |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| License:         | <u>Licence agreement concerning inclusion of doctoral thesis in the</u><br><u>Institutional Repository of the University of Leiden</u> |

| Downloaded from: | https://hdl.handle.net/1887/22911                                                                                                      |

Note: To cite this publication please use the final published version (if applicable).

Cover Page

# Universiteit Leiden

The handle <u>http://hdl.handle.net/1887/22911</u> holds various files of this Leiden University dissertation.

Author: Haastregt, Sven Joseph Johannes van

**Title:** Estimation and optimization of the performance of polyhedral process networks **Issue Date:** 2013-12-17

# Estimation and Optimization of the Performance of Polyhedral Process Networks

Sven van Haastregt

## Estimation and Optimization of the Performance of Polyhedral Process Networks

Proefschrift

ter verkrijging van de graad van Doctor aan de Universiteit Leiden, op gezag van Rector Magnificus prof.mr. C.J.J.M. Stolker, volgens besluit van het College voor Promoties te verdedigen op dinsdag 17 december 2013 klokke 12:30 uur

door

Sven van Haastregt geboren te Rijpwetering in 1985

### Samenstelling promotiecommissie:

| promotor<br>co-promotor | Prof.dr. Ed Deprettere<br>Dr. Bart Kienhuis                                                  |                               |

|-------------------------|----------------------------------------------------------------------------------------------|-------------------------------|

| overige leden:          | Prof.dr. Joost Kok<br>Prof.dr. Harry Wijshoff<br>Prof.dr. Koen Bertels<br>Dr. Hristo Nikolov | Technische Universiteit Delft |

This manuscript was edited by the author using Vim, and typeset using  $\text{LAT}_{\text{EX}} 2_{\varepsilon}$ , BiBTEX, and *MakeIndex* in a process automated using GNU Make. Graphics were produced mostly using Inkscape, and occasionally using Xfig or gnuplot. Git over ssh was used for revision tracking, synchronization, and backup purposes.

Cover design by Marcel IJssennagger.

Estimation and Optimization of the Performance of Polyhedral Process Networks Sven van Haastregt. -Thesis Universiteit Leiden. - With index, ref. - With summary in Dutch 190 pages, 47988 words, 176 index entries, 162 references. ISBN 978-94-6182-383-0

Copyright ©2013 by Sven van Haastregt, Leiden, The Netherlands.

All rights reserved. No part of the material protected by this copyright notice may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying, recording or by any information storage and retrieval system, without permission from the author. Printed in the Netherlands.

# CONTENTS

| Co | ntent | ts                                          | vii |

|----|-------|---------------------------------------------|-----|

| No | tatio | n                                           | xi  |

| 1  | Intro | oduction                                    | 1   |

|    | 1.1   | Problem Context                             | 1   |

|    | 1.2   | Problem Statement                           | 4   |

|    | 1.3   | Related Work                                | 7   |

|    |       | 1.3.1 High-Level Synthesis                  | 8   |

|    |       | 1.3.2 Electronic System-Level Synthesis     | 10  |

|    | 1.4   | Contributions and Outline                   | 12  |

| 2  | Bacl  | kground                                     | 15  |

|    | 2.1   | Polyhedral Model                            | 15  |

|    | 2.2   | Models of Computation                       | 21  |

|    |       | 2.2.1 Homogeneous Synchronous Dataflow      | 22  |

|    |       | 2.2.2 Synchronous Dataflow                  | 23  |

|    |       | 2.2.3 Cyclo-Static Dataflow                 | 25  |

|    |       | 2.2.4 Polyhedral Process Networks           | 27  |

|    | 2.3   | Derivation of PPNs from Sequential Programs | 30  |

|    |       | 2.3.1 Channel Type Determination            | 31  |

|    |       | 2.3.2 Buffer Size Computation               | 32  |

|    | 2.4   | Code Generation                             | 33  |

|    |       | 2.4.1 Integrating Dedicated IP Cores        | 34  |

| 3  | Synt  | thesizing PPNs                              | 37  |

|    | 3.1   | Motivation & Contributions                  | 37  |

|    | 3.2   | IP Core Characterization                    | 38  |

|    |       | 3.2.1 IP Core Integration                   | 39  |

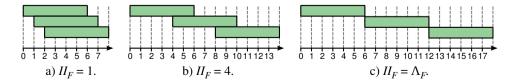

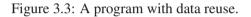

|   | 3.3  | Data Reuse                                    | 0  |

|---|------|-----------------------------------------------|----|

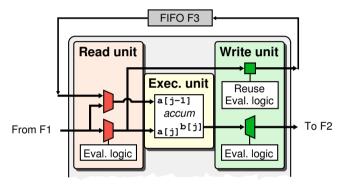

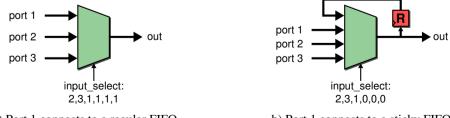

|   | 3.4  | Sticky FIFOs                                  | 2  |

|   | 3.5  | Evaluation Logic Optimizations                | 3  |

|   |      | 3.5.1 Pipelined Evaluation Logic              | 4  |

|   |      | 3.5.2 ROM-Based Evaluation Logic              | 4  |

|   |      |                                               | 17 |

|   | 3.6  | Out-of-Order Communication                    | 8  |

|   | 3.7  | Conclusion and Summary                        | 52 |

| 4 | Perf | formance Estimation 5                         | 53 |

|   | 4.1  | Motivation                                    | 53 |

|   | 4.2  | Definitions                                   | 55 |

|   | 4.3  | RTL Simulation                                | 57 |

|   | 4.4  | SystemC Simulation                            | 57 |

|   |      |                                               | 58 |

|   |      | 4.4.2 Light-weight Timed SystemC Simulation 6 | 50 |

|   | 4.5  | Maximum Cycle Mean Analysis                   | 51 |

|   |      | 4.5.1 Related Work                            | 51 |

|   |      |                                               | 53 |

|   |      |                                               | 64 |

|   |      |                                               | 2  |

|   | 4.6  |                                               | 75 |

|   |      | 4.6.1 Related Work                            | 6  |

|   |      |                                               | 7  |

|   |      |                                               | 34 |

|   |      | -                                             | 35 |

|   |      | ÷ .                                           | 35 |

|   |      |                                               | 0  |

|   |      | 4.6.7 Instrumentation Overhead                | 92 |

|   | 4.7  |                                               | 94 |

|   | 4.8  | -                                             | 96 |

|   |      | •                                             | 97 |

|   |      |                                               | 98 |

|   | 4.9  |                                               | 99 |

| 5 | App  | lication Transformation 10                    | )1 |

| - | 5.1  | Transformations                               |    |

|   |      | 5.1.1 Splitting                               |    |

|   |      | 5.1.2 Merging                                 |    |

|   |      |                                               |    |

|    |                                                                     | 1 8                      | 106 |  |  |  |

|----|---------------------------------------------------------------------|--------------------------|-----|--|--|--|

|    | 5.0                                                                 | e                        | 109 |  |  |  |

|    | 5.2                                                                 | 5 5                      | 116 |  |  |  |

|    |                                                                     |                          | 116 |  |  |  |

|    |                                                                     |                          | 120 |  |  |  |

|    |                                                                     | 1 8                      | 121 |  |  |  |

|    |                                                                     | e                        | 124 |  |  |  |

|    | 5.3                                                                 | Conclusion and Summary   | 127 |  |  |  |

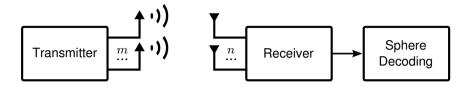

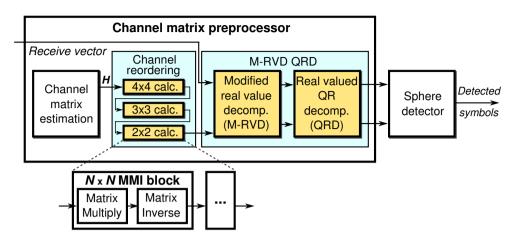

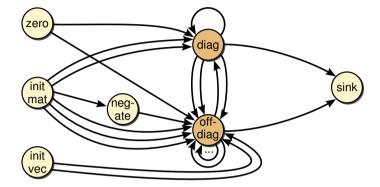

| 6  | Indu                                                                | istrial Case Study       | 129 |  |  |  |

|    | 6.1                                                                 | Sphere Decoding          | 129 |  |  |  |

|    | 6.2                                                                 | Reference Implementation | 131 |  |  |  |

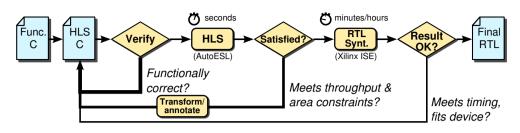

|    | 6.3                                                                 | AutoESL                  | 132 |  |  |  |

|    |                                                                     | 6.3.1 Design Flow        | 133 |  |  |  |

|    |                                                                     | 6.3.2 Design Entry       | 134 |  |  |  |

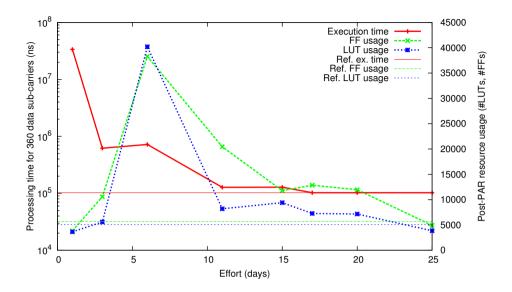

|    |                                                                     |                          | 138 |  |  |  |

|    | 6.4                                                                 |                          | 140 |  |  |  |

|    |                                                                     | 6.4.1 Design Entry       | 141 |  |  |  |

|    |                                                                     | ÷ •                      | 147 |  |  |  |

|    | 6.5                                                                 |                          | 148 |  |  |  |

|    | 6.6                                                                 |                          | 149 |  |  |  |

| 7  | Con                                                                 | clusions                 | 151 |  |  |  |

| Sa | Samenvatting<br>Curriculum Vitae<br>Acknowledgments<br>Bibliography |                          |     |  |  |  |

| Cı |                                                                     |                          |     |  |  |  |

| Ac |                                                                     |                          |     |  |  |  |

| Bi |                                                                     |                          |     |  |  |  |

| In | Index                                                               |                          |     |  |  |  |

## NOTATION

- $\begin{array}{ll} |\cdot| & \text{Cardinality: } |\mathcal{S}| \equiv \text{the number of elements in } \mathcal{S}, \text{ page 20.} \\ \hline [\cdot, \cdot) & \text{Interval: } [a, b) = \{x \in \mathbb{Z} \mid a \leq x < b\}. \end{array}$

- $\left[\cdot\right] \qquad \text{Least integer: } \left[x\right] = n \Leftrightarrow n \in \mathbb{N} \land n 1 < x \le n.$

- $\cdot \prec \cdot$  Lexicographical order, page 18.

- $D_p$  Iteration domain of process p, page 27.

- d(e) Number of initial tokens on edge e, page 22.

- $\delta_c$  Process reading from channel *c*, page 27.

- $\mathcal{E}$  The set of channels of a PPN, page 27.

- $II_F$  Initiation interval of function F, page 38.

- $IPD_i^k$  k-th Input Port Domain of process *i*, page 27.

- $\Lambda_F$  Latency (input-to-output delay) of function F, page 38.

- $M_c$  Channel relation of channel *c*, page 27.

- $\mathbb{N}$  The set of natural numbers, including 0.

- $\mathbb{N}^+$  The set of positive natural numbers, excluding 0.

- $OPD_i^k$  k-th Output Port Domain of process i, page 27.

- $\mathcal{P}$  The set of processes of a PPN, page 27.

- $\mathbb{Q}$  The set of rational numbers.

- $\sigma_c$  Process writing to channel *c*, page 27.

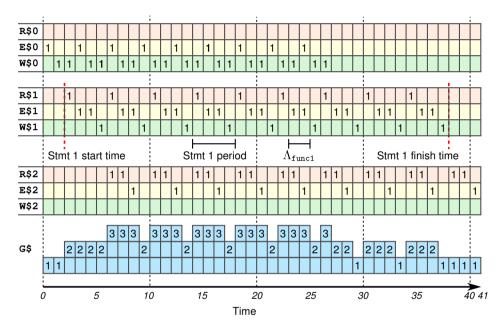

- $T_p$  Period of a process p, page 55.

- t(a) Execution time of data flow node a, page 22.

- $\tau_p$  Throughput of a process p, page 55.

- $\theta(\mathbf{i})$  Application of schedule  $\theta$  to iteration vector  $\mathbf{i}$ , pages 111, 112.

- $\mathbb{Z}$  The set of integers.

## INTRODUCTION

**E** LEMENT NUMBER 14, or silicon, has been important for many ancient civilizations, albeit mostly as a constituent of sand and rocks. Silicon was essential for the construction of houses, temples, and roads, which together formed the centers of society. In 1954, a new and very different use for silicon was found that would have a dramatic impact on the established centers of society: Gordon Teal and his team produced the first silicon transistor [Che04]. Many electronic devices have become available since then, in which silicon transistors are an essential component. By miniaturization, more and more transistors could be fit onto a small area, thereby enabling the construction of complex processing systems. Contemporary examples of such processing systems include the special purpose processors found in automotive, mobile communications, medical, industrial, and entertainment application domains. Many of these processing systems are tightly coupled to their environment and perform a specific task, and are therefore classified as *embedded systems* [LS11, Mar11, SB00]. Central to this dissertation is the design of the special purpose processors in these embedded systems.

## 1.1 Problem Context

The special purpose processors in embedded systems are highly optimized to perform their application-specific computations in a fast and area- and energy-efficient way. The design of those processors is becoming increasingly challenging due to increasing application complexity, the ever-increasing demand for computational power, and worldwide time-to-market pressure. To satisfy the demand for computational power, *Multi-Processor System-on-Chip (MPSoC)* solutions are deployed in modern embedded systems. Such MPSoCs consist of many different components such as programmable processing components, specialized processing components, memory components, and input/output interfaces. By letting multiple components work in parallel, the demand for computational power is met. Unfortunately, the design of an MPSoC is even more challenging than the design of a single-processor system. The challenge for the designer is to distribute computations over different processors of the MPSoC. While doing so, the designer should guarantee functional correctness of the system and at the same time make tradeoffs between orthogonal design aspects such as circuit area and performance [Mar06]. Thus, the shift to multi-processor systems may address the demand for computational power, but this comes at the expense of a further increase in design complexity.

Traditionally, processors have been designed at the *Register Transfer Level (RTL)*. An RTL specification of a processor consists of registers that are interconnected by signals and combinational logic. RTL design of modern MPSoCs is becoming increasingly error-prone and time-consuming because of the abundance of registers, signals, and combinational logic needed for a modern MPSoC's functionality. To cope with the design complexity of modern MPSoCs, the designer needs to work at a level of abstraction above the RTL. This has led to the emergence of *Electronic System-Level (ESL)* design methodologies [GAGS09, BM10]. In such a design methodology, the designer first specifies a system at a high level of abstraction. Next, the designer constructs an RTL implementation from the initial specification with the aid of system-level design automation tools.

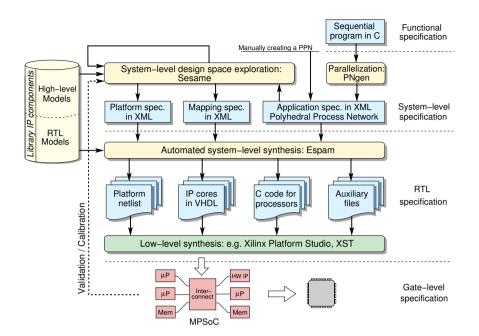

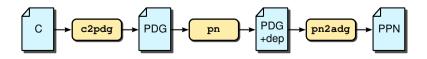

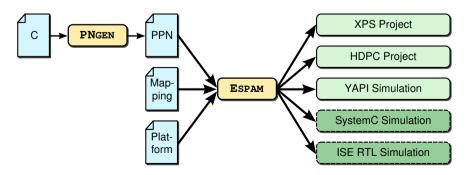

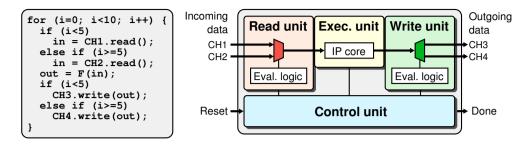

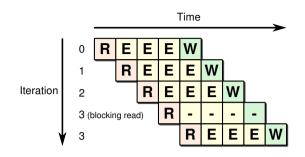

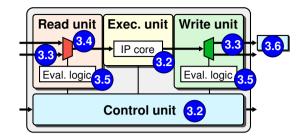

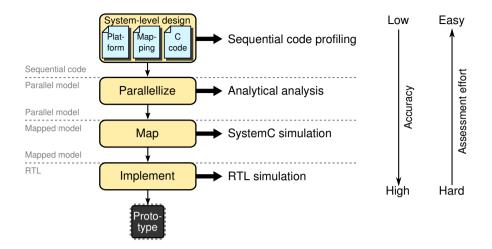

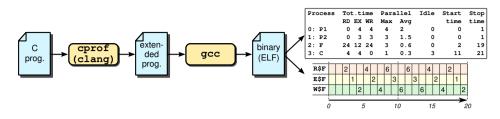

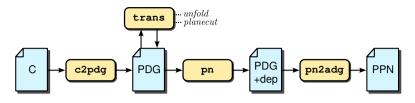

An example system-level design tool set is the open-source Daedalus tool set which has been developed at the Leiden Embedded Research Center (LERC) [NSD08b, Lei08]. We leverage the Daedalus tool set in this thesis. This means that we want to develop the special purpose processors of an embedded system with Daedalus. An overview of the Daedalus system-level tool flow is depicted in Figure 1.1. Daedalus enables a designer to obtain a deployable gate-level specification from a system-level specification in a fully automated way. The functional behavior of the system-level specification is specified as a sequential C program, as shown at the upper right part of Figure 1.1. The elaboration from one specification level to a lower specification level is done in a fully automated way. We discuss the different aspects of Daedalus in the following paragraphs.

Many applications in the embedded systems domain are specified using an imperative model of computation, in for example the C language. Such models are wellsuited and widely adopted to specify the functionality of single-processor systems. Unfortunately, mapping an imperative specification onto a multi-processor system is difficult because of two mismatches. First, the sequential nature of an imperative specification does not match the parallel nature of a multi-processor system. Sec-

Figure 1.1: Daedalus system-level tool flow overview [NSD08b].

ond, an imperative specification assumes shared memory which is likely to become a performance bottleneck on a multi-processor system. A distributed memory model better matches a multi-processor system, but it is not possible in the general case to extract a distributed memory model from an imperative specification.

The functionality of a multi-processor system is more naturally specified using a parallel model of computation such as a network of processes communicating over channels. A model that has gained widespread popularity is the Kahn Process Network model [Kah74]. Specifying the functionality of a system using a parallel model of computation is considered more difficult compared to using an imperative model of computation. This is because the human brain tends to solve problems as a sequence of steps, which matches the sequential nature of an imperative model of computation. Moreover, in a parallel specification deadlocks and race conditions may occur that are very difficult to detect or predict beforehand [Mar06]. Such difficulties do not occur in a sequential specification, despite the subsequent difficulties of implementing the specification as an MPSoC. The mismatch between the programmer-preferred sequential specifications and the parallel specifications desired for multi-processor systems is known as the *specification gap* [Ste04].

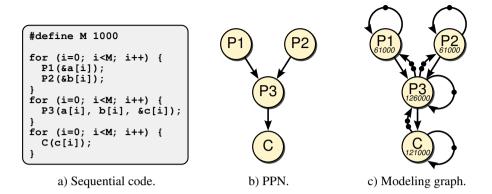

Various approaches exist to bridge the specification gap. One approach is to extend a sequential program with library calls or compiler pragma directives to indicate tasks that can execute concurrently. Examples of this approach include pthreads, OpenCL [Khr08], and OpenMP [Ope97]. Another approach is to automatically extract concurrent tasks from a sequential program using a parallelizing compiler such as LooPo [GL97], Polaris [BEF<sup>+</sup>94], Pluto [BBK<sup>+</sup>08], or PNGEN [VNS07]. The latter is part of Daedalus to bridge the specification gap. PNGEN generates a parallel specification from a sequential program written in a subset of the C language. We discuss PNGEN in more detail in Section 2.3.

A system-level specification lacks many details that are present in the RTL specification because these details are irrelevant at the system level. For example, at the system level the designer reasons about sending data from one processor to another without specifying the registers and logic that implement such communication in the RTL specification. Not exposing the designer to such implementation details allows a designer to better cope with complex systems. However, the omission of implementation details opens up a gap between the system-level specification and the RTL implementation, which is known as the *implementation gap* [NSD08b]. To obtain a functional implementation from a system-level specification, the implementation gap needs to be bridged by adding low-level implementation details to the system-level specification. This is done by a system-level synthesis tool which refines a systemlevel specification into an RTL specification in a systematic and automated way.

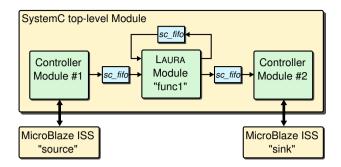

The Daedalus tool set provides the ESPAM tool for automated system-level synthesis. A system-level specification for ESPAM is composed of three individual specifications: an implementation platform specification describing the number and types of processing and interconnect components of the system; a parallel application specification consisting of a network of communicating tasks; and a mapping specification that maps the application tasks onto processing components. The ESPAM tool generates an RTL specification from the three specifications. This RTL specification is then taken through commercial *low-level synthesis* tools that convert the RTL into a gate-level specification. Place-and-route tools take such a gate-level specification and create a layout of the circuit which can be implemented on a *Field-Programmable Gate Array (FPGA)* or provided to an *Application-Specific Integrated Circuit (ASIC)* manufacturing process. This last step yields a complete MPSoC implementation.

### **1.2 Problem Statement**

Existing system-level design tools such as Daedalus present a forward synthesis flow to bridge the specification and implementation gaps. This allows a designer to obtain

a working prototype of a system in only a few hours of time [NSD08b]. However, many different implementations of an application specification are possible that have identical functionality but differ in performance and implementation cost aspects. This presents the designer with another problem: selecting an implementation from a vast *design space* of possible implementations. Only a subset of the *design points* in this design space represent implementations that satisfy a set of given *design constraints* on performance and circuit area. Thus, solely closing the specification and implementation gaps still leaves open the problem of selecting the design point that best matches a set of design constraints.

A Daedalus system-level specification consists of the application, platform, and mapping subspecifications, as described in the previous section and shown in Figure 1.1. Each of these subspecifications may be transformed to yield a functionally equivalent implementation that has different performance and resource cost properties, as described by the Y-chart approach [KDWV02]. For example, a designer can transfrom the platform specification by adding or removing processors, or transform the mapping specification by moving a task from one processor to another, or transform the application specification by splitting a tasks into smaller subtasks and thereby exposing more parallelism. Many combinations of such *transformations* are possible and this number grows rapidly as application and platform sizes increase. As a result, the design space for a modern MPSoC is typically very large.

Despite the existence of fully automated system-level synthesis tools, implementing and evaluating all design points is infeasible for modern MPSoC design because of the large design space. Therefore, the design space should be explored in such a way that only the "promising" design points need to be implemented and evaluated. Finding the promising design points is a non-trivial multi-objective optimization problem. Many *Design Space Exploration (DSE)* techniques have been proposed to efficiently search large design spaces [Gri04]. Daedalus incorporates the SESAME DSE tool to explore the design space using an evolutionary algorithm [PEP06]. SESAME relies on trace-based simulation to estimate the performance of candidate design points. Although SESAME's simulation is intended for fast performance analysis, conducting many simulations may still take a considerable amount of time [PP12]. This leads to unreasonably long design times.

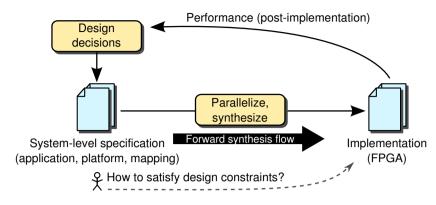

An alternative way of finding a satisfactory design point is the (naive) iterative design flow depicted in Figure 1.2. The design flow starts with an initial system-level specification. A parallel application specification is automatically derived from an imperative program using for example PNGEN, thereby bridging the specification gap. The designer synthesizes this system-level specification into an FPGA prototype to verify if for example performance constraints are satisfied. The designer uses a system-level synthesis tool such as ESPAM in this step, thereby bridging the

Figure 1.2: Iterative system-level design flow.

implementation gap. If a performance constraint is not satisfied, the system-level specification is transformed based on performance and cost metrics obtained from the prototype implementation. These transformations entail modifying the application by rewriting the C code, modifying the platform by adding processors, or modifying the mapping by assigned tasks to different processors. The designer relies on experience and expertise to come up with transformations that most likely have the desirable effect on performance and cost aspects. Building up this knowledge is referred to as the "acquisition of insight" [Spe97]. However, it is not trivial to predict beforehand if and by how much a certain transformation affects performance and cost aspects. At this moment, the best a designer can do is to perform a new time-consuming synthesis step after transforming the system-level specification. This procedure is repeated until an implementation is obtained that satisfies performance constraints. The designer can then proceed with the actual manufacturing of the system.

A naive iterative design flow may appear to be more deterministic than a randomsearch driven DSE flow. Because the designer iteratively transforms a system-level specification in a pragmatic manner, a system that satisfies all performance constraints should eventually be the result. However, this only holds if the designer always makes the optimal decisions. This does not always happen in practice, because the designer may for example overlook solutions or ignore solutions that seem counter-intuitive. Another problem with a naive iterative design flow is that evaluation of a single specification may easily take a few hours of time. This reduces the number of iterations a designer can make in a given time frame, increasing time-tomarket.

The naive iterative design flow bridges both the specification and implementation gaps by employing advanced parallelizing compilation techniques and system-level synthesis tools. However, it does not address the following problem: given a performance constraint, which transformations should the designer apply to obtain an implementation that meets this performance constraint? For example, consider the scenario in which a designer constructs a video processing system under the constraint that the system should meet a throughput of 20 frames per second. After synthesizing the system-level specification, the designer finds that the system works at only 11 frames per second. This puts a burden on the designer to transform the system-level specification such that the performance constraint of 20 frames per second is met. We therefore argue that solely bridging the specification and implementation gaps is not sufficient to solve a design problem.

In this dissertation, we consider the iterative system-level design flow of Figure 1.2 and address a designer's problem that is currently not addressed. That is, we ask how to modify this design flow to obtain a constraint-satisfying implementation of a system in a short amount of time. This modification is needed as synthesizing a design in the current flow takes too long, keeping the designer in the dark whether the design will satisfy the designer's constraints. Performance estimation methods are lacking that could provide an early indication of whether a design will satisfy the designer's constraints at all. After obtaining an implementation not meeting the constraints, there is little guidance to help a designer transform his design in such a way that his performance constraints will be satisfied. In this context, we formulate our three central research problems as follows:

- 1. **Synthesis**: How to automatically obtain efficient RTL implementations from a high-level specification that enable application of established transformations such as splitting, merging, stream multiplexing, and scheduling?

- 2. **Performance estimation**: How to assess the absolute performance of a design point, possibly in different ways by trading off evaluation speed against accuracy?

- 3. **Optimization**: How to obtain an implementation that satisfies a performance constraint while reducing the number of design iterations?

Only after addressing these three problems from a designer's perspective, Daedalus can become a powerful system-level synthesis tool capable of solving design problems.

## **1.3 Related Work**

We address the central problems listed above in this dissertation by leveraging and extending the underlying theory of the Daedalus methodology [NSD08b, Lei08]. The Daedalus methodology addresses the problem of obtaining an efficient FPGA implementation from a high-level application specification in a short amount of time. As such, Daedalus provides an important stepping stone to address the three central problems, ultimately leading to an extended Daedalus design flow that also considers performance constraints.

Daedalus is only one of many methodologies to (semi-)automatically obtain special purpose processor implementations from high-level application and system specifications. In this section, we give a brief overview of related approaches to obtain RTL implementations from high-level application specifications. We discuss related high-level synthesis techniques in Section 1.3.1 and related electronic system-level synthesis techniques in Section 1.3.2. Related work specific to each of the three central problems is discussed separately in Chapters 3, 4, and 5.

### 1.3.1 High-Level Synthesis

Automated synthesis of RTL implementations from specifications above the register transfer level, known as High-Level Synthesis (HLS), has been subject of research since the late 1980s [MK88, MPC88, PK89]. Since then, many academic and commercial HLS tools have been developed. In 1994, electronic design automation company Synopsys released its Behavioral Compiler tool that is widely regarded as the first commercial HLS tool [CM08]. This tool took a behavioral description of a design in VHDL or Verilog as input and generated a cycle-accurate VHDL or Verilog description. During synthesis, the tool allowed the designer to trade off throughput against chip area. Since then, many different HLS tools have been released by different companies, with varying degrees of commercial success. As of 2013, three of the major commercially available HLS tools are Synopsis SynphonyC [Syn10], Xilinx Vivado HLS [Xil13], and Calypso Catapult [Cal11]. A difference with Behavioral Compiler is that modern commercial HLS tools have anchored on C, C++, or SystemC input specifications instead of input specifications using Hardware Description Languages like VHDL or Verilog [Fin10]. Meeus et al. conducted a comparison between twelve different commercial and open-source high-level synthesis tools [MVBG<sup>+</sup>12].

Next to commercial tools, numerous academic high-level synthesis tools have been developed. One of the early academic tools was Hercules [MK88] which has been integrated in the Olympus Synthesis System [MKMT90]. Olympus takes an input specification written in HardwareC and provides synthesis and simulation of designs. HardwareC is a C-like language in which a system is described as a set of concurrent modules. The modules are interconnected using communication primitives. This requires the designer to split the application functionality across different modules and

interconnect them manually using communication primitives. Advanced compilation techniques such as those employed by Daedalus allow tools to automatically derive such interconnects from a sequential specification. The ROCCC tool takes a subset of the C language as input and generates RTL targeted towards FPGAs [GNB08]. ROCCC requires that loop iterators are used in at most one array dimension. This poses a problem when expressing for example a loop skewing transformation. Such a restriction is not necessary in Daedalus as any affine expression of loop iterators is analyzable using the polyhedral model. Other HLS approaches that employ the polyhedral model include for example PARO [HRDT08] and MMALPHA [GQR03]. These approaches use functional languages as input, while commercial tools and Daedalus all use an imperative language. Related early work included modeling affine nested loop programs using uniform recurrence equations to generate systolic array implementations [Qui84]. The FCUDA approach takes C code annotated using NVIDIA's CUDA primitives and generates C code annotated with AutoESL pragmas to obtain an FPGA implementation [PGS<sup>+</sup>09]. This allows a designer to express parallelism in a single specification and target both GPU and FPGA platforms. Besides the main FPGA backend, Daedalus also includes a GPU backend, allowing a designer to also target both GPU and FPGA platforms. Unlike FCUDA, Daedalus does not require CUDA-like annotations of the C code.

High-level synthesis should not be confused with design entry using a high-level language, because the use of a high-level language does not necessarily imply that the design is specified at a high level of abstraction. For example, Handel-C is a subset of the C language with extensions to describe hardware succinctly [Pag96]. Parallel behavior is expressed using the Communicating Sequential Processes (CSP) model of computation [Hoa85]. Similar to RTL design, the designer should perform scheduling and pipelining manually, whereas this is performed automatically in an HLS flow. Cobble is a language similar to Handel-C [TCL05] with support for custom compilation schemes. This allows a designer to define how a particular pattern in the source program should be mapped to hardware. Cobble is compiled into Pebble, which is a simplified hardware description language supporting design parameterization and run-time reconfiguration [LM98]. MyHDL allows a designer to specify hardware in the Python language [Dec03]. MyHDL still requires the designer to specify the behavior of the hardware at the register-transfer level using constructs provided by the MyHDL Python package.

Daedalus may be regarded as an HLS tool to some extent, since it generates RTL from a specification in the C language when a process is mapped onto an application-specific hardware processor. But in contrast to a conventional HLS tool, Daedalus only generates the control path RTL of a hardware processor. Daedalus does not generate data path RTL, as it relies on the designer to provide IP cores that implement

the data path [NSD08a]. Moreover, Daedalus generates complete heterogeneous MP-SoC implementations, which is a task that is beyond the scope of high-level synthesis. Another difference between HLS tools and Daedalus is the model used to represent applications. HLS tools predominantly employ *Control Data Flow Graphs* (*CDFGs*) [MPC88, CGMT09], whereas Daedalus employs a process network based model [VNS07].

### 1.3.2 Electronic System-Level Synthesis

During the late 1990s, electronic system-level synthesis gained interest of system designers as it provided means to cope with the increasing design complexity of systems. A system-level synthesis flow focuses on an entire system possibly containing programmable processors. In contrast, a high-level synthesis flow focuses on a highly optimized application-specific RTL architecture implementing one or more kernels. Many different system-level synthesis tools exist besides Daedalus. SystemCoDesigner takes a set of SystemC modules as input and implements a system by mapping these modules onto hardware and software components [KSS<sup>+</sup>09]. Ptolemy is an environment for simulation and prototyping of heterogeneous systems [BHLM94, EJL<sup>+</sup>03]. A system design in Ptolemy may consist of subsystems that employ different models of computation, such as continuous time or process network based models. PeaCE [HKL<sup>+</sup>08] provides a system-level design environment based on Ptolemy, but restricts itself to an extension of the synchronous data flow model and an extension of the finite state machine model. SystemCoDesigner, Ptolemy, and PeaCE require the designer to specify a system as a set of actors interconnected using communication channels, while Daedalus automatically derives actors (processes) and channels from sequential code. The StreamIt approach [GTA06] requires the designer to specify an application graph using actors and communication channels in a custom language. StreamIt employs the Synchronous Data Flow (SDF) model, which is more restrictive than the PPN model employed by Daedalus. The System-on-Chip Environment (SCE) [DGP+08] uses the SpecC language [ZDG97] to describe system behavior. The SCE design flow consists of similar design steps as Daedalus, such as parallelization, communication synthesis, and RTL generation. However, the parallelization step is automated in Daedalus, whereas SCE requires the designer to explicitly specify the system as a set of concurrent tasks interconnected using communication channels. The MPSoC Application Programming Studio (MAPS) [LC10] is a framework that aids the MPSoC designer with C application parallelization. The parallelization in MAPS is relies on profiling information, whereas parallelization in Daedalus is static. Like Daedalus, MAPS can also incorporate already parallelized applications specified as a (Kahn) process network. Unlike

Daedalus, MAPS does not provide an automated way to obtain a parallelized variant of a sequential application. The Multi-Application and Multi-Processor Synthesis (MAMPS) flow maps synchronous dataflow graphs onto homogeneous MPSoCs. In contrast, Daedalus uses the more expressive PPN model and targets heterogeneous MPSoCs. MAMPS on the other hand supports multiple applications at once, whereas the Daedalus version used in this thesis supports only one application at once, although the Daedalus<sup>RT</sup> extension does support multiple applications [BZNS12].

Bluespec SystemVerilog (BSV) is a high-level hardware description language intended to describe complete systems [NC10]. In a comparison conducted by Nikolov et al., a C specification of an H.264 video decoder was implemented using both the automated Daedalus flow and as a semi-custom design in BSV [NRD<sup>+</sup>09]. The Daedalus design employed programmable components as processing elements, on which the C specification was mapped. The Bluespec design employed dedicated hardware processing elements, requiring manual conversion of the C specification to BSV. The authors found that the design time for the Daedalus approach was roughly 6 times shorter than the design time for the Bluespec design. This difference was mainly caused by the manual conversion and verification in the BSV design. However, the shorter design time in Daedalus came at the expense of higher resource cost caused by the use of programmable processors. Replacing programmable processors with dedicated RTL cores may reduce the resource cost footprint in the Daedalus flow. Such cores can be obtained automatically from C using HLS tools. We discuss the integration of HLS in Daedalus in Chapter 3.

Several ESL tools focus on graphical entry of a system-level design. For example, a system is specified in Koski using Unified Modeling Language (UML) [KKO<sup>+</sup>06]. Xilinx System Generator provides a block-based design environment [Xil02]. A System Generator design can be compiled into a netlist, which can then be synthesized onto an FPGA. The latest Vivado design suite from Xilinx integrates System Generator, AutoESL, and RTL synthesis into a single ESL design environment.

Many of the discussed high-level synthesis and system-level design tools do not address the specification gap, as they require the designer to provide a parallel specification. On the other hand, Daedalus employs the PNGEN tool flow to bridge the specification gap as it can automatically find a parallel specification. As the designer does not have to provide a parallel specification, the design process is accelerated. A key challenge of automated parallelization is detecting the statements that are independent of each other, such that they can execute in parallel. PNGEN employs exact data dependence analysis to precisely find the dependence relations between statements [Fea91]. Obtaining exact data dependence information is complicated and is not always possible for arbitrary code. Most HLS and ESL tools that start from a sequential specification therefore rely on approximate data dependence analysis techniques such as Banerjee's test [Ban88]. But as a result of the approximate nature, tools may need to conservatively assume a data dependence exists between statements, possibly preventing any parallel execution. Such false data dependences can be circumvented using tool-specific compiler pragmas that need to be inserted by the designer. Daedalus requires that the application is specified as a SANLP (cf. Section 2.3) for which exact data dependence analysis is always feasible. This eliminates the need for conservative data dependence assumptions, freeing the designer from having to manually analyze data dependences.

### **1.4** Contributions and Outline

In Section 1.2, we identified three central problems in an iterative system-level design flow. We solve these three problems in this dissertation in the context of the Daedalus methodology [NSD08b], which we discuss in more detail in **Chapter 2**. The Daedalus methodology is the result of many dissertations in the LERC group [Rij02, Ste04, Tur07, ZI08, Nik09, Mei10, Nad12, Bal13]. We want to build further upon the contributions made in these dissertations. The research conducted in this thesis has led to the following four contributions:

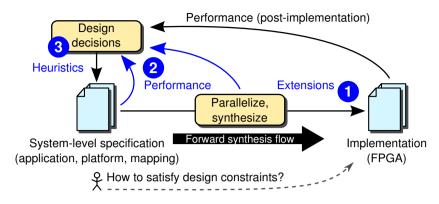

**Contribution I** [HK09, NHS<sup>+</sup>11, HK12]: As a solution to the synthesis problem, we add extensions to the Daedalus methodology. These extensions enable us to obtain FPGA implementations from C programs which were already accepted by Daedalus, but for which an FPGA implementation was not yet feasible. With these extensions, we are now able to obtain complete FPGA implementations for industrially relevant applications, like the sphere decoder application discussed in Chapter 6. We have shown that we can characterize and integrate functional kernels (IP cores) from a broad set of conventional HLS tools like the industrial tools Vivado HLS and Synphony C, and the academic tool DWARV. Our extensions to the Daedalus methodology provide an enabling step to realize the complete conventional "forward" system-level synthesis flow for FPGAs in the flow shown in Figure 1.3. The position of these extensions is indicated by the **0** in Figure 1.3 and are discussed in **Chapter 3**.

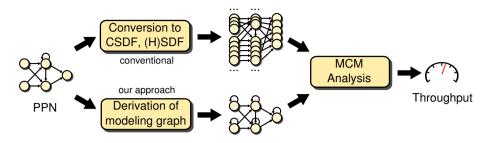

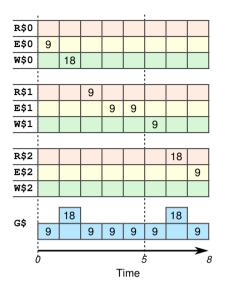

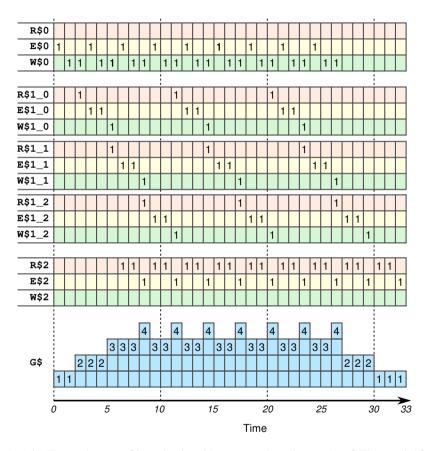

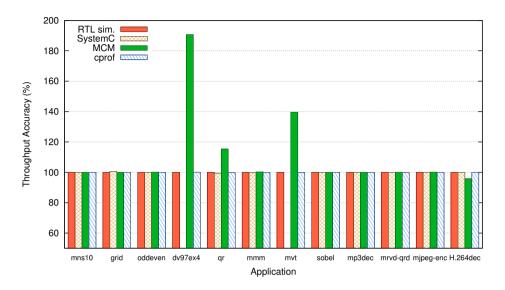

**Contribution II** [HHK10]: As a solution to the performance estimation problem, we investigate four different performance estimation techniques, that differ in accuracy and assessment effort. We want to emphasize on two techniques in particular. We show a novel analytical approach to estimate the performance of cyclic PPNs. The analytical approach is based on the well-known *Maximum Cycle Mean* (MCM) theory from the HSDF model of computation, but avoids exponential complexity explosion in the PPN-to-HSDF conversion. Although providing a theoretical basis, the practical use is limited due to unknown accuracy of the result. In that respect, an-

Figure 1.3: Contributions positioned in the iterative design flow.

other contribution of this thesis is *cprof*, which is a novel profiling based approach that completely bypasses the forward synthesis flow. The approach is robust as it relies only on an ordinary  $C^{++}$  compiler to obtain accurate performance estimates of PPNs. Moreover, the approach allows for early estimation of the effects of transformations. The approach provides the designer with an upper bound on the degree of parallelism in an application specification. This allows a designer to assess at a very early stage in the design flow whether he can meet his constraints. The position of the alternative performance estimation techniques in the overall design flow is indicated by the ② in Figure 1.3 and is discussed in **Chapter 4**.

**Contribution III** [HK12]: As a solution to the optimization problem, we provide heuristics to optimize a design by leveraging the insight gained from the performance estimation techniques discussed in Chapter 4. The heuristics provide a concrete set of criteria that guide the designer in selecting standard transformations such as splitting, merging, stream multiplexing, and scheduling. This position of the heuristics is indicated by the **③** in Figure 1.3 and is discussed in **Chapter 5**.

**Contribution IV** [HNVK11, NNH<sup>+</sup>10, NNH<sup>+</sup>11]: We have shown that we can apply the extended forward system-level synthesis flow depicted in Figure 1.3 on an industrially relevant application. This case study also shows that PPNs are a feasible alternative to conventional CDFG-based C-to-RTL flows. Using the heuristics from Chapter 5, in particular merging, we were able to transform the design to obtain a new pareto design point that was not achievable with a state-of-the-art industrial HLS tool. The use of the profiling-based cprof performance estimation technique presented in Chapter 4 was essential to gain insight in the application performance and the optimization opportunities. The case study is discussed in **Chapter 6**.

We summarize our work and conclude in Chapter 7.

## BACKGROUND

In this chapter, we introduce concepts and notations that are used throughout this thesis. In Section 2.1, we introduce the polyhedral model which we employ for analysis of programs. In Section 2.2, we review various models of computation that are widely employed to represent applications. We focus on the polyhedral process network model of computation employed by Daedalus and review in Section 2.3 how such networks can be derived from a particular class of sequential programs. In Section 2.4, we review how processes of polyhedral process networks can be implemented in hardware.

## 2.1 Polyhedral Model

The streaming applications that we consider in this thesis are data-driven: a sequence of computations is repeatedly applied on an incoming data stream, such as a stream of images produced by a video camera. These streaming applications spend most of their execution time in loops that perform computations on data stored in arrays. For example, edge detection algorithms consist of loop nests that iterate over all pixels of the input image that is stored in a 2-dimensional array. These loop nests are the primary candidates for optimization, since most of the time is spent there. To select and apply optimizations, one needs means to reason about iterations of loops and relations between statements contained in loop nests. This is possible with the polyhedral model [Pug91, Fea96] which is employed by modern compilers like GCC [PCB<sup>+</sup>06] and LLVM/Polly [GZA<sup>+</sup>11]. The polyhedral model allows a compact representation of loop nests while providing sufficient means to express advanced optimizations such as loop skewing [SKD02]. We use polyhedra to compactly represent loop nests

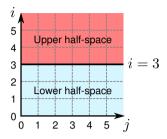

Figure 2.1: A 1-dimensional hyperplane (i.e., a line)  $H_1 = \{(j,i) \in \mathbb{Q}^2 \mid i = 3\}$  dividing a 2-dimensional space.

in the polyhedral model. A polyhedron can be defined using hyperplanes.

### Definition 2.1 (Hyperplane).

A hyperplane H is a subspace of dimension d - 1 inside a d-dimensional space, that is,

$$H = \{ \mathbf{x} \in \mathbb{Q}^d \mid \mathbf{a}^T \mathbf{x} = c \},\$$

where  $\mathbf{a}$  is a non-zero vector of size d and c is a constant [Rij02].

A hyperplane is a generalization of a conventional 2-dimensional plane to  $n \in \mathbb{N}$  dimensions. A 1-dimensional hyperplane dividing a 2-dimensional space is shown in Figure 2.1. A hyperplane divides a space into an upper and a lower *half-space*. We distinguish *open half-spaces* which do not include the dividing hyperplane itself, and *closed half-spaces* which include the dividing hyperplane. We use hyperplanes to define subspaces of  $\mathbb{Q}^d$ , known as rational polyhedra:

### Definition 2.2 (Rational Polyhedron).

A rational polyhedron  $\mathcal{P}$  is a subspace of  $\mathbb{Q}^d$  that is bounded by a finite set of m hyperplanes, that is,

$$\mathcal{P} = \{ \mathbf{x} \in \mathbb{Q}^d \mid A\mathbf{x} \ge \mathbf{c} \},\$$

where A is an integral  $m \times d$  matrix and c is an integral vector of size m [Ver10].

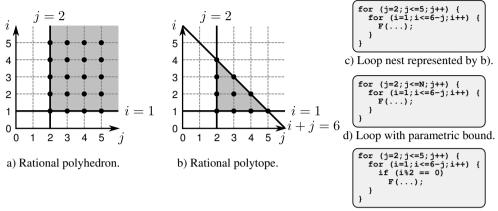

The shaded rectangular area in Figure 2.2a represents a 2-dimensional rational polyhedron that is bounded by the closed upper half-spaces of two 1-dimensional hyperplanes i = 1 and j = 2. This rational polyhedron extends into infinity in both dimensions. By adding the closed lower half-space of the hyperplane i + j = 6 to the bounds, we obtain a rational polyhedron that is fully enclosed by its bounding hyperplanes, as shown in Figure 2.2b. Such an enclosed rational polyhedron containing a finite number of integral points is called a *rational polytope*.

e) Statement with modulo guard.

Figure 2.2: a) A 2-dimensional rational polyhedron; b) a 2-dimensional rational polytope; c) a loop nest of depth two that can be represented by the 2-dimensional rational polytope given in b); d) a loop nest where the outer loop has a parametric upper bound; and e) a statement with a modulo guard.

#### Definition 2.3 (Parametric Rational Polyhedron).

A *parametric rational polyhedron*  $\mathcal{P}(\mathbf{s})$  is a family of rational polyhedra in  $\mathbb{Q}^d$  that is parametrized by parameters  $\mathbf{s} \in \mathbb{Q}^n$ :

$$\mathbf{s} \mapsto \mathcal{P}(\mathbf{s}) = \{ \mathbf{x} \in \mathbb{Q}^d \mid A\mathbf{x} + B\mathbf{s} \ge \mathbf{c} \},\$$

where A is an integral  $m \times d$  matrix, B is an integral  $m \times n$  matrix, and c is an integral vector of size m [Ver10].

A parametric rational polyhedron can represent a loop nest that iterates over a finite, possibly parameterized set of iterations. By assuming that the iterators of such a loop nest are integers, we can represent a loop nest as a set of integral points in a (parametric) rational polyhedron. For example, the loop nest shown in Figure 2.2c can be represented by the rational polytope shown in Figure 2.2b. Each iteration of the loop nest has a corresponding point in the rational polytope. The loop nest shown in Figure 2.2d can be represented by a parametric rational polytope.

When for example a statement is guarded with an expression containing a modulo operator, we are interested in only a subset of the points of a parametric rational polyhedron. In the example shown in Figure 2.2d, function F is called only for even values of iterator i. We define the polyhedral set to represent a subset of points in a parametric rational polyhedron.

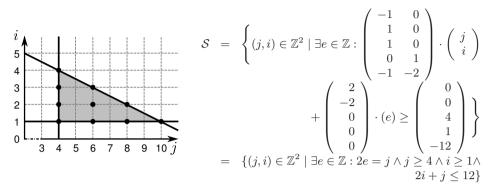

Figure 2.3: Example polyhedral set.

#### Definition 2.4 (Polyhedral Set).

A polyhedral set S is a finite union of basic integer sets,  $S = \bigcup_i S_i$ , of type  $\mathbb{Q}^n \to 2^{\mathbb{Q}^d}$ , where each basic integer set  $S_i$  is defined as

$$\mathcal{S}_i = \mathbf{s} \mapsto \mathcal{S}_i(\mathbf{s}) = \{ \mathbf{x} \in \mathbb{Z}^d \mid \exists \mathbf{z} \in \mathbb{Z}^e : A\mathbf{x} + B\mathbf{s} + D\mathbf{z} \ge \mathbf{c} \}.$$

where A is an integral  $m \times d$  matrix, B is an integral  $m \times n$  matrix, D is an integral  $m \times e$  matrix, and c is an integral vector of size m. The *parameter domain* of S,  $\{s \in \mathbb{Z}^n \mid S(s) \neq \emptyset\}$ , is a polyhedral set containing all parameter values s for which S is non-empty. A polyhedral set with an empty parameter domain (i.e., n = 0) is called a *non-parametric* polyhedral set, and denoted with "s  $\mapsto$ " omitted. The parameter domain of a polyhedral set is always non-parametric [Ver10].

The polyhedral set depicted in Figure 2.3 contains only a subset of the integral points of its bounding rational polytope. In particular, it only contains the integral points for even values of j, which can be expressed as " $j \mod 2 = 0$ ". Such constraints are enforced using the existentially quantified variables z in Definition 2.4. For example, the constraint " $j \mod 2 = 0$ " is represented by a condition 2e = j and the requirement that e is integral.

To allow reasoning about the execution order of different iterations of a program, we define the lexicographic order on the points of a polyhedral set:

### Definition 2.5 (Lexicographic Order).

The *lexicographic order* is a total order on the elements of a polyhedral set. An element a is lexicographically smaller than an element b, denoted as  $a \prec b$ , if

$a_i < b_i$  for the first dimension *i* in which both elements differ, or, equivalently,

$$\mathbf{a} \prec \mathbf{b} \equiv \bigvee_{i=1}^{n} \left( a_i < b_i \land \bigwedge_{j=1}^{i-1} a_j = b_j \right).$$

For example, an element a = (2, 3, 5) is lexicographically smaller than an element b = (2, 4, 0), because the first difference between both elements is in the second dimension, and the value 3 in the second dimension of a is less than the value 4 in the second dimension of b.

Loop optimizations such as skewing transform iteration domains that we represent using polyhedral sets. A transformation of a polyhedral set can be expressed as a relation between the original polyhedral set and the transformed polyhedral set. We define the polyhedral map to express such relations:

#### Definition 2.6 (Polyhedral Map).

A polyhedral map  $\mathcal{M}$  is a finite union of basic polyhedral maps,  $\mathcal{M} = \bigcup_i \mathcal{M}_i$ , of type  $\mathbb{Q}^n \to 2^{\mathbb{Q}^{d_1+d_2}}$ , where each basic polyhedral map is defined as

$$\mathcal{M}_i = \mathbf{s} \mapsto \mathcal{M}_i(\mathbf{S})$$

= {( $\mathbf{x_1}, \mathbf{x_2}$ )  $\in \mathbb{Z}^{d_1} \times \mathbb{Z}^{d_2} \mid \exists \mathbf{z} \in \mathbb{Z}^e : A_1 \mathbf{x_1} + A_2 \mathbf{x_2} + B\mathbf{s} + D\mathbf{z} \ge \mathbf{c}$ },

where  $A_1$  is an integral  $m \times d_1$  matrix,  $A_2$  is an integral  $m \times d_2$  matrix, B is an integral  $m \times n$  matrix, D is an integral  $m \times e$  matrix, and **c** is an integral vector of size m [Ver10].

The polyhedral set

$\mathbf{s} \mapsto \{\mathbf{x_1} \in \mathbb{Z}^{d_1} \mid \exists \mathbf{x_2} \in \mathbb{Z}^{d_2} : (\mathbf{x_1}, \mathbf{x_2}) \in M(\mathbf{s})\}$

is the *domain* of a polyhedral map M. The polyhedral set

$$\mathbf{s} \mapsto {\mathbf{x_2} \in \mathbb{Z}^{d_2} \mid \exists \mathbf{x_1} \in \mathbb{Z}^{d_1} : (\mathbf{x_1}, \mathbf{x_2}) \in M(\mathbf{s})}$$

is the range of a polyhedral map M. In this thesis, we denote polyhedral maps as

$$\mathcal{M} = \mathbf{s} \mapsto \{\mathbf{x_1} \to \mathbf{x_2} \mid \dots \}.$$

An example polyhedral map consisting of only one basic polyhedral map is

$$\mathcal{M}_1 = \{ (j_1, i_1) \to (j_2, i_2) \mid j_2 = 2j_1 \land i_2 = i_1 \}.$$

(2.1)

We use polyhedral maps to manipulate points or polyhedral sets by application of the

polyhedral map. For example, applying  $\mathcal{M}_1$  to a point (2, 1) yields (4, 1), denoted as

$$\mathcal{M}_1(2,1) = (4,1).$$

If we apply this polyhedral map to the polyhedral set of Figure 2.2b, that is, if we compute  $\mathcal{M}_1(\mathcal{S}_1)$ , we obtain the polyhedral set depicted in Figure 2.3. The points in this new polyhedral set result from application of  $\mathcal{M}_1$  to each point in the original polyhedral set  $\mathcal{S}_1$ .

We sometimes need to know the size of a polyhedral set or map, for example to judge whether a certain transformation is beneficial to a given program. The number of elements in a polyhedral set or polyhedral map is given by the cardinality:

### Definition 2.7 (Cardinality).

The *cardinality* of a polyhedral set S, denoted as |S|, represents the number of elements in S.

The cardinality of a polyhedral map  $\mathcal{M}$ , denoted as  $|\mathcal{M}|$ , represents the number of elements in the range of  $\mathcal{M}$  associated to any element in the domain of  $\mathcal{M}$ .

We use the barvinok library to analytically determine the cardinality of polyhedral sets and maps [VSB<sup>+</sup>07, Ver03a]. The cardinality is expressed as a piecewise quasipolynomial. A piecewise quasipolynomial consists of one or more quasipolynomials:

#### Definition 2.8 (Quasipolynomial).

A quasipolynomial  $q(\mathbf{x})$  is a polynomial expression in greatest integer parts of affine expressions of variables in  $\mathbf{x}$ . The coefficient of each term may include a constant integer division [Ver10].

#### Definition 2.9 (Piecewise Quasipolynomial).

A piecewise quasipolynomial  $q(\mathbf{x})$  consists of one or more quasipolynomials. Each quasipolynomial  $q_i(\mathbf{x})$  is defined only for a disjoint piece  $\mathcal{D}_i$  of a domain  $\mathcal{D}$ . For a given point  $\mathbf{x} \in \mathcal{D}$ , the piecewise quasipolynomial evaluates to

$$q(\mathbf{x}) = \begin{cases} q_i(\mathbf{x}) & \text{if } \mathbf{x} \in \mathcal{D}_i, \\ 0 & \text{otherwise} \quad \text{[Ver10].} \end{cases}$$

For example, the cardinality of the polyhedral set  $S_2$  of Figure 2.3 is expressed using the piecewise quasipolynomial

$$|\mathcal{S}_2| = \begin{cases} 10 & \text{if } 1 \ge 0 \end{cases}.$$

The cardinality of  $S_2$  is constant because all bounding hyperplanes are constant. Therefore, the cardinality is not dependent on any parameters or variables and consists of only one piece that is selected using the tautology  $1 \ge 0$ . The quasipolynomial has a constant value of 10, as  $S_2$  consists of 10 points.

The cardinality of the polyhedral map  $M_1$  of Equation (2.1) is expressed using the piecewise quasipolynomial

$$\mathcal{M}_1|(j_1, i_1) = \begin{cases} 1 & \text{if } (j_1, i_1) \in \mathbb{Z}^2, \\ 0 & \text{otherwise.} \end{cases}$$

This means that applying  $\mathcal{M}_1$  to any point  $(j_1, i_1)$  that is in  $\mathbb{Z}^2$  always yields exactly one new point  $(j_2, i_2)$ .

### 2.2 Models of Computation

Designers specify the behavior of a system in a structured way using a Model of *Computation (MoC)*. To facilitate programming of multi-processor systems, a parallel MoC is needed such that the tasks for each processor and the communication and synchronization mechanisms can be specified. Different MoCs have been proposed and evaluated for their use in design automation in literature [LSV98, JS05]. For example, HDL simulators often employ a timed discrete-event MoC in which all events are ordered globally in time. A global ordering is often not desired for a multi-processor system because different parts of the system may execute in parallel. Our interest is in untimed dataflow process network based MoCs such as Kahn Process Networks (KPNs) defined by Kahn [Kah74]. The dataflow-based MoCs that we consider in this thesis have several properties that make them attractive for specification of multi-processor systems  $[SZT^+04]$ . One desirable property is deterministic behavior, such that a given input sequence always results in the same output sequence regardless of variations in computation or communication times. Another desirable property is that each task behaves autonomously, such that each processor of a multiprocessor system can be considered in isolation. This allows designers to better cope with complex multi-processor systems.

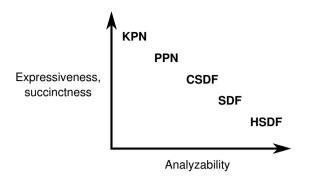

Many different specializations of dataflow process network based MoCs have been proposed in literature for the design of streaming applications. A major reason for the abundance of different specializations is to allow different tradeoffs of expressiveness against analyzability. With *expressiveness* of a model we refer to the ability to express an application in that model in a succinct way. Although more general models often can be converted to more specialized equivalent models, such a conversion often increases the size of the application model making it no longer succinct. With *analyzability* of a model we refer to the existence and complexity of compiletime analysis algorithms to compute for example static schedules, buffer sizes, or

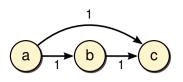

Figure 2.4: Different models and their expressiveness and analyzability.

throughput. In Figure 2.4, we depict five different models and compare their expressiveness and analyzability. For example, many applications can be expressed in the KPN MoC, but due to the genericity of the model, the compile-time analyzability is limited. In contrast, the HSDF model has a lower expressiveness but this allows for full analyzability. We now review four dataflow-based models that we use in the remainder of this thesis for specification and analysis of MPSoCs: the HSDF, SDF, CSDF, and PPN models of computation.

## 2.2.1 Homogeneous Synchronous Dataflow

The most restricted model of computation that we consider in this thesis is the homogeneous synchronous dataflow model, which is also known as the single-rate dataflow model [GGS<sup>+</sup>06]. The more generic models that we discuss later extend the homogeneous synchronous dataflow model. We use the following definition, in line with the notation used by e.g. Moreira et al. [MBGS10]

Definition 2.10 (Homogeneous Synchronous Dataflow Graph).

A Homogeneous Synchronous Data Flow (HSDF) graph is a directed graph defined by a tuple (V, E, t, d), where

- V is a set of vertices representing computation nodes,

- *E* is a set of *edges* representing communication channels that carry *tokens*,

- $t(i), i \in V$  represents the time needed for a single execution of node *i*, and

- d(e), e ∈ E represents the number of *initial tokens* on edge e, also referred to as the *delay* of edge e.

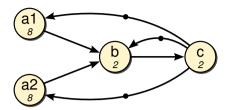

An HSDF graph consisting of four nodes and six edges is shown in Figure 2.5. Shown in the upper half of each node is a label that we assign for convenient referencing. Shown in the lower half of each node is the node's execution time t(i). For

Figure 2.5: An HSDF graph.

example, node b has an execution time t(b) = 2 time units. Initial tokens d(e) for each edge are shown as dots on the edges. For example, the edge connecting node c to a2 contains one initial token, that is,  $d(c \rightarrow a2) = 1$ . For clarity reasons, we may visualize multiple initial tokens by a single dot and a number above or below the dot.

Edges transfer units of data referred to as *tokens*. A node is said to be *enabled* if each of its incoming edges contains at least one token. An enabled node is said to *fire* when it consumes a token from each incoming edge, performs a computation on these tokens, and then produces a token on each of its outgoing edges. If none of the nodes is enabled, then the graph is in a *deadlock* state. If all nodes of a graph can fire infinitely often, then the graph is *live*. An HSDF graph is said to be *consistent* if every token written to an edge is eventually consumed, such that the graph can be executed under bounded memory conditions. An *iteration* of an HSDF graph is defined as each node executing exactly once.

Different firings of a node may start at the same time, such that overlapped execution between firings of the same node occurs. For example, if edge  $c \rightarrow al$  in Figure 2.5 would contain two initial tokens, then two firings of *al* can start simultaneously. Such overlapped execution of firings of the same node is referred to as *auto-concurrency*. By adding an edge from a node to itself, referred to as *a selfloop*, we can regulate auto-concurrency of a node. The number of initial tokens on that selfloop limits the number of parallel firings. By putting one initial token on the selfloop, autoconcurrency is fully prevented. In such a case, the node consumes the initial token from the selfloop at the first firing, and only produces a new token on the edge once it finishes its firing. The node is not enabled for any subsequent firings until the first firing has finished, meaning no overlap between firings occurs.

#### 2.2.2 Synchronous Dataflow

HSDF graphs are a special case of the more general synchronous dataflow graphs defined by Lee and Messerschmitt [LM87].

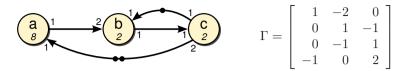

Figure 2.6: An SDF graph and its topology matrix  $\Gamma$ .

#### Definition 2.11 (Synchronous Dataflow Graph).

A Synchronous Data Flow (SDF) graph is a directed graph defined by a tuple (V, E, t, d, p, c), where

- V, E, t, and d follow those in Definition 2.10,

- *p*(*e*), *e* ∈ *E* represents the number of tokens placed on edge *e* when the corresponding source node fires, referred to as the *production rate*, and

- c(e), e ∈ E represents the number of tokens consumed from edge e when the corresponding destination node fires, referred to as the *consumption rate*.

An SDF graph consisting of three nodes and four edges is shown in Figure 2.6. The numbers depicted at the location where edges connect to nodes represent the production and consumption rates. For example, when node c fires it consumes  $c(b \rightarrow c) = 1$  token from edge  $b \rightarrow c$ , and it produces  $p(c \rightarrow b) = 1$  token on edge  $c \rightarrow b$  and  $p(c \rightarrow a) = 2$  tokens on edge  $c \rightarrow a$ .

The structure and production and consumption rates of an SDF graph are compactly represented by a *topology matrix*  $\Gamma$ . The columns of  $\Gamma$  represent the nodes and the rows of  $\Gamma$  represent the edges. A positive entry  $\Gamma(i, j)$  means that node j produces  $\Gamma(i, j)$  tokens on edge i. A negative entry  $\Gamma(i, j)$  means that node j consumes  $-\Gamma(i, j)$  tokens from edge i. A zero entry  $\Gamma(i, j)$  means that node j does not read or write to edge i. A selfloop can be represented in  $\Gamma$  by the net difference between production and consumption [LM87, p. 27].

An SDF graph can be converted into an equivalent HSDF graph [SB00, Chapter 3]. However, such a conversion may cause an exponential increase in the number of nodes in the worst case. The HSDF graph of Figure 2.5 is the result of converting the SDF graph of Figure 2.6. An *iteration* of an SDF graph is defined as each node of the equivalent HSDF graph executing exactly once. If an SDF graph is consistent, then a *repetition vector*  $\mathbf{q}$  exists which contains for every node the number of times the node has to fire to return the SDF graph to its initial state. The repetition vector is the smallest non-trivial positive integer vector that is a valid solution to the *balance equation*  $\Gamma \cdot \mathbf{q} = \mathbf{0}$ .

For the graph of Figure 2.6, the smallest non-trivial solution to the balance equation is the repetition vector  $\mathbf{q} = [2, 1, 1]^T$ . This means that if node *a* fires twice, node *b*

fires once, and node c fires once, then the number of initial tokens on each edge is the same as before the execution of these four firings.

An SDF node always consumes tokens from all input edges and produces tokens on all output edges during a firing. Consequently, the SDF model cannot describe a node that for example reads from different input ports during different firings. This means that applications in which such behavior occurs cannot be modeled as an SDF graph.

### 2.2.3 Cyclo-Static Dataflow

An extension to the SDF model that allows such behavior is the cyclo-static dataflow model [BELP96]. This model allows a compact representation of applications with a cyclically changing, but predefined behavior.

#### Definition 2.12 (Cyclo-Static Dataflow Graph).

A Cyclo-Static Data Flow (CSDF) graph is a directed graph defined by a tuple  $(V, E, \mathbf{f}, \mathbf{t}, d, \mathbf{p}, \mathbf{c})$ , where

- V, E, and d follow those in Definition 2.10,

- f<sub>j</sub>, j ∈ V represents the function repertoire for node j, which is a sequence of functions [f<sub>j</sub>(0), f<sub>j</sub>(1), · · · , f<sub>j</sub>(S<sub>j</sub> − 1)] of phase length S<sub>j</sub>,

- $\mathbf{t}_j(i), j \in V$  represents the time needed for an execution of function i in  $\mathbf{f}_j$ ,

- p<sub>e</sub>(i), e ∈ E is a sequence of integers representing the number of tokens produced on edge e after e's source node fires its i-th function, and

- $\mathbf{c}_e(i), e \in E$  is a sequence of integers representing the number of tokens consumed from edge e before e's destination node fires its *i*-th function.

Each node in a CSDF graph executes the functions in its function repertoire in a cyclic fashion. At the start of the *n*-th firing of node j,  $\mathbf{c}_e(n \mod S_j)$  tokens are consumed from incoming edge e. Then, function  $f_j(n \mod S_j)$  is executed which takes  $\mathbf{t}_j(n \mod S_j)$  time units. After the function finishes execution,  $\mathbf{p}_e(n \mod S_j)$  tokens are produced on outgoing edge e.

Similar to the topology matrix of an SDF graph, we can define a *topology matrix*  $\Gamma$  for a CSDF graph. A positive entry  $\Gamma(i, j)$  means that node j produces in total  $\Gamma(i, j)$  tokens on edge i for a complete execution sequence, that is,  $\Gamma(i, j) = \sum_{k=0}^{S_j-1} \mathbf{p}_i(k)$ . A negative entry  $\Gamma(i, j)$  means that node j consumes in total  $\Gamma(i, j)$  tokens from edge i for a complete execution sequence, that is,  $\Gamma(i, j) = -\sum_{k=0}^{S_j-1} \mathbf{c}_i(k)$ . All other entries are zero.

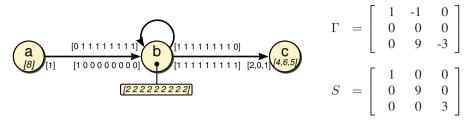

Figure 2.7: A CSDF graph, its topology matrix  $\Gamma$ , and its phase matrix S.

To obtain the repetition vector of a CSDF graph, one first solves the *balance equation*  $\Gamma \cdot \mathbf{r} = \mathbf{0}$ . The repetition vector then equals

$$\mathbf{q} = S \cdot \mathbf{r}, \qquad \text{where } S(i, j) = \begin{cases} S_j & \text{if } i = j, \\ 0 & \text{otherwise.} \end{cases}$$

(2.2)

Matrix S in Equation (2.2), whose diagonal contains the phase lengths of all nodes, is referred to as the *phase matrix*.

A CSDF graph consisting of three nodes and three edges is shown in Figure 2.7. The function repertoire of node c contains three functions with latencies 4, 6, and 5, as shown in the bottom part of the node. Thus, the phase length of node  $c S_c = 3$ . Node c has one incoming edge  $b \rightarrow c$ . In the 0 (mod 3)-th execution of node c, two tokens are consumed from this edge; in the 1 (mod 3)-th execution of node c, no tokens are consumed; and in the 2 (mod 3)-th execution of node c, one token is consumed from this edge.

The topology matrix of the CSDF graph is shown in the upper right part of Figure 2.7. Since the CSDF graph contains a selfloop, the second row of  $\Gamma$  consists entirely of zeros. The phase matrix of the CSDF graph is shown in the lower right part of Figure 2.7. For example, the lower right element of this matrix equals node c's phase length  $S_c = 3$ . The smallest non-trivial solution to the balance equation is  $\mathbf{r} = [1, 1, 3]^T$ . Hence, the repetition vector of the CSDF graph  $\mathbf{q} = [1, 9, 9]^T$ .

The phase lengths and production and consumption patterns  $\mathbf{p}$  and  $\mathbf{c}$  may be large for applications that have mainly regular, but occasionally irregular behavior. This is for example found in image edge detection algorithms, whose behavior is regular for most pixels, but irregular for pixels at the image borders. Large phase lengths make a CSDF representation impractical for analysis and synthesis tools. We therefore present another model in which complex patterns can be captured in a compact way using the polyhedral model.

### 2.2.4 Polyhedral Process Networks

The Daedalus system-level design tool set that was introduced in Section 1.1 (cf. Figure 1.1) employs polyhedral process networks as its application model. The polyhedral process network model was first coined by Meijer et al. [MNS10] and was later formally defined by Verdoolaege [Ver10]. The definition of Verdoolaege differs from the classical definitions employed by the Compaan and Daedalus tools, as presented by for example Turjan [Tur07], Nikolov et al. [NSD08b], and Rijp-kema [Rij02]. Throughout this thesis, we use the definition of the latter references. A conversion from the definition of Verdoolaege to the definition used by Daedalus is possible and is extensively used in the Daedalus tool flow [Ver03b].

#### Definition 2.13 (Polyhedral Process Network).

A Polyhedral Process Network (PPN) is a directed graph  $(\mathcal{P}, \mathcal{E})$  where  $\mathcal{P}$  is a set of vertices representing processes and  $\mathcal{E}$  is a set of edges representing communication channels. Each process  $p_i \in \mathcal{P}$  is characterized by:

- a function  $F_i$ ,

- a process dimensionality  $d_i$ ,

- a polyhedral set  $D_i \subseteq \mathbb{Z}^{d_i}$  defining the process' domain.

- a set of *input ports*  $IP_i$ , where the k-th input port  $IP_i^k$  is bound to an input argument of  $F_i$  and has an associated *Input Port Domain* (*IPD*)  $IPD_i^k \subseteq D_i$ , and

- a set of *output ports*  $OP_i$ , where the k-th output port  $OP_i^k$  is bound to an output argument of  $F_i$  and has an associated *Output Port Domain* (*OPD*)  $OPD_i^k \subseteq D_i$ .

Each channel  $c_i \in \mathcal{E}$  is characterized by:

- a source process  $\sigma_i \in \mathcal{P}$ ,

- a destination process  $\delta_i \in \mathcal{P}$ ,

- a source process' output port  $OP_{\delta_i}^j$ ,

- a destination process' input port  $IP_{\sigma_i}^k$ ,

- a polyhedral map  $M_i \subseteq D_{\sigma_i} \times D_{\delta_i}$  mapping iterations from the destination process domain back to the source process domain.

- a channel type  $T_i$ , which is *FIFO*, *sticky FIFO*, or *out-of-order* (cf. Section 2.3.1), and

- a piecewise quasipolynomial  $S_i$  representing the buffer size.

The parameters that occur in the process domains, channel maps and buffer sizes are *static*, meaning that their values are fixed at run-time. A more general model which

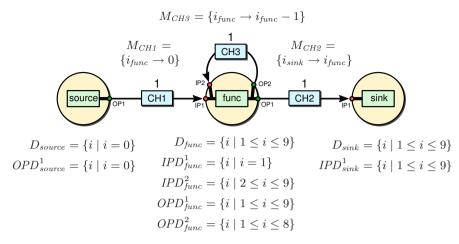

Figure 2.8: A polyhedral process network.

also includes *dynamic* parameters is the Parameterized Polyhedral Process Network (P<sup>3</sup>N) model [ZNS11]. Such dynamic parameters enable the P<sup>3</sup>N model to cope with applications that adapt their behavior at runtime. Another related model is the Approximated Dependence Graph (ADG) [SD03]. The ADG model supports the class of weakly dynamic programs, which is more generic than the class of static affine nested loop programs that we consider in this thesis.

In this thesis, we are dealing with instances of PPNs for which all static parameters have known fixed values. We replace the static parameters by their fixed values, thereby removing the parameters, for the sake of simplicity.

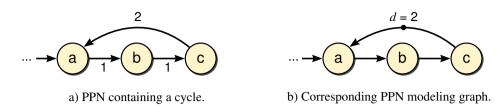

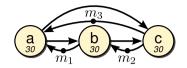

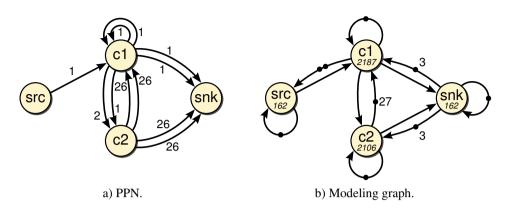

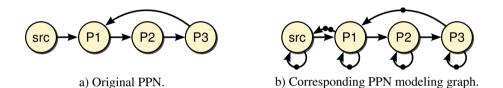

An example PPN consisting of three processes and three channels is depicted in Figure 2.8. In this thesis, we only consider PPNs that consist of exactly one *connected component*. That is, if one replaces all directed edges in the graph by undirected edges, then a path from u to v exists for every pair of vertices u, v. The PPNs that we consider may contain zero or more *strongly connected components*. A strongly connected component is a subgraph in which a path from any vertex in the subgraph to any other vertex in the subgraph exists.

If a process does not have any input ports, that is,  $IP_i = \emptyset$ , then the process is called a *source process*. Likewise, if a process does not have any output ports, that is,  $OP_i = \emptyset$ , then the process is called a *sink process*. The function of a process should be a *pure function*, that is, it should always yield the same output for a given input and it should not have any side effects. Exceptions to this requirement are source and sink processes, which often serve as an abstraction for the input and output interfaces of a system. As such, input and output operations are desired side-effects for functions of

source and sink processes.

In the PPN of Figure 2.8, *source* is a source process with one output port and *sink* is a sink process with one input port. The ports of a process are depicted by the dots on the border of each process. The output argument of the *source* function is connected to the output port of the process. Similarly, the input port of the *sink* process is connected to the input argument of the function. The *func* process has two input ports and two output ports. The *func* function has one input argument and one output argument. Both input ports connect to the same input argument and the output argument is connected to both output ports. Port multiplexing and demultiplexing is performed at run-time, as computations are distributed as a result of data flow analysis. Input and output tokens of a process need to be communicated from and to different processes at different iterations through process input and output ports.

The process and port domains are depicted below the processes in Figure 2.8. For example, the domain of the *sink* process consists of the integral points from 1 to 9. The IPD of its input port is identical to the process domain, which means that in every iteration a token is read from this input port.