# **Generalized strictly periodic scheduling analysis, resource optimization, and implementation of adaptive streaming applications** Niknam, S.

#### Citation

Niknam, S. (2020, August 25). *Generalized strictly periodic scheduling analysis, resource optimization, and implementation of adaptive streaming applications*. Retrieved from https://hdl.handle.net/1887/135946

| Version:         | Publisher's Version                                                                                                                    |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| License:         | <u>Licence agreement concerning inclusion of doctoral thesis in the</u><br><u>Institutional Repository of the University of Leiden</u> |

| Downloaded from: | https://hdl.handle.net/1887/135946                                                                                                     |

Note: To cite this publication please use the final published version (if applicable).

Cover Page

# Universiteit Leiden

The handle <u>http://hdl.handle.net/1887/135946</u> holds various files of this Leiden University dissertation.

Author: Niknam, S. Title: Generalized strictly periodic scheduling analysis, resource optimization, and implementation of adaptive streaming applications Issue Date: 2020-08-25

# Generalized Strictly Periodic Scheduling Analysis, Resource Optimization, and Implementation of Adaptive Streaming Applications

Sobhan Niknam

### Generalized Strictly Periodic Scheduling Analysis, Resource Optimization, and Implementation of Adaptive Streaming Applications

#### PROEFSCHRIFT

ter verkrijging van de graad van Doctor aan de Universiteit Leiden, op gezag van Rector Magnificus Prof.mr. C.J.J.M. Stolker, volgens besluit van het College voor Promoties te verdedigen op dinsdag 25 augustus 2020 klokke 15:00 uur

door

Sobhan Niknam geboren te Tehran, Iran in 1990

| Promotor:            | Dr. Todor Stefanov                                                                                                                                            | Universiteit Leiden                                                                                                    |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| Second-Promotor:     | Prof. dr. Harry Wijshoff                                                                                                                                      | Universiteit Leiden                                                                                                    |

| Promotion Committee: | Prof. dr. Akash Kumar<br>Prof. dr. Jeroen Voeten<br>Prof. dr. Paul Havinga<br>Prof. dr. Frank de Boer<br>Prof. dr. Aske Plaat<br>Prof. dr. Marcello Bonsangue | TU Dresden<br>TU Eindhoven<br>Universiteit Twente<br>Universiteit Leiden<br>Universiteit Leiden<br>Universiteit Leiden |

The research was supported by NWO under project number 12695 (CPS-3).

Generalized Strictly Periodic Scheduling Analysis, Resource Optimization, and Implementation of Adaptive Streaming Applications Sobhan Niknam. -Dissertation Universiteit Leiden. - With ref. - With summary in Dutch.

Copyright © 2020 by Sobhan Niknam. All rights reserved. This dissertation was typeset using LATEX.

ISBN: 978-90-9033402-8 Printed by Ipskamp Printing, Enschede.

To my family

# Contents

| Та | Table of Contentsvii |        |                                                         |      |

|----|----------------------|--------|---------------------------------------------------------|------|

| Li | st of 3              | Figure | 5                                                       | xi   |

| Li | st of '              | Tables |                                                         | xv   |

| Li | st of                | Abbrev | viations                                                | xvii |

| 1  | Intr                 | oducti | on                                                      | 1    |

|    | 1.1                  | Desig  | n Requirements for Embedded Streaming Systems           | 2    |

|    | 1.2                  | 0      | ls in Embedded Streaming Systems Design                 | 4    |

|    |                      | 1.2.1  | Multi-Processor System-on-Chip (MPSoC)                  | 4    |

|    |                      | 1.2.2  | Model-based Design                                      | 6    |

|    | 1.3                  | Two I  | mportant Design Challenges                              | 8    |

|    | 1.4                  | Resea  | rch Questions                                           | 9    |

|    |                      | 1.4.1  | Phase 1: Analysis                                       | 10   |

|    |                      | 1.4.2  |                                                         | . 11 |

|    |                      | 1.4.3  | Phase 3: Implementation                                 | 12   |

|    | 1.5                  | Resea  | rch Contributions                                       | 13   |

|    |                      | 1.5.1  | Generalized Strictly Periodic Scheduling Framework .    | 13   |

|    |                      | 1.5.2  | Algorithm to Find an Alternative Application Task Graph | L    |

|    |                      |        | for Efficient Utilization of Processors                 | 13   |

|    |                      | 1.5.3  | Energy-Efficient Periodic Scheduling Approach           | 14   |

|    |                      | 1.5.4  | MADF Implementation and Execution Approach              | 14   |

|    | 1.6                  | Thesis | s Outline                                               | 15   |

| 2  | Bac                  | kgroun | ıd                                                      | 17   |

|    | 2.1                  | Dataf  | low Models of Computation                               | 18   |

|    |                      | 2.1.1  | Cyclo-Static/Synchronous Data Flow (CSDF/SDF)           | 18   |

|    |                      | 2.1.2  | Mode-Aware Data Flow (MADF)                             | 20   |

|   | 2.2  | 0 5                                                                | 23<br>23   |

|---|------|--------------------------------------------------------------------|------------|

|   |      | •                                                                  | 23         |

|   |      |                                                                    | 24         |

|   | 2.3  |                                                                    | 28         |

|   | 2.4  |                                                                    | 30         |

| 3 | Har  | d Real-Time Scheduling of Cyclic CSDF Graphs                       | 35         |

|   | 3.1  |                                                                    | 35         |

|   | 3.2  |                                                                    | 36         |

|   | 3.3  |                                                                    | 37         |

|   | 3.4  | 1                                                                  | 38         |

|   | 3.5  | 1                                                                  | <b>1</b> 0 |

|   |      | 5                                                                  | 41         |

|   |      | 0 ,                                                                | <b>1</b> 5 |

|   | 3.6  | 1                                                                  | <b>1</b> 6 |

|   | 3.7  | Conclusions                                                        | <b>1</b> 9 |

| 4 | г    |                                                                    |            |

| 4 | -    | loiting Parallelism in Applications to Efficiently Utilize Proces- | -1         |

|   | SOTS |                                                                    | 51         |

|   | 4.1  |                                                                    | 52         |

|   | 4.2  |                                                                    | 53         |

|   | 4.3  |                                                                    | 54         |

|   | 4.4  | 8                                                                  | 57         |

|   |      | 0 1                                                                | 57         |

|   | 4 -  | 5                                                                  | 58         |

|   | 4.5  | 1                                                                  | 59         |

|   | 4.6  | 1 0                                                                | 53         |

|   | 4.7  | 1                                                                  | 57         |

|   |      | 0 1                                                                | 70         |

|   |      | 0 1                                                                | 73         |

|   | 4.8  | Conclusions                                                        | 76         |

| 5 | Ene  | rgy-Efficient Scheduling of Streaming Applications                 | 77         |

|   | 5.1  |                                                                    | 77         |

|   | 5.2  | Contributions                                                      | 78         |

|   | 5.3  | Related Work                                                       | 79         |

|   | 5.4  |                                                                    | 30         |

|   |      | 5.4.1 System Model                                                 | 31         |

|   |      | 5                                                                  | 31         |

|                      | 5.5     | Motivational Example                                            | 81          |

|----------------------|---------|-----------------------------------------------------------------|-------------|

|                      |         | 5.5.1 Applying VFS Similar to Related Works                     | 82          |

|                      |         | 5.5.2 Our Proposed Scheduling Approach                          | 84          |

|                      | 5.6     | Proposed Scheduling Approach                                    | 87          |

|                      |         | 5.6.1 Determining Operating Modes                               | 91          |

|                      |         | 5.6.2 Switching Costs $o_{HL}$ , $o_{LH}$ , $e_{HL}$ , $e_{LH}$ | 92          |

|                      |         | 5.6.3 Computing $Q_H$ and $Q_L$                                 | 95          |

|                      |         | 5.6.4 Memory Overhead                                           | 96          |

|                      | 5.7     | Experimental Evaluation                                         | 98          |

|                      |         | 5.7.1 Experimental Setup                                        | 98          |

|                      |         | 5.7.2 Experimental Results                                      | 99          |

|                      | 5.8     | Conclusions                                                     | 102         |

| 6                    | Imp     | lementation and Execution of Adaptive Streaming Applications    | <b>5103</b> |

|                      | 6.1     | Problem Statement                                               | 104         |

|                      | 6.2     | Contributions                                                   | 104         |

|                      | 6.3     | Related Work                                                    | 105         |

|                      | 6.4     | K-Periodic Schedules (K-PS)                                     | 106         |

|                      | 6.5     | Extension of the MOO Transition Protocol                        |             |

|                      | 6.6     | Implementation and Execution Approach for MADF                  | 110         |

|                      |         | 6.6.1 Generic Parallel Implementation and Execution Approach    |             |

|                      |         | 6.6.2 Demonstration of Our Approach on $LITMUS^{RT}$            | 112         |

|                      | 6.7     | Case Studies                                                    | 115         |

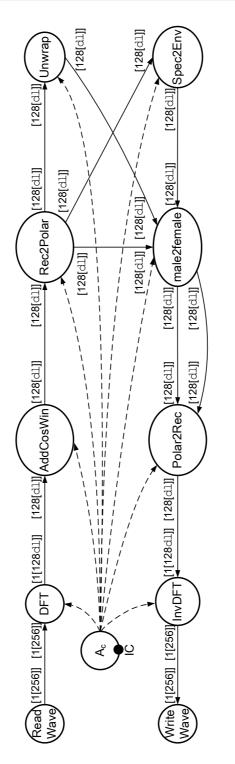

|                      |         | 6.7.1 Case Study 1                                              | 116         |

|                      |         | 6.7.2 Case Study 2                                              | 119         |

|                      | 6.8     | Conclusions                                                     | 122         |

| 7                    | Sum     | mary and Conclusions                                            | 123         |

| Bi                   | bliog   | raphy                                                           | 127         |

| Su                   | ımma    | ry                                                              | 137         |

| Sa                   | menv    | atting                                                          | 139         |

|                      |         | ů –                                                             |             |

| L19                  | st of l | Publications                                                    | 141         |

| Curriculum Vitae 143 |         |                                                                 |             |

| Acknowledgments 145  |         |                                                                 |             |

# **List of Figures**

| 1.1 | Samsung Exynos 5422 MPSoC [70]                                                                                                                                                         | 6  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Overview of the research questions and contributions in this thesis using a design flow.                                                                                               | 10 |

| 2.1 | Example of an MADF graph ( $G_1$ )                                                                                                                                                     | 20 |

| 2.2 | Two modes of the MADF graph in Figure 2.1.                                                                                                                                             | 20 |

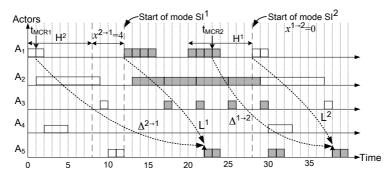

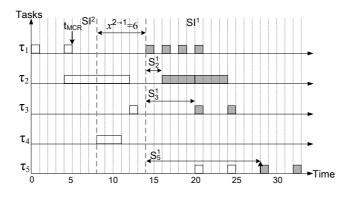

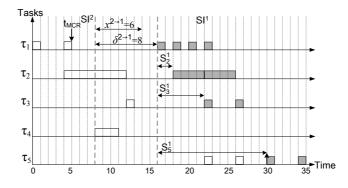

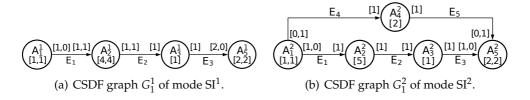

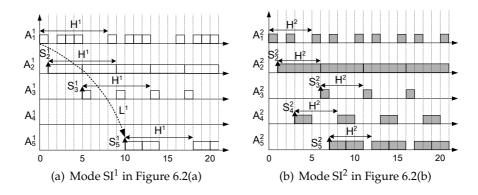

| 2.3 | Execution of two iterations of both modes $SI^1$ and $SI^2$ . (a) Mode $SI^1$ in Figure 2.2(a). (b) Mode $SI^2$ in Figure 2.2(b)                                                       | 22 |

| 2.4 | Execution of graph $G_1$ with two mode transitions under the MOO protocol.                                                                                                             | 22 |

| 2.5 | Execution of graph $G_1$ with a mode transition from mode SI <sup>2</sup> to mode SI <sup>1</sup> under the MOO protocol and the SPS framework                                         | 31 |

| 2.6 | Execution of graph $G_1$ with a mode transition from mode SI <sup>2</sup> to mode SI <sup>1</sup> under the MOO protocol and the SPS framework with task allocation on two processors. | 33 |

| 3.1 | A <b>cyclic</b> CSDF graph $G$ . The backward edge $E_5$ in $G$ has 2 initial tokens that are represented with black dots                                                              | 39 |

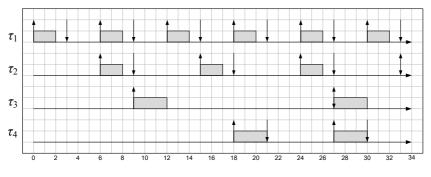

| 3.2 | The <i>SPS</i> of the CSDF graph <i>G</i> in Figure 3.1 without considering the backward edge $E_5$ . Up arrows are job releases and down                                              |    |

|     | arrows job deadlines                                                                                                                                                                   | 39 |

| 3.3 | The <i>GSPS</i> of the CSDF graph <i>G</i> in Figure 3.1                                                                                                                               | 40 |

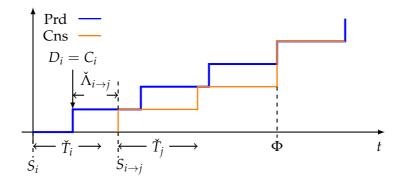

| 3.4 | Production and consumption curves on edge $E_u = (A_i, A_j)$                                                                                                                           | 41 |

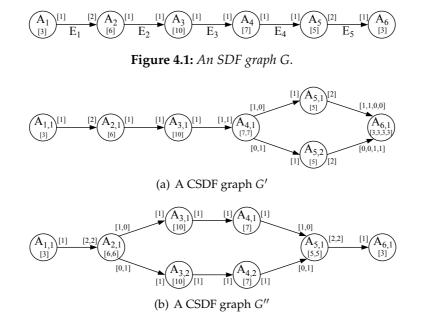

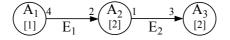

| 4.1 | An SDF graph G                                                                                                                                                                         | 58 |

| 4.2 | Equivalent CSDF graphs of the SDF graph $G$ in Figure 4.1 obtained by (a) replicating actor $A_5$ by factor 2 and (b) replicating actors $A_3$ and $A_4$ by factor 2                   | 58 |

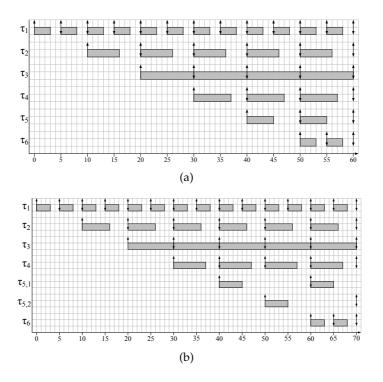

| 4.3 | A strictly periodic execution of tasks corresponding to the actors<br>in: (a) the SDF graph $G$ in Figure 4.1 and (b) the CSDF graph $G'$<br>in Figure 4.2(a). The x-axis represents the time.                                                                                                                                                     | 60  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

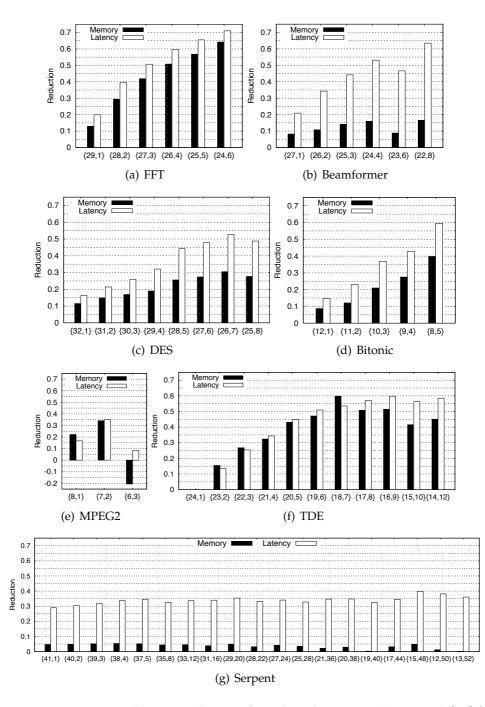

| 4.4 | Memory and latency reduction of our algorithm compared to<br>the related approach with the same number of processors                                                                                                                                                                                                                               | 71  |

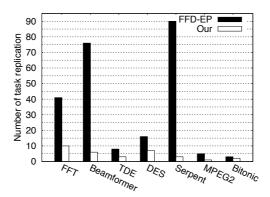

| 4.5 | Total number of task replications needed by FFD-EP and our proposed algorithm.                                                                                                                                                                                                                                                                     | 72  |

| 4.6 | Memory and latency reduction of our algorithm compared to EDF-sh [92] for real-life applications on different heterogeneous platforms.                                                                                                                                                                                                             | 74  |

| 5.1 | An SDF graph G                                                                                                                                                                                                                                                                                                                                     | 82  |

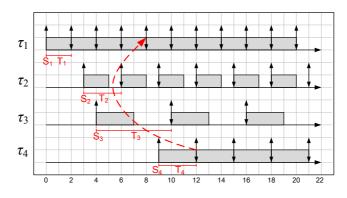

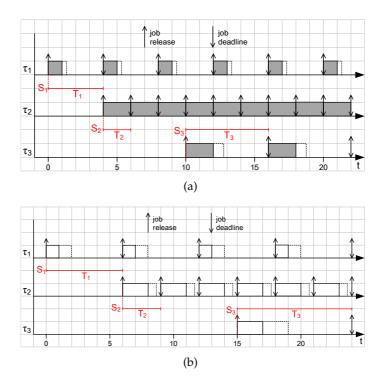

| 5.2 | The (a) SPS and (b) scaled SPS of the (C)SDF graph <i>G</i> in Figure 5.1. Up arrows represent job releases, down arrows represent job deadlines. Dotted rectangles show the increase of the tasks execution time when using the VFS mechanism.                                                                                                    | 83  |

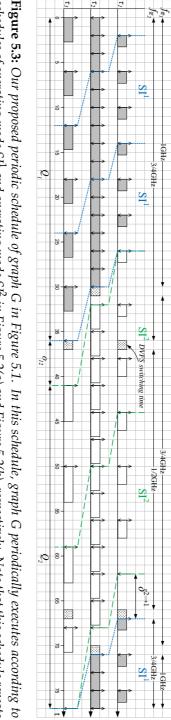

| 5.3 | Our proposed periodic schedule of graph <i>G</i> in Figure 5.1. In this schedule, graph <i>G</i> periodically executes according to schedules of operating mode SI <sup>1</sup> and operating mode SI <sup>2</sup> in Figure 5.2(a) and Figure 5.2(b), respectively. Note that this schedule repeats periodically. $o_{12} = 5$ and $o_{21} = 0$ . | 86  |

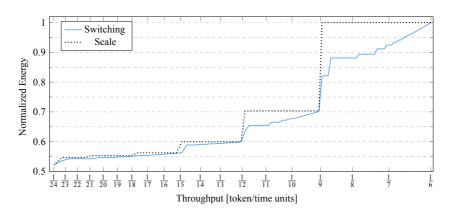

| 5.4 | Normalized energy consumption of the scaled scheduling and our proposed scheduling of the graph <i>G</i> in Figure 5.1 for a wide                                                                                                                                                                                                                  | 07  |

| 5.5 | <ul><li>range of throughput requirements</li></ul>                                                                                                                                                                                                                                                                                                 | 87  |

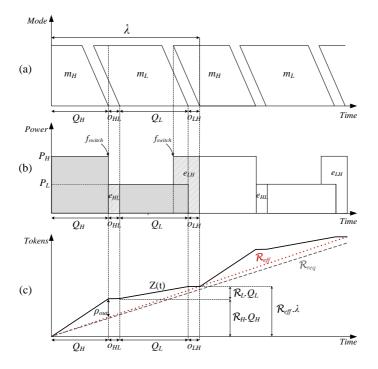

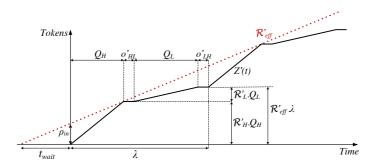

| 5.5 | the switching scheme and (c) Token production function Z(t).                                                                                                                                                                                                                                                                                       | 88  |

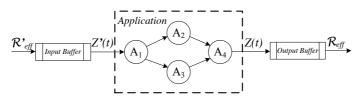

| 5.6 | Input and Output buffers.                                                                                                                                                                                                                                                                                                                          | 90  |

| 5.7 | Token consumption function $Z'(t)$ . Note that, $o_{HL} + o_{LH} = o'_{HL} + o'_{LH} = \delta^{H \to L} + \delta^{L \to H}$ .                                                                                                                                                                                                                      | 97  |

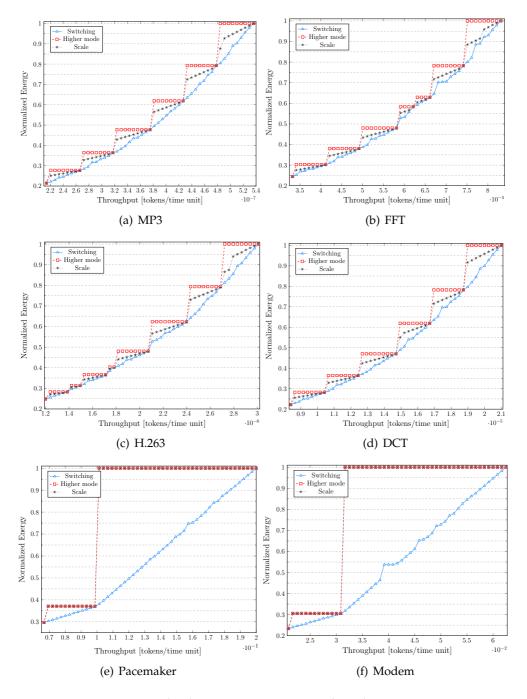

| 5.8 | Normalized energy consumption vs. throughput requirements.                                                                                                                                                                                                                                                                                         | 100 |

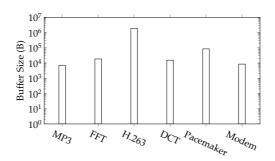

| 5.9 | Total buffer sizes needed in our scheduling approach for differ-<br>ent applications. Note that the y axis has a logarithmic scale                                                                                                                                                                                                                 | 101 |

| 6.1 | (a) An MADF graph $G_1$ (taken from Section 2.1.2). (b) The allocation of actors in graph $G_1$ on four processors                                                                                                                                                                                                                                 | 108 |

| 6.2 | Two modes of graph $G_1$ in Figure 2.1 (taken from Section 2.1.2 with modified WCET of the actors).                                                                                                                                                                                                                                                | 108 |

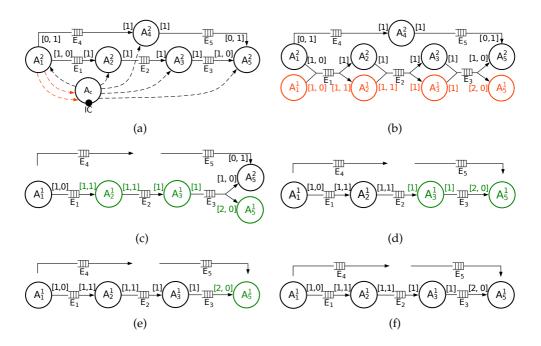

| 6.3 |                                                                                                                                                                                                                                                                                                                                                    | 109 |

| 6.4 | Execution of $G_1$ with two mode transitions under (a) the MOO                       |       |

|-----|--------------------------------------------------------------------------------------|-------|

|     | protocol, and (b) the extended MOO protocol with the allocation                      |       |

|     | shown in Figure 6.1(b).                                                              | 109   |

| 6.5 | Mode transition of $G_1$ from mode SI <sup>2</sup> to mode SI <sup>1</sup> (from (a) |       |

|     | to (f)). The control actor and the control edges are omitted in                      |       |

|     | figures (b) to (f) to avoid cluttering.                                              | . 111 |

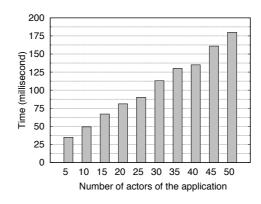

| 6.6 | MADF graph of the Vocoder application.                                               | . 117 |

| 6.7 | The execution time of control actor $A_c$ for applications with                      |       |

|     | different numbers of actors.                                                         | 119   |

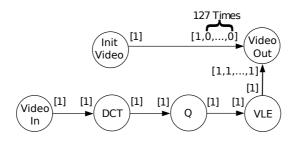

| 6.8 | CSDF graph of MJPEG encoder                                                          | 120   |

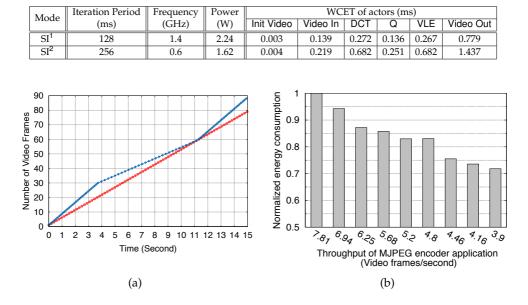

| 6.9 | (a) The video frame production of the MJPEG encoder applica-                         |       |

|     | tion over time for the throughput requirement of 5.2 frames/sec-                     |       |

|     | ond. (b) Normalized energy consumption of the application for                        |       |

|     | different throughput requirements                                                    | . 121 |

# **List of Tables**

| 2.1        | Summary of mathematical notations                                                                                                                                                                            | 17       |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 3.1<br>3.2 | Benchmarks used for evaluation                                                                                                                                                                               | 47<br>48 |

| 4.1        | Throughput $\mathcal{R}$ (1/time units), latency $\mathcal{L}$ (time units), memory requirements $\mathcal{M}$ (bytes), and number of processors m for $G$ under different scheduling/allocation approaches. | 63       |

| 4.2        | Benchmarks used for evaluation taken from [23]                                                                                                                                                               | 68       |

|            |                                                                                                                                                                                                              |          |

| 4.3<br>4.4 | Comparison of different scheduling/allocation approaches<br>Runtime (in seconds) comparison of different scheduling/allo-                                                                                    | 69       |

|            | cation approaches.                                                                                                                                                                                           | 73       |

| 5.1        | Operating modes for graph G                                                                                                                                                                                  | 85       |

| 5.2        | Benchmarks used for evaluation.                                                                                                                                                                              | 99       |

| 6.1        | Performance results of each individual mode of Vocoder                                                                                                                                                       | 116      |

| 6.2        | Performance results for all mode transitions of Vocoder (in ms).                                                                                                                                             | 118      |

| 6.3        | The specification of modes SI <sup>1</sup> and SI <sup>2</sup> in MJPEG encoder appli-                                                                                                                       |          |

|            | cation                                                                                                                                                                                                       | 121      |

# **List of Abbreviations**

| BFD      | Best-Fit Decreasing                      |

|----------|------------------------------------------|

| CDP      | Constrained-Deadline Periodic            |

| CSDF     | Cyclo-Static Data Flow                   |

| DSE      | Design Space Exploration                 |

| DVFS     | Dynamic VFS                              |

| EDF      | Earliest Deadline First                  |

| EE       | Energy Efficient                         |

| FFD      | First-Fit Decreasing                     |

| FFID-EDF | First-Fit Increasing Deadlines EDF       |

| FIFO     | First-In First-Out                       |

| GSPS     | Generalized Strictly Periodic Scheduling |

| HRT      | Hard Real-Time                           |

| IDP      | Implicit-Deadline Periodic               |

| MADF     | Mode-Aware Data Flow                     |

| MCR      | Mode Change Request                      |

| MoC      | Model of Computation                     |

| MOO      | Maximum-Overlap Offset                   |

|          |                                          |

MPSoC Multi-Processor System-on-Chip

| PE   | Performance Efficient        |

|------|------------------------------|

| RM   | Rate Monotonic               |

| RTOS | Real-time Operating System   |

| SDF  | Synchronous Data Flow        |

| SPS  | Strictly Periodic Scheduling |

| SRT  | Soft Real-Time               |

| TDP  | Thermal Design Power         |

| VFS  | Voltage-Frequency Scaling    |

| WCET | Worst-Case Execution Time    |

| WFD  | Worst-Fit Decreasing         |

# Chapter 1

# Introduction

**T** N the last few decades, tremendous developments in the field of electronics have made a significant impact on human lives. Nowadays, electronic systems have become an inevitable part of our modern-day life. They are prevalent and exist almost everywhere around us, even sometimes without noticing their presence, from our smartwatch, cell-phones, tablets to our cars and home appliances, improving the quality of our life from almost every aspect. For instance, thanks to the electronics technology, the patients' health status, e.g., vital signals such as ECG, EEG, and skin temperature, can be remotely monitored on a daily basis and accessed by hospital physicians using *wearable health-care monitoring devices* to diagnose medical symptoms like epilepsy or sleep disorders, e.g., e-Glass [77] for detection of epileptic seizures, while the patients can do their normal activities with no need of staying at a hospital or using a conventional clinical setting. As another example, we can refer to *advanced driver-assistance systems*, supporting vehicle drivers on the road and improving their safety and comfort. Examples of such systems include the active cruise control, which autonomously adjusts the distance to the front car, *the collision avoidance*, which warns and prompts the driver to prevent a collision with incoming unexpected obstacles, e.g., a pedestrian, and if needed autonomously brakes shortly before the collision when the driver is not responsive to the given warning, the rearview system, which increases the field of view for the driver, and many others.

In all of the above cases, each electronic system is enclosed into a larger entity like a device, product, or another system for which it provides a dedicated functionality. These electronic systems are known as **embedded systems**. Embedded systems are widespread in the world and use 98% of all processors according to recent studies [36,48]. The global market for embedded systems was valued over \$165 billion in 2015 and it is anticipated to be nearly \$260 billion by 2023 [1]. In this market, automotive and health-care embedded systems have gained the first- and second-largest share due to the increasing demand for smart vehicles and portable medical devices, respectively [1].

Different from general-purpose systems such as Personal Computers (PC), embedded systems are application-domain specific because they perform specific functions tightly coupled with the environment where they operate. They collect environmental information using sensors, process it, and perform an action accordingly using actuators. An important class of embedded systems is embedded streaming systems. Typically, these systems run software programs, called **streaming applications**, that process a continuous infinite, stream of data items coming from the environment. In these applications, data items in the stream are processed in-order using the same set of operations. Processing each data item takes a limited time and there is a little control flow between the operations. As a result, a continuous infinite, stream of data items are produced and fed into the environment. Examples of streaming applications include a wide range of applications from different application domains such as image processing, video/audio processing, network protocol processing, computer vision, navigation, digital signal processing, and many others. For instance, a popular streaming application, widely used in our daily life, on mobile phones, is watching a movie from YouTube. In such application, a video stream is continuously being received over the internet using a software defined radio protocol like WLAN, 3G, or 4G. Simultaneously, video and audio decoding like MPEG-4 and MP3 are performed on the received data stream and the decoded video and audio streams are continuously being played on the screen and speaker, respectively.

## 1.1 Design Requirements for Embedded Streaming Systems

In general, embedded systems are subjected to a wide range of strict design requirements compared to general-purpose systems. Some of these design requirements are common among all classes of embedded systems, including embedded streaming systems, while others are dependent on the environment where the embedded systems are deployed. In this section, we introduce explicitly the non-functional design requirements, i.e., timing, cost, and energy efficiency, that are considered in this thesis. Functional requirements, such as deadlock-free execution, etc., are implicitly considered as well.

For many embedded systems, the *timing* is a critical design requirement. In

such systems, the correct *behavior* depends not only on producing the correct output but also on whether the output is produced before a *deadline*. This timing requirement for the correct behavior of embedded systems is called a **real-time requirement** and a system with real-time requirements is called a **real-time system**. Regarding the criticality of a failure to satisfy the realtime requirements, the real-time systems can be classified into the following categories:

- **Soft Real-Time (SRT) Systems**: not always satisfying the real-time requirements does not lead to a system failure but only degrades the system performance provided that the deadline misses are within a certain threshold which the system can tolerate.

- Hard Real-Time (HRT) Systems: not always satisfying the real-time requirements leads to a system failure, which can have catastrophic consequences in safety- or life-critical systems.

For instance, in a video system which is an example of a SRT system, to watch a video smoothly through YouTube, a huge amount of data should be received regularly over the internet and processed in a short period of time. Otherwise, the video is played slow-motion, blurry, and jerky which greatly degrades the user experience. In contrast, in a HRT system such as the collision avoidance system found in a smart car, the collected data from camera and laser sensors mounted on the car must be processed always within a pre-defined and fixed time interval, such that the car can detect an incoming obstacle and react in time to avoid a collision. Otherwise, catastrophic consequences can happen, e.g., loss of human life. In the case of embedded streaming systems, timing requirements that are typically considered and guaranteed are **throughput** and/or **latency**. The throughput represents the rate at which the output is produced by a streaming application, whereas the latency represents the elapsed time between the arrival of a data item to the application and the output of the processed data item by the application.

For high-volume embedded systems, especially in consumer electronics, keeping the *cost* of a system competitive in mass markets is extremely important for survival [57]. Therefore, embedded system designers should make efficient use of hardware resources (i.e., processors, memories, etc.), either by reducing the amount of resources needed to implement a required functionality or by utilizing the available resources on a single hardware platform efficiently by running as many required applications as possible. In the latter case, different applications may share resources. Such resource sharing, however, should not affect the timing requirements and guarantees for the different applications. This property is known as *temporal isolation*, that is, the

ability to start or stop applications at run-time without violating the timing requirements of other concurrently running applications on a shared hardware platform.

Usually, embedded systems operate using stand-alone power supply such as batteries. As frequently replacing/recharging the batteries is not desirable/possible for many embedded systems, the *energy efficiency* is another important design requirement in order to prolong the operational time of such systems on a single battery charge.

### 1.2 Trends in Embedded Streaming Systems Design

At the beginning of this chapter, we have introduced the embedded systems and explained their importance in our daily life. We have also pointed out, in Section 1.1, the set of non-functional design requirements for embedded streaming systems, considered in this thesis. In this section, therefore, we discuss the current trends in designing embedded streaming systems to satisfy the aforementioned design requirements.

#### 1.2.1 Multi-Processor System-on-Chip (MPSoC)

Traditionally, embedded (streaming) systems were implemented on top of uniprocessors for a long period of time. Following the same trend as in general-purpose systems, the embedded (streaming) systems designers relied on enhancing the computational power of uniprocessors by scaling up their operational clock frequency as well as employing advanced micro-architectural innovations, such as pipelining, branch prediction, out-of-order execution, cache memory hierarchy and others, to satisfy the tight timing requirements, i.e., high throughput and/or low latency, in streaming applications [41]. This enhancement of the computational power had been driven by the fast development of the technology node which had enabled chip manufacturers to produce thinner and faster transistors, the fundamental elements in digital electronic circuits, and made it possible to integrate more and more transistors on a chip, as the result of the *Moore's Law*<sup>1</sup> coupled with the *Dennard scaling*<sup>2</sup> [68]. However, by reaching a technology node below 100 nanometers,

<sup>&</sup>lt;sup>1</sup>Moore's Law refers to Moore's prediction in 1965 that the number of transistors on a chip doubles every 18 months.

<sup>&</sup>lt;sup>2</sup>In 1974, Dennard *et al.* [30] postulated that the power density in a chip remains roughly constant by scaling the transistor size from one technology node to another, widely known as "*Dennard Scaling*", i.e., the power consumption of transistors scales down as long as their size is reduced.

the *Dennard's Scaling* fails due to the extremely increased leakage power consumption of transistors, i.e., the consumed power caused by currents that leak through transistors when transistors are idle. In addition, when the size of transistors decreases, their density increases on a chip resulting in increased on-chip power density which leads to overheating issues and makes on-chip thermal hotspots [73]. To avoid the overheating issues, the power consumption of chips is constrained severely with a safe power level, called *thermal design power* (TDP), provided by chip manufacturers [59]. To keep the power consumption within the TDP budget, uniprocessors have to operate at a lower operational clock frequency instead of the maximum possible frequency [59]. Moreover, the usage of many micro-architectural innovations in uniprocessors quickly reached the point of diminishing return in performance and increased design complexity. As a consequence, chip manufacturers were forced to look for an alternative to the uniprocessor paradigm.

As a solution to enhance the system performance even further while coping with the aforementioned high power consumption, chip manufacturers have shifted their design scheme towards multi-processor platforms in order to effectively utilize the growing number of transistors on a chip. In such platforms, the issue of increased power consumption has been partially resolved by replacing a complex processor running at a high operational voltage and clock frequency with multiple relatively simpler processors running at a lower operational voltage and clock frequency. In this way, the system performance can be enhanced through parallel processing while keeping the power and complexity under control. Nowadays, due to the advances in the chip fabrication technology, embedded system designers can integrate all components, including multiple processors, memories, interconnections, and other hardware peripherals, necessary for an application into a single chip, the so-called Multi-Processor System-On-Chip (MPSoC) [44]. Indeed, MPSoCs are a suitable way of implementing embedded streaming systems as they can provide high-performance, timing guaranteed, low-cost, compact, light, and low power/energy products. To further reduce the power/energy consumption, MPSoC platforms are usually armed with a Voltage and Frequency Scaling (VFS) mechanism [71]. In general, a VFS mechanism trades performance for power/energy consumption by adjusting the voltage and operating frequency of processors.

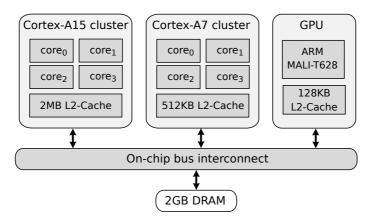

An example of an MPSoC is the Samsung Exynos 5 Octa (5422) [70], shown in Figure 1.1, which can be found in the Samsung Galaxy S5 mobile phones. This MPSoC is based on the big.LITTLE architecture [40] and has one cluster of four performance-efficient ARM Cortex-A15 cores and one cluster of four

Figure 1.1: Samsung Exynos 5422 MPSoC [70].

energy-efficient Cortex-A7 cores. Additionally, it has the ARM Mali-T628 GPU containing 6 cores for graphical processing and 2GB DRAM on-chip memory. All the processors are connected through an on-chip bus interconnect. For the Cortex-A15 cluster, the frequency can be varied between 200 MHz to 2000 MHz whereas for the Cortex-A7 cluster, it can be varied between 200 MHz to 1400 MHz, with a step of 100 MHz in both clusters. Note that the voltage is adjusted by the firmware automatically according to pre-set pairs of voltage-frequency values.

#### 1.2.2 Model-based Design

To satisfy the tight timing requirements of streaming applications (introduced in Section 1.1), the computational capacity of MPSoC platforms (introduced in Section 1.2.1) must be efficiently exploited. To facilitate this, streaming applications must be expressed primarily in a parallel fashion. The common practice for expressing the parallelism in an application is to use parallel **Models of Computation (MoCs)** in which the application is specified, at a high level of abstraction, as a set of parallel or concurrent tasks with specific communication and synchronization semantics. In particular, a parallel MoC defines, in a formal way, the rules by which the tasks of an application compute, communicate, and synchronize among each other. As a consequence, adopting MoCs during a design process enables system designers to reason about both functional and non-functional properties of an application. A design process which exploits MoCs is called **Model-based Design**.

In the past three decades, a variety of parallel MoCs have been proposed [43, 53]. This variety enables designers to choose the most suitable

parallel MoCs for the considered application domain. For streaming applications, that are the main focus of this thesis, dataflow MoCs have been identified as the most suitable parallel MoCs [88]. Within a dataflow MoC, a streaming application is modeled as a directed graph, where the graph nodes represent the application tasks and the graph edges represent data dependencies among the tasks. Thus, the parallelism is explicitly specified in the model. In general, dataflow MoCs differ among each other by their *expressiveness*, analyzability, and implementation efficiency [86]. The expressiveness of a model indicates what type of applications the model is capable of modeling and how compact the model is. The analyzability of a model is determined by the availability of design-time analysis techniques for checking (non-)functional requirements of the modeled application, e.g., liveness<sup>3</sup>, boundedness<sup>4</sup>, and throughput/latency, as well as by the computational complexity of the analysis techniques. Finally, the implementation efficiency of a model is influenced by the complexity of the scheduling problem and the code size of the resulting schedules. Basically, the expressiveness and analyzability are inversely related, meaning that, MoCs with high expressiveness exhibit low analyzability, and vice versa. Similarly, MoCs with high expressiveness generally have lower implementation efficiency. Therefore, there is no a single MoC which performs superior among all existing MoCs in all of the three aforementioned criteria. Consequently, designers have to choose a suitable MoC depending on their needs. A detailed and complete comparison of different dataflow MoCs is provided in [86,93].

In this thesis, we use two well-known dataflow MoCs to specify streaming applications, namely, Synchronous Data Flow (SDF) [52] and its generalization Cyclo-Static Data Flow (CSDF) [16], due to their high analyzability. For these MoCs, various powerful analysis methods have been developed over the past two decades to evaluate liveness/boundedness [34], to compute throughput/latency [9,10,19,35,56,78,82], buffer sizes [9,10,78,85,91], and so on. These MoCs are mainly suitable and used to specify streaming applications with static behavior. But, modern streaming applications may exhibit adaptive/dynamic behavior at run-time. For example, a computer vision system processes different parts of an image continuously to obtain information from several regions of interest depending on the actions taken by the external environment [94]. To model such adaptive behavior while having a certain degree of

<sup>&</sup>lt;sup>3</sup>An application is *live* if each task of the application can execute infinitely, i.e., no deadlock occurs.

<sup>&</sup>lt;sup>4</sup>An application is *bounded* if the application can execute infinitely with a bounded amount of memory needed for communication/synchronization among its tasks, i.e., no buffer overflow occurs.

analyzability, in this thesis, we use a more expressive dataflow MoC, namely, Mode-Aware Data Flow (MADF) [94], which is proposed and deployed as an extension of the CSDF MoC, as well. MADF can capture the behavior of an adaptive streaming application as a collection of different static behaviors, called *modes*, which are individually analyzable at design-time. The formal definitions of the aforementioned dataflow MoCs are given in Chapter 2.

### 1.3 Two Important Design Challenges

Although dataflow MoCs resolve the problem of explicitly exposing the available parallelism in an application, two challenges remain, namely, how to execute the tasks of a dataflow-modeled application spatially, i.e., task mapping<sup>5</sup>, and temporally, i.e., task scheduling, on an MPSoC platform such that all timing requirements are satisfied while making efficient utilization of available resources (e.g, processors, memory, energy, etc.) on the platform. More precisely, the task mapping determines how tasks are distributed among the processors whereas the task scheduling determines the time periods in which each task is executed on a processor. These two challenges have been identified as two of the most urgent design challenges needed to be solved for implementing embedded systems [58,75]. To address these challenges, several scheduling policies have been proposed for streaming applications, specified using dataflow MoCs and executed on MPSoC platforms. For a long period of time, self-timed scheduling was considered as the most appropriate scheduling policy for streaming applications [51]. Under self-timed scheduling, a task executes as soon as possible when its input data is ready. This scheduling policy, however, has two significant drawbacks: 1) it does not provide temporal isolation (introduced in Section 1.1) among applications concurrently running on a shared MPSoC platform; 2) it needs a complex design space exploration (DSE) to determine the minimum number of required processors and the mapping of tasks to these processors in an MPSoC platform such that all timing requirements are satisfied.

In contrast, many scheduling algorithms from the classical hard real-time scheduling theory for multiprocessors [21, 29] have the following attractive properties: 1) the minimum number of processors needed to schedule a certain set of tasks and their mapping on processors can be calculated in a fast, yet accurate analytical way; 2) temporal isolation among different applications is guaranteed; 3) fast admission and scheduling decisions for new incoming applications can be performed at run-time. In these scheduling algorithms,

<sup>&</sup>lt;sup>5</sup>Also referred as *tasks allocation* in the literature. Both are used interchangeably in this thesis.

the tasks of an application are specified using a *real-time task model*. The most influential example of such a task model is the *periodic real-time* task model [54] in which a task is invoked in a strictly periodic way, with a constant interval between invocations. Each task invocation has a constant execution time which must be completed before a certain deadline. These scheduling algorithms, however, typically assume sets of *independent* periodic or sporadic tasks. Thus, such a simple task model is not directly applicable to streaming applications that have data-dependent tasks.

In recent years, several approaches [8–10,78,79] have been proposed to bridge the gap between the dataflow MoCs that support data-dependent tasks and the classical hard real-time scheduling theory which mainly considers independent periodic/sporadic tasks. Using these approaches, the dependent tasks of an application, specified by an *acyclic* CSDF graph, can be converted to a set of real-time periodic tasks. Therefore, this conversion enables the utilization of many scheduling algorithms from the classical hard real-time scheduling theory that offer properties such as temporal isolation and fast calculation of the number of processors needed to guarantee the required performance. Motivated by the above discussion, we use the approach proposed in [8] as a basis and research driver in this thesis.

### 1.4 Research Questions

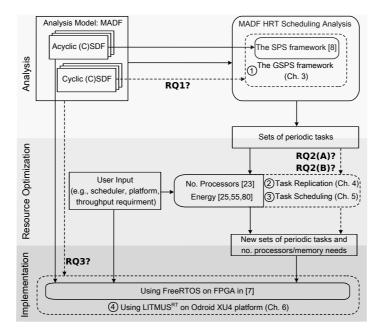

After introducing some important requirements, trends, and challenges in the design of embedded streaming systems in Section 1.1, Section 1.2, and Section 1.3, respectively, in this section, we formulate the specific research questions addressed in this thesis concerning the design of embedded streaming systems. Recall that we consider the scheduling framework proposed in [8], namely the so-called strictly periodic scheduling (SPS) framework, as the basis and research driver in this thesis. To easily introduce the research questions, addressed in this thesis, and the logical connection between them, a design flow which incorporates the SPS framework, as the main component, is illustrated in Figure 1.2. The design flow involves three phases, namely, analysis, resource optimization, and implementation, each of them highlighted with a different color. The rectangular boxes represent the input(s)/output(s) to/from each phase of the design flow, whereas the ellipsoid boxes represent the operations performed in the phases. The dashed lines and boxes denote the research questions and contributions of this thesis, respectively. In the following subsections, we shortly explain each phase of the design flow and introduce the research question belonging to each phase.

**Figure 1.2:** Overview of the research questions and contributions in this thesis using a design flow.

#### 1.4.1 Phase 1: Analysis

The input to the first phase of the design flow is an adaptive streaming application specified using the MADF MoC [94]. Note that if the application has static behavior, its MADF specification has only one mode which is specified by a (C)SDF graph. Then, a HRT scheduling analysis is performed on the (C)SDF specification of each mode of the application using the SPS framework [8]. The result of this analysis is a derived set of periodic tasks for each mode of the application. To verify whether the timing requirements of the application are satisfied, a HRT analysis for the application execution during mode transitions, when the application's behavior is switching from one mode to another one, is provided in [94].

The SPS framework, however, as mentioned in Section 1.3, only accepts, as input, streaming applications specified as *acyclic* CSDF graphs, thereby enabling the utilization of many scheduling algorithms from classical hard real-time scheduling theory only for *acyclic* CSDF graphs. Consequently, these well-developed hard real-time scheduling algorithms cannot be applied to many streaming applications that are specified as **cyclic** CSDF graphs, i.e., graphs where the tasks have cyclic data dependencies. Thus, we formulate

the first research question addressed in this thesis as follows.

RQ1: How to apply the hard real-time scheduling theory to streaming applications, specified as CSDF graphs, with cyclic dependencies?

#### 1.4.2 Phase 2: Resource Optimization

The inputs to the second phase of the design flow are sets of periodic tasks, derived in the first phase, and some user inputs such as the platform on which the tasks will execute, the (hard) real-time scheduling algorithm used to schedule the tasks on the platform, and timing requirements (e.g., throughput). Then, in this phase, the number of required processors on the platform and the task mapping for each mode of the application are analytically computed using the scheduling algorithm, selected by the user, such that all timing requirements are satisfied. The outputs of this phase are a new derived sets of periodic tasks along with their task mapping, number of processors required to satisfy the timing requirements, and the memory needed for data communication/synchronization among the tasks.

Regarding the design requirements, mentioned in Section 1.1, in this phase, further improvements can be performed on the tasks mapping and scheduling to more efficiently utilize the limited resources, i.e., the number of processors and energy budget, available on the platform. To this end, several task mapping and scheduling approaches using the SPS framework have been proposed in [23, 25, 55, 80]. As the computational capacity of the processors is underutilized under partitioned scheduling algorithms<sup>6</sup> due to the capacity fragmentation issue, i.e., no single processor has sufficient remaining capacity to schedule any other task in spite of the existence of a total large amount of unused capacity on the platform, a mapping and scheduling approach is proposed in [23] to more efficiently exploit the computational capacity of the processors by allowing only certain tasks to migrate between multiple processors while the rest of the tasks are statically allocated on the processors. Although this approach can result in better processor utilization, it increases the memory needs and latency of the application significantly. Thus, we formulate the second research question addressed in this thesis as follows.

RQ2(A): How to alleviate the capacity fragmentation issue introduced by partitioned scheduling algorithms and reduce the number of processors required for an application with a given throughput requirement while imposing less overhead on the memory needs and latency of the application?

<sup>&</sup>lt;sup>6</sup>Where periodic tasks of an application are statically mapped on the processors, as introduced in Section 2.2.3 on page 24.

To achieve energy efficiency, [25, 55, 80] propose energy-efficient task mapping and scheduling approaches using the VFS mechanism mentioned in Section 1.2.1. The general idea behind these approaches is to efficiently exploit available idle (i.e., slack) times in the schedule of an application in order to slow down the execution of running tasks of the application by using the VFS mechanism to reduce the energy consumption while satisfying the throughput requirement of the application. By using the SPS framework, however, only a set of application throughputs can be guaranteed for the application. Therefore, given a required application throughput that is not in the set of guaranteed throughputs by the SPS framework, the mapping and schedule that provide the closest higher throughput to the required one must be selected from the set. This, however, reduces the amount of slack time in the schedule of the application that can be potentially exploited using the VFS mechanism to reduce the energy consumption. Thus, we formulate the third research question addressed in this thesis as follows.

RQ2(B): How to exploit more slack times in the schedule of an application with a given throughput requirement using the VFS mechanism to achieve more energy efficiency?

#### 1.4.3 Phase 3: Implementation

Finally, the third phase of the design flow, shown in Figure 1.2, is to implement and execute the analyzed application on an MPSoC platform. The inputs to this phase are the MADF-modeled application, the selected MP-SoC platform, scheduling algorithm, and timing requirements by the user, and the sets of periodic tasks derived in the second phase along with their task mapping, number of required processors, and memory needs for data communication/synchronization among the tasks. Note that since the SPS framework converts an application into a set of real-time periodic tasks, the implementation and execution of the application must be performed on top of a real-time operating system (RTOS) which provides real-time multiprocessor scheduling algorithms (e.g., Earliest Deadline First (EDF) or Rate Monotonic (RM)) needed to schedule the periodic tasks on the MPSoC platform. In this regard, [7] adopts the FreeRTOS [72], which is an open-source RTOS, and proposes an implementation and execution approach for static streaming applications, specified as acyclic (C)SDF graphs, running on a Xilinx FPGA board. Concerning adaptive streaming applications, modeled and analyzed with the MADF MoC, however, no attention has been paid so far at this implementation phase. Thus, we formulate the fourth research question addressed in this thesis as follows.

RQ3: How to implement and execute an adaptive streaming application, modeled and analyzed with the MADF MoC, on an MPSoC platform, such that the properties of the analyzed model are preserved?

## 1.5 Research Contributions

To address the research questions, outlined in Section 1.4, this thesis provides four research contributions represented as the dashed boxes in Figure 1.2. We summarize these research contributions in the following sub-sections.

#### 1.5.1 Generalized Strictly Periodic Scheduling Framework

To address research question **RQ1**, we propose a novel scheduling framework, called Generalized Strictly Periodic Scheduling (GSPS), published in [64] and presented in Chapter 3, that can handle cyclic (C)SDF graphs. To this end, we first propose a sufficient test to check for the existence of a strictly periodic schedule for a streaming application modeled as a cyclic (C)SDF graph. If a strictly periodic schedule exists for the application, the tasks of the application are converted to a set of periodic tasks by computing their periods, deadlines, and earliest start times. As a consequence, this conversion enables the utilization of many well-developed HRT scheduling algorithms [21,29] on streaming applications modeled as cyclic (C)SDF graphs to benefit from the properties of these algorithms such as HRT guarantees, fast admission control, temporal isolation, and fast calculation of the number of required processors. The experimental results, on a set of real-life benchmarks, demonstrate that our approach can schedule the tasks in an application, modeled as a cyclic CSDF graph, with guaranteed throughput equal or comparable to the throughput obtained by existing scheduling approaches while providing HRT guarantees for every task in the application thereby enabling temporal isolation among concurrently running tasks/applications on a multi-processor platform.

#### 1.5.2 Algorithm to Find an Alternative Application Task Graph for Efficient Utilization of Processors

To address research question **RQ2(A)**, we propose a novel algorithm, published in [63] and presented in Chapter 4, to find an alternative application task graph that exposes more parallelism, particularly in the form of data-level parallelism, while preserving the same application behavior and throughput. This is needed due to the fact that a given initial application task graph is not

the most suitable one for a given MPSoC platform because the application developers, providing the initial graph, typically focus on realizing certain application behavior while neglecting the efficient utilization of the available resources on MPSoC platforms. Therefore, the main innovation in our proposed algorithm is that by using the unfolding graph transformation, introduced in Section 4.4.1, we propose a method to determine a replication factor for each task of an application, specified as an acyclic SDF graph, such that the distribution of the workloads among more parallel tasks, in the obtained graph after the transformation, results in a better resource utilization, which can alleviate the capacity fragmentation introduced by partitioned scheduling algorithms, hence reducing the number of required processors. The experimental results, on a set of real-life streaming applications, demonstrate that our approach can reduce the minimum number of processors required to schedule an application while imposing considerably less overhead, i.e., an average of up to 31.43% and 44.09% less overhead in terms of memory needs and application latency, respectively, compared to related approaches while satisfying the same throughput requirement.

#### 1.5.3 Energy-Efficient Periodic Scheduling Approach

To address research question **RQ2(B)**, we propose a novel energy-efficient periodic scheduling approach, published in [62] and presented in Chapter 5. In this approach, the execution of an application, specified as a CSDF graph, is periodically switched at run-time between a few off-line determined energy-efficient schedules in order to satisfy the application throughput requirement in a long run. As a result, this approach can reduce the energy consumption significantly by exploiting slack times in the schedules of the application more efficiently using a Dynamic VFS (DVFS) mechanism, where multiple voltage and operating frequencies are selected at design-time for the processors to be periodically switched at run-time. The experimental results, on a set of real-life streaming applications, show that our novel scheduling approach can achieve up to 68% energy reduction depending on the application and the throughput requirement compared to related approaches.

#### 1.5.4 MADF Implementation and Execution Approach

To address research question **RQ3**, we propose a generic parallel implementation and execution approach, published in [65] and presented in Chapter 6, for adaptive streaming applications, specified and analyzed using the MADF MoC. Our implementation and execution approach conforms to the analysis model and its operational semantics. We demonstrate our approach using LITMUS<sup>RT</sup> [22] which is one of the existing real-time extensions of the Linux kernel. To show the practical applicability of our parallel implementation and execution approach and its conformity to the analysis model, we present a case study where we implement and execute a real-life adaptive streaming application on the Odroid XU4 platform [66] with LITMUS<sup>RT</sup>. Odroid XU4 features the MPSoC shown in Figure 1.1.

### 1.6 Thesis Outline

Below, we give an outline of this thesis, summarizing the contents of the following chapters.

**Chapter 2** presents an overview of the dataflow MoCs considered in this thesis, some relevant analysis techniques from the hard real-time (HRT) scheduling theory, and the HRT scheduling analysis of (C)SDF and MADF graphs. All of these concepts and techniques are necessary to understand the contributions of this thesis.

Chapter 3 to Chapter 6 contain the main contributions of this thesis. Each chapter is organized in a self-contained way, meaning that each chapter contains a more specific introduction to the addressed problem, a related work, the proposed solution approach, an experimental evaluation, and a concluding discussion.

**Chapter 3** presents our novel HRT scheduling framework, called GSPS, for streaming applications modeled as cyclic (C)SDF graphs. This chapter is based on our publication [64].

**Chapter 4** presents our novel algorithm to optimize the number of processors needed for executing streaming applications modeled as acyclic SDF graphs under partitioned scheduling algorithms. This chapter is based on our publication [63].

**Chapter 5** presents our energy-efficient periodic scheduling approach for streaming applications modeled as (C)SDF graphs. This chapter is based on our publication [62].

**Chapter 6** presents the final contribution of this thesis, which is our parallel implementation and execution approach for adaptive streaming applications modeled as MADF graphs. This chapter is based on our publication [65].

Finally, **Chapter 7** ends this thesis by providing a summary of the research works done in this thesis along with some conclusions.

# **Chapter 2**

# Background

THIS chapter is dedicated to an overview of the background material needed to understand the novel research contributions of this thesis presented in the following chapters. We first provide a summary of some mathematical notations used throughout this thesis in Table 2.1.

| Symbol              | Meaning                                                         |

|---------------------|-----------------------------------------------------------------|

| $\mathbb{N}$        | The set of natural numbers excluding zero                       |

| $\mathbb{N}_0$      | $\mathbb{N} \cup \{0\}$                                         |

| Z                   | The set of integers                                             |

| <i>x</i>            | The cardinality of a set <i>x</i>                               |

| $\lceil x \rceil$   | The smallest integer that is greater than or equal to $x$       |

| $\lfloor x \rfloor$ | The greatest integer that is smaller than or equal to $x$       |

| x                   | The maximum value of <i>x</i>                                   |

| ž                   | The minimum value of <i>x</i>                                   |

| $\vec{x}$           | The vector <i>x</i>                                             |

| lcm                 | The least common multiple operator                              |

| mod                 | The integer modulo operator                                     |

| xV                  | An <i>x</i> -partition of a set <i>V</i> (see Definition 2.2.1) |

**Table 2.1:** Summary of mathematical notations.

Then, in Section 2.1, we present the dataflow MoCs that are used in this thesis. In Section 2.2, we present some results and definitions from the hard real-time (HRT) scheduling theory relevant to the context of this thesis. Finally, in Section 2.3 and 2.4, we describe the HRT analysis for the adopted dataflow MoCs.

### 2.1 Dataflow Models of Computation

As mentioned in Section 1.2.2, dataflow MoCs have been identified as the most suitable parallel MoCs to express the available parallelism in streaming applications. In this section, we present the dataflow MoCs considered in this thesis, that is, the CSDF and SDF MoCs are given in Section 2.1.1 and the MADF MoC is given in Section 2.1.2.

### 2.1.1 Cyclo-Static/Synchronous Data Flow (CSDF/SDF)

An application modeled as a CSDF [16] is defined as a directed graph  $G = (\mathcal{A}, \mathcal{E})$ . *G* consists of a set of actors  $\mathcal{A}$ , which corresponds to the graph nodes, that communicate with each other through a set of communication channels  $\mathcal{E} \subseteq \mathcal{A} \times \mathcal{A}$ , which corresponds to the graph edges. Actors represent computations while communication channels represent data dependencies among actors. A communication channel  $E_u \in \mathcal{E}$  is a first-in first-out (FIFO) buffer and it is defined by a tuple  $E_u = (A_i, A_j)$ , which implies a directed connection from actor  $A_i$  (called *source*) to actor  $A_j$  (called *destination*) to transfer data, which is divided in atomic data objects called *tokens*. An actor receiving an input data stream of the application from the environment is called *input actor*.

An actor fires (executes) when there are enough tokens on all of its input channels. Every actor  $A_i \in \mathcal{A}$  has an *execution sequence*  $[f_i(1), f_i(2), \cdots, f_i(\phi_i)]$ of length  $\phi_i$ , i.e., it has  $\phi_i$  phases. This means that the execution of each phase  $1 \leq \phi \leq \phi_i \in \mathbb{N}$  of actor  $A_i$  is associated with a certain function  $f_i(\phi)$ . As a consequence, the execution time of actor  $A_i$  is also a sequence  $[C_i(1), C_i(2), \dots, C_i(\phi_i)]$  consisting of the worst-case execution time (WCET) values for each phase. Every output channel  $E_u$  of actor  $A_i$  has a predefined token *production sequence*  $[x_i^u(1), x_i^u(2), \dots, x_i^u(\phi_i)]$  of length  $\phi_i$ . Analogously, token consumption from every input channel  $E_u$  of actor  $A_i$  is a predefined sequence  $[y_i^u(1), y_i^u(2), \cdots, y_i^u(\phi_i)]$ , called *consumption sequence*. Therefore, the *k*-th time that actor  $A_i$  is fired, it executes function  $f_i(((k-1) \mod \phi_i) + 1))$ , produces  $x_i^u(((k-1) \mod \phi_i) + 1)$  tokens on each output channel  $E_u$ , and consumes  $y_i^u((k-1) \mod \phi_i) + 1)$  tokens from each input channel  $E_u$ . The total number of produced tokens by actor  $A_i$  on channel  $E_u$  during its first ninvocations and the total number of consumed tokens from the same channel by  $A_i$  during its first *n* invocations are  $X_i^u(n) = \sum_{l=1}^n x_i^u(((l-1) \mod \phi_i) + 1)$ and  $Y_i^u(n) = \sum_{l=1}^n y_i^u(((l-1) \mod \phi_i) + 1)$ , respectively.

An important property of the CSDF model is the ability to derive a schedule

for the actors at design-time. In order to derive a valid static schedule for a CSDF graph at design-time, it has to be *consistent* and *live*.

**Theorem 2.1.1** (From [16]). In a CSDF graph G, a repetition vector  $\vec{q} = [q_1, q_2, \cdots, q_{|\mathcal{A}|}]^T$  is given by

$$\vec{q} = \Theta \cdot \vec{r} \quad with \quad \Theta_{ik} = \begin{cases} \phi_i & if \ i = k \\ 0 & otherwise \end{cases}$$

(2.1)

where  $\vec{r} = [r_1, r_2, \cdots, r_{|\mathcal{A}|}]^T$  is a positive integer solution of the balance equation

$$\Gamma \cdot \vec{r} = \vec{0} \tag{2.2}$$

and where the topology matrix  $\Gamma \in \mathbb{Z}^{|\mathcal{E}| \times |\mathcal{A}|}$  is defined by

$$\Gamma_{ui} = \begin{cases} X_i^u(\phi_i) & \text{if actor } A_i \text{ produces on channel } E_u \\ -Y_i^u(\phi_i) & \text{if actor } A_i \text{ consumes from channel } E_u \\ 0 & \text{otherwise.} \end{cases}$$

(2.3)

Theorem 2.1.1 shows that a repetition vector and hence a valid static schedule can only exist if the balance equation, given as Equation (2.2), has a non-trivial solution [16]. A graph *G* that meets this requirement is said to be consistent. An entry  $q_i \in \vec{q} = [q_1, q_2, \cdots, q_{|\mathcal{A}|}]^T \in \mathbb{N}^{|\mathcal{A}|}$  denotes how many times an actor  $A_i \in \mathcal{A}$  executes in every graph iteration of *G*. If a deadlock-free schedule can be found, *G* is said to be live. When every actor  $A_i \in \mathcal{A}$  in *G* has a single phase, i.e.,  $\phi_i = 1$ , the graph *G* is a Synchronous Data Flow (SDF) [52] graph, meaning that the SDF MoC is a subset of the CSDF MoC.

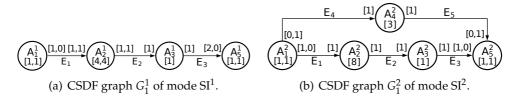

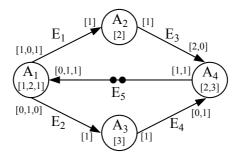

For example, Figure 2.2(b) shows a CSDF graph. The graph has a set  $\mathcal{A} = \{A_1, A_2, A_3, A_4, A_5\}$  of five actors and a set  $\mathcal{E} = \{E_1, E_2, E_3, E_4, E_5\}$  of five FIFO channels that represent the data dependencies between the actors. In this graph, there is one input actor (i.e.,  $A_1$ ) and one output actor (i.e.,  $A_5$ ). Each actor has different number of phases, an execution time sequence, and production/consumption sequences on different channels. For instance, actor  $A_1$  has two phases, i.e.,  $\phi_1 = 2$ , its execution time sequence (in time units) is  $[C_1(1), C_1(2)] = [1, 1]$  and its token production sequence on channel  $E_4$  is [0, 1]. Then, according to Equations (2.1), (2.2), and (2.3) in Theorem 2.1.1, we can derive the repetition vectors  $\vec{q}$  as follows:

$$\mathbf{\Gamma} = \begin{bmatrix} 1 & -1 & 0 & 0 & 0 \\ 0 & 1 & -1 & 0 & 0 \\ 0 & 0 & 1 & 0 & -1 \\ 1 & 0 & 0 & -1 & 0 \\ 0 & 0 & 0 & 1 & -1 \end{bmatrix}, \vec{r} = \begin{bmatrix} 1 \\ 1 \\ 1 \\ 1 \\ 1 \end{bmatrix}, \mathbf{\Theta} = \begin{bmatrix} 2 & 0 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 0 & 0 \\ 0 & 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & 0 & 2 \end{bmatrix}, \text{ and } \vec{q} = \begin{bmatrix} 2 \\ 1 \\ 1 \\ 1 \\ 2 \end{bmatrix}$$

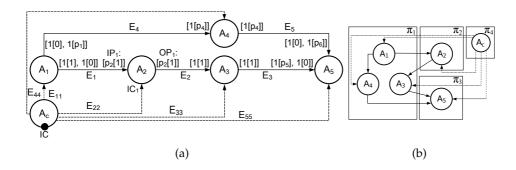

**Figure 2.1:** *Example of an MADF graph*  $(G_1)$ *.*

Figure 2.2: Two modes of the MADF graph in Figure 2.1.

### 2.1.2 Mode-Aware Data Flow (MADF)

MADF [94] is an adaptive MoC which can capture multiple application modes associated with an adaptive streaming application, where each individual mode is represented as a CSDF graph [16]. Formally, an MADF is a multigraph defined by a tuple ( $\mathcal{A}, A_c, \mathcal{E}, P$ ), where  $\mathcal{A}$  is a set of dataflow actors,  $A_c$  is the control actor to determine modes and their transitions,  $\mathcal{E}$  is the set of edges for data/parameter transfer, and  $P = \{\vec{p}_1, \vec{p}_2, \dots, \vec{p}_{|\mathcal{A}|}\}$  is the set of parameter vectors, where each  $\vec{p}_i \in P$  is associated with a dataflow actor  $A_i \in \mathcal{A}$ . The detailed formal definitions of all components of the MADF MoC can be found in [94].

Here, we explain the MADF intuitively by an example. The MADF graph  $G_1$  of an adaptive streaming application with two different modes is shown in Figure 2.1. This graph consists of a set of five actors  $A_1$  to  $A_5$  that communicate data over FIFO channels, i.e., the edges  $E_1$  to  $E_5$ . Also, there is an extra actor  $A_c$  which controls the switching between modes through control FIFO channels, i.e., the edges  $E_{11}$ ,  $E_{22}$ ,  $E_{33}$   $E_{44}$ , and  $E_{55}$ , at run-time. Each data FIFO channel contains a production and a consumption pattern, and some of these production and consumption patterns are parameterized. Having different values of parameters and WCET of the actors determine different

modes. For example, to specify the consumption pattern with variable length on a data FIFO channel in graph  $G_1$ , the parameterized notation [a[b]] is used to represent a sequence of a elements with integer value b, e.g., [2[1]] = [1, 1]and [1[2]] = [2]. For the MADF example in Figure 2.1,  $P = \{\vec{p}_1 = [p_1], \vec{p}_2 = [p_2], \vec{p}_3 = [], \vec{p}_4 = [p_4], \vec{p}_5 = [p_5, p_6]\}$ . Now let assume that the parameter vector  $[p_1, p_2, p_4, p_5, p_6]$  can take only two values [0, 2, 0, 2, 0] and [1, 1, 1, 1, 1]. Then,  $A_c$  can switch the application between two corresponding modes SI<sup>1</sup> and SI<sup>2</sup> by setting the parameter vector to the first value and the second value, respectively, at run-time. Figure 2.2(a) and Figure 2.2(b) show the corresponding CSDF graphs of modes SI<sup>1</sup> and SI<sup>2</sup>.