Parallel and distributed processing in high speed traffic monitoring  $\mathsf{Cristea},\,\mathsf{M.L.}$

### Citation

Cristea, M. L. (2008, October 1). *Parallel and distributed processing in high speed traffic monitoring*. *ASCI dissertation series*. Retrieved from https://hdl.handle.net/1887/13122

Version: Corrected Publisher's Version

License: License agreement concerning inclusion of doctoral thesis in the

Institutional Repository of the University of Leiden

Downloaded from: https://hdl.handle.net/1887/13122

**Note:** To cite this publication please use the final published version (if applicable).

# Parallel and Distributed Processing in High Speed Traffic Monitoring

Mihai-Lucian Cristea

## Parallel and Distributed Processing in High Speed Traffic Monitoring

### **Proefschrift**

ter verkrijging van de graad van Doctor aan de Universiteit Leiden, op gezag van Rector Magnificus prof.mr. P. F. van der Heijden, volgens besluit van het College voor Promoties te verdedigen op woensdag 1 oktober 2008 klokke 15:00 uur

door

Mihai-Lucian Cristea geboren te Galaţi, România in 1976

### Samenstelling promotiecommissie:

promotor: Prof.dr. H.A.G. Wijshoff Universiteit Leiden co-promotor: Dr. H.J. Bos Vrije Universiteit referent: Dr. E.P. Markatos FORTH, Greece

overige leden: Prof.dr. E. DePrettere Universiteit Leiden

Prof.dr. F.J. Peters Universiteit Leiden Prof.dr. J.N. Kok Universiteit Leiden

Dr. C.Th.A.M. de Laat Universiteit van Amsterdam Dr. B.H.H. Juurlink Technische Universiteit Delft

This work was carried out in the ASCI graduate school. ASCI dissertation series number: 164.

Parallel and Distributed Processing in High Speed Traffic Monitoring Mihai-Lucian Cristea.

Thesis Universiteit Leiden. - With ref. - With summary in Dutch ISBN 978-973-1937-03-8

Copyright ©2008 by Mihai-Lucian Cristea, Leiden, The Netherlands.

All rights reserved. No part of the material protected by this copyright notice may be reproduced or utilised in any form or by any means, electronic or mechanical, including photocopying, recording or by any information storage and retrieval system, without permission from the author.

Printed in Romania by ALMA PRINT Galaţi

### Contents

| 1 | Intr | troduction 1 |                                                            |    |  |  |  |  |  |  |

|---|------|--------------|------------------------------------------------------------|----|--|--|--|--|--|--|

|   | 1.1  | Proble       | roblem definition                                          |    |  |  |  |  |  |  |

|   | 1.2  | Appro        | ach                                                        | 3  |  |  |  |  |  |  |

|   | 1.3  | State o      | of the Art in network traffic monitoring                   | 6  |  |  |  |  |  |  |

|   |      | 1.3.1        | Network monitoring applications                            | 6  |  |  |  |  |  |  |

|   |      | 1.3.2        | Specialised hardware for network monitoring                | 9  |  |  |  |  |  |  |

|   |      | 1.3.3        | Storing traffic at high-speeds                             | 11 |  |  |  |  |  |  |

|   | 1.4  | Traffic      | processing at high link rates                              | 12 |  |  |  |  |  |  |

|   | 1.5  |              | hesis overview                                             |    |  |  |  |  |  |  |

| 2 | Bac  | kground      | d                                                          | 15 |  |  |  |  |  |  |

|   | 2.1  | The FI       | FPF framework                                              | 15 |  |  |  |  |  |  |

|   |      | 2.1.1        | The FFPF architecture                                      | 16 |  |  |  |  |  |  |

|   |      | 2.1.2        | The FPL-1 language                                         |    |  |  |  |  |  |  |

|   | 2.2  |              |                                                            |    |  |  |  |  |  |  |

|   |      | 2.2.1        | Common characteristics in NPs                              | 24 |  |  |  |  |  |  |

|   |      | 2.2.2        | The IXP1200 processor                                      | 25 |  |  |  |  |  |  |

|   |      | 2.2.3        | The IXP2400 processor                                      |    |  |  |  |  |  |  |

|   |      | 2.2.4        | The IXP2850 processor                                      |    |  |  |  |  |  |  |

| 3 | A R  | esource      | Constrained Language for Packet Processing: FPL            | 31 |  |  |  |  |  |  |

|   | 3.1  |              | FPF packet language: FPL                                   | 31 |  |  |  |  |  |  |

|   |      | 3.1.1        | From interpreted to compiled code                          |    |  |  |  |  |  |  |

|   |      | 3.1.2        | The FPL language                                           |    |  |  |  |  |  |  |

|   |      | 3.1.3        | The FPL-compiler architecture                              |    |  |  |  |  |  |  |

|   |      | 3.1.4        | The FPL-compiler tool                                      |    |  |  |  |  |  |  |

|   |      | 3.1.5        | Authorisation of FPL filters into the run-time environment | 47 |  |  |  |  |  |  |

|   | 3.2  | Evalua       | ation of the FPL-compiler                                  |    |  |  |  |  |  |  |

|   | 3.3  |              | oles of FPL applications                                   |    |  |  |  |  |  |  |

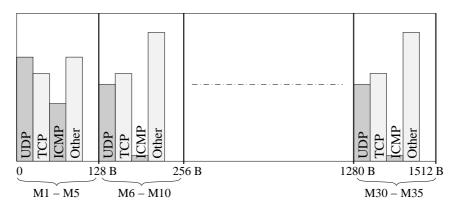

|   |      | 3.3.1        | Traffic characteristics histogram                          |    |  |  |  |  |  |  |

|   |      | 332          |                                                            | 51 |  |  |  |  |  |  |

viii Contents

|   | 3.4  | Summary                                                    | 53       |

|---|------|------------------------------------------------------------|----------|

| 4 | FPI. | Run-time Environments                                      | 55       |

| - | 4.1  |                                                            | 55       |

|   | 7.1  | •                                                          | 55<br>55 |

|   |      | $\epsilon$                                                 | 55<br>57 |

|   |      | 1 3                                                        | 57<br>58 |

|   | 4.2  | 1                                                          | ٥٥<br>59 |

|   | 4.2  |                                                            |          |

|   |      |                                                            | 60       |

|   |      |                                                            | 62       |

|   |      |                                                            | 64       |

|   |      |                                                            | 64       |

|   |      |                                                            | 65       |

|   | 4.3  |                                                            | 65       |

|   |      | E                                                          | 67       |

|   |      | 8 8                                                        | 67       |

|   |      | 4.3.3 Using system level synthesis tool                    | 69       |

|   | 4.4  | Evaluation                                                 | 70       |

|   |      | 4.4.1 FFPF on commodity PC                                 | 70       |

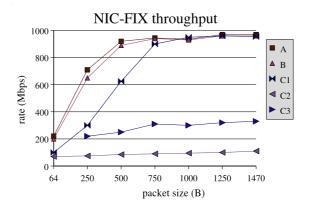

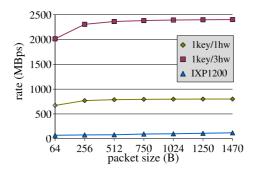

|   |      | 4.4.2 FFPF on NP: NIC-FIX                                  | 71       |

|   |      | 4.4.3 FFPF on FPGA: NIC-FLEX                               | 73       |

|   | 4.5  | Summary                                                    | 77       |

| 5 | Dist | ibuted Packet Processing in Multi-node NET-FFPF            | 79       |

|   | 5.1  | Introduction                                               | 79       |

|   | 5.2  | Architecture                                               | 80       |

|   |      | 5.2.1 High-level overview                                  | 80       |

|   |      | <u> </u>                                                   | 81       |

|   |      | · · · · · · · · · · · · · · · · · · ·                      | 82       |

|   | 5.3  |                                                            | 84       |

|   | 5.4  | ±                                                          | 89       |

|   | 5.5  |                                                            | 91       |

| 6 | Tow  | ards Control for Distributed Traffic Processing: Conductor | 93       |

| • |      | 6                                                          | 93       |

|   | 6.2  |                                                            | 96       |

|   | 0.2  |                                                            | 96       |

|   |      |                                                            | 98       |

|   |      |                                                            | 00       |

|   |      | 1 6                                                        | 00<br>01 |

|   |      | 6.2.5 Resource screening                                   |          |

|   |      | 6.2.6 Resource control topologies                          |          |

|   | 6.3  | ·                                                          | 03<br>03 |

|   | U. 7 | Authority                                                  | 7        |

Contents ix

| 7   | A Si   | mple Implementation of Conductor Based on Centralised Control         | 105 |

|-----|--------|-----------------------------------------------------------------------|-----|

| ,   | 7.1    | Centralised control for adaptive processing                           |     |

|     | ,      | 7.1.1 Model identification in a distributed traffic processing system |     |

|     |        | 7.1.2 Control design                                                  |     |

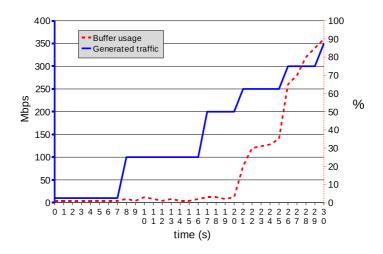

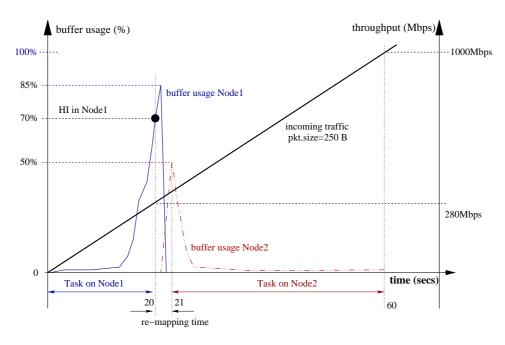

|     | 7.2    | Experiments                                                           |     |

|     | 7.2    | 7.2.1 Test-bench                                                      |     |

|     |        | 7.2.2 Application task: pattern matching                              |     |

|     |        | 7.2.3 Controller behaviour                                            |     |

|     | 7.3    | Summary                                                               |     |

| 8   | Revo   | ond Monitoring: the Token Based Switch                                | 119 |

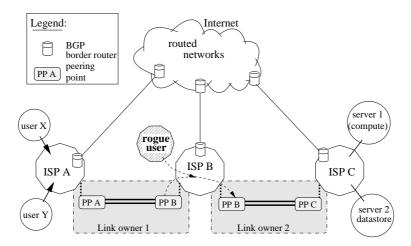

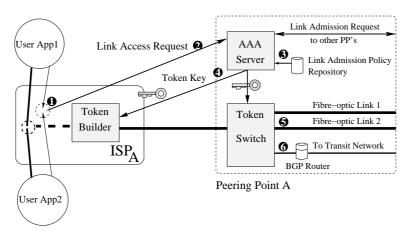

| Ü   | 8.1    | Introduction                                                          |     |

|     | 8.2    | Architecture                                                          |     |

|     | 0.2    | 8.2.1 High-level overview                                             |     |

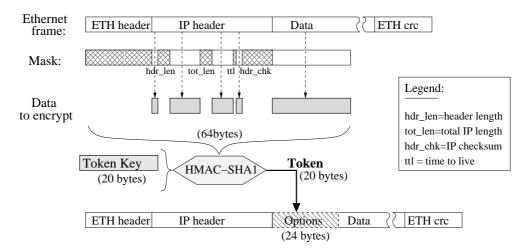

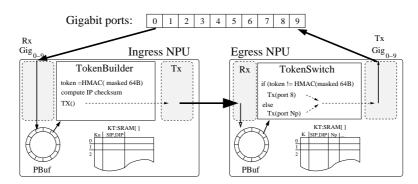

|     |        | 8.2.2 Token principles                                                |     |

|     | 8.3    | Implementation details                                                |     |

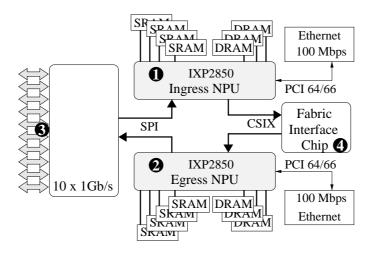

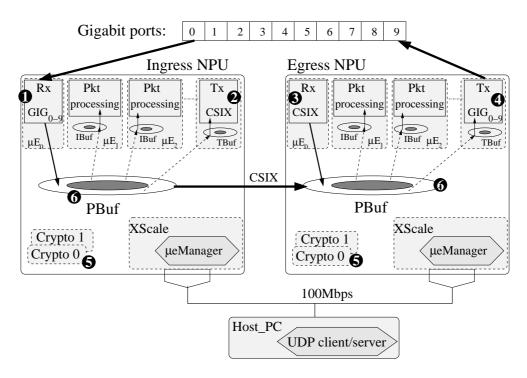

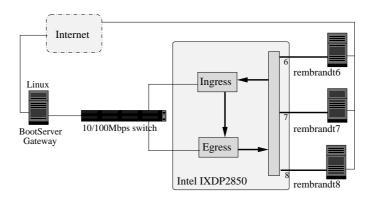

|     | 0.0    | 8.3.1 Hardware platform                                               |     |

|     |        | 8.3.2 Software framework; FFPF on IXP2850                             |     |

|     |        | 8.3.3 Token Based Switch                                              |     |

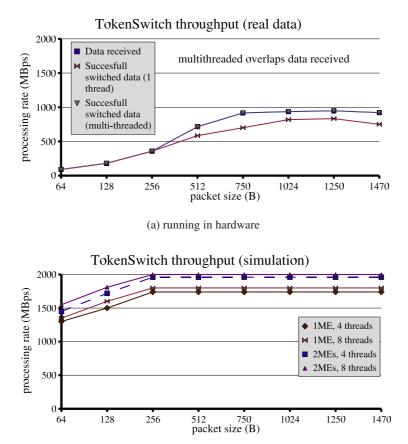

|     | 8.4    | Evaluation                                                            |     |

|     | 8.5    | Discussion                                                            |     |

|     | 0.0    | 8.5.1 Summary                                                         |     |

| 9   | Con    | clusions                                                              | 137 |

|     | 9.1    | Summary of contributions                                              | 138 |

|     | 9.2    | Further research                                                      |     |

| Bil | bliogi | raphy                                                                 | 140 |

| Sa  | menv   | atting                                                                | 151 |

| Ac  | know   | vledgments                                                            | 155 |

|     |        | ılum Vitae                                                            | 157 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <b>-</b> |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--|--|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |  |  |  |

| \( \text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\tinc{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\tin}\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\texi}\text{\text{\text{\text{\text{\text{\text{\text{\tet |          |  |  |  |

| Chapter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |  |  |  |

How could anybody imagine in the late 1960s, when the Internet was born on those 50 Kbps wires of the ARPANET, that nowadays, less than five decades later, we are using connection speeds of multiple Gbps over millions of nodes. Although the Internet development started as a military project, ARPANET, it went to public domain and is currently supported worldwide from people's need to share and exchange their knowledge. Currently, there is a huge amount of information available on the Internet that no one man can assimilate by himself in a lifetime. Extrapolating from these facts, can anybody imagine how fast our machines will communicate in the next few decades? What kind of material or immaterial support will be used by that time for information exchange? How will the 'network of networks' (the Internet) manage/control itself?

Since the Internet was born on the first packet-switched data networks, there has been a need for traffic processing at the nodes of this network (e.g., for routing). Currently, however, the need arises for increasingly complex processing at these nodes. For instance, increasing concerns about security demand efficient scanning of payloads and other needs such as network monitoring. Unfortunately, it seems that the network speed increases at least as fast as the processing capacity and probably faster [1]. It has often been suggested that parallelism is the only way to handle future link rates [2–4]. In this thesis, the assumption is that link rates grow so fast as to exceed the capacity of a single processor. The question we try to address is how to handle the link rate of the future. To limit the scope of this research to a manageable problem domain, we restrict ourselves primarily to network monitoring applications (although we also consider other domains).

This chapter briefly summarises the research questions and the approach towards a solution in the first two sections, followed by the current state-of-the-art in traffic monitoring which will be described in Section 1.3. The thesis statement and argumentation are presented in Section 1.4. And finally, an overview of the main results is shown in Section 1.5.

### 1.1 Problem definition

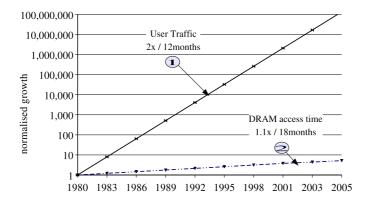

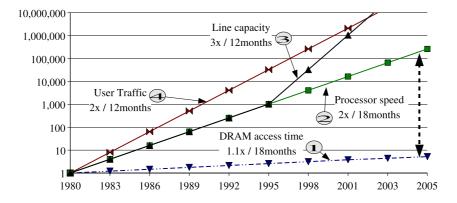

In recent years there has been a growing gap between the link speeds and the processing and storage capacity for user traffic that flows through the Internet links. On the one hand, the link speed improvements are given mostly by the advances in optical fields. On the other hand, the evolution of processing capacity is much slower than that of link speeds because it is limited by the (slow) evolution of memory access time technology. Using fast memory like SRAM instead of DRAM to cope with the memory bottleneck is a feasible solution for many applications in the computer industry where caching can be aggressively exploited because the applications exhibit a lot of locality of reference. Unfortunately, most networking applications offer very little locality of reference, so the benefit of caching are small. Figure 1.1 illustrates in logarithmic scale, as observed by McKeown [5], a normalised growth of the trends of aggregated user traffic that passes the routers of a typical backbone in the Internet ① versus DRAM memory access time ②.

Figure 1.1: Trends in technology and traffic.

The memory bottleneck pushes us towards using parallel and distributed systems. Modern networking equipment often uses distributed systems made of tightly coupled parallel systems: multi-core. However, when using multi-cores hardware systems we need to design and develop networking applications that map onto the parallel system. Moreover, when using different hardware systems for various traffic processing tasks (e.g., a commodity PC for traffic shaping or audio/video streams processing specialised hardware) we need to address a heterogeneous distributed processing system. How can we build such a heterogeneous distributed system for traffic processing?

In addition to the distributed demands, traffic processing systems also face the problem of changing conditions. For instance, a traffic processing application may be designed and developed for certain traffic assumptions. However, one day, the traffic exceeds the assumptions made at design time (e.g., increase in service users, introduction of a new popular service, or malicious traffic). Therefore, a second demand is to build a 'distributed traffic processing system' that can autonomously adapt to an unforeseen and changing environment. For this purpose, we need to address the following research questions:

• initial system state (at deployment time): how to compute a proper mapping of the

1.2 Approach 3

system requirements onto a given distributed hardware architecture composed of heterogeneous nodes;

• continuous adaptive system (at runtime): how to adjust the distributed processing system (e.g., by traffic re-routing or tasks re-mapping) according to the environment changes so that the entire system remains stable and works at an optimal level.

### 1.2 Approach

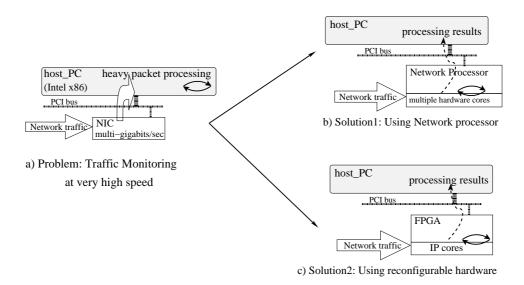

In these days, there is an increasingly demand for traffic monitoring at backbone speeds. Most of the advanced traffic monitoring systems such as network intrusion detection systems (NIDS) need to process all incoming packets by touching the entire packet byte stream in order to scan for virus signatures, for instance. Moreover, other traffic monitoring systems such as network intrusion prevention systems (NIPS) need, in addition to the NIDS, to perform on each packet intensive computations like checksums, packet fragmentation for transmission, encryption/decryption, etc.

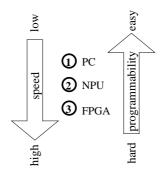

Current, programmable traffic processing systems build on one (or both) of the following available hardware processing architectures: a general purpose CPU such as Intel Pentium 4, or specifically designed embedded systems for packet processing such as Intel IXP2xxx network processors. Both architectures present the same major barrier that stands against providing the processing power required by the traffic monitoring applications: the memory bottleneck. The processing technology is trying hard to cope with the memory bottleneck by using parallel threads or cores and multiple memory buses so as to hide the memory latency.

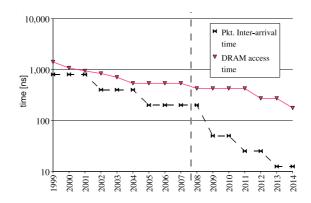

Assuming an average Internet packet size of 250Bytes, Figure 1.2 illustrates the packet inter-arrival time for current and future link speeds. In other words, a traffic processing system has to receive, process, and eventually transmit every incoming packet within a certain time determined by the packet inter-arrival time so as to keep up with the link speed in use. When the time that the processing system spends on each packet exceeds this packet inter-arrival time, then the system starts dropping packets because a new packet arrives before the system finished with the current one.

Figure 1.2: Link versus memory access speeds.

The packet inter-arrival time chart shown in Figure 1.2 decreases exponentially with the use of higher link speeds in time. Although the latest official link speed is not in use currently, the first optical transceiver working at OC-3072 (cca. 160 Gbps) speed was already announced by IBM on 29 March 2007. Figure 1.2 also illustrates the memory access time needed to write and read a chunk of 250 data bytes in an external DRAM memory at different moments in time, as the memory technology evolved and is predicted to evolve by Inphi Corporation [6]. However, when comparing the evolution of the packet inter-arrival time against those of the memory access time, we can see that there is a growing disparity. Moreover, this disparity does not include the time a general CPU architecture would need to transfer the data across other buses such as the PCI express.

'Parallelism' is a well known concept that helps to build architectures that cope with the disparity risen because of a bottleneck in the data process flow. Since the end of the 90s, network processor architectures specialised in packet processing were built on a 'tightly coupled' parallelism concept: multiple cores on the same silicon. The external shared memory (DRAM) was connected to the multi-core architecture through parallel buses so as to hide the memory latency as much as possible. However, as shown in Figure 1.2, after a certain link speed the disparity becomes so large that even a single parallel processing system is not sufficient and we will show how we can cope with higher speeds by distributing the workload onto a distributed architecture.

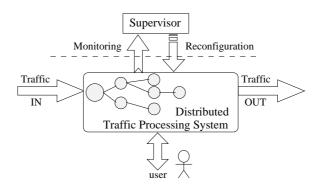

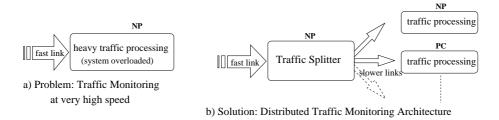

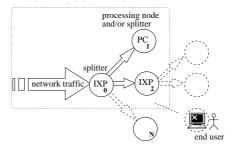

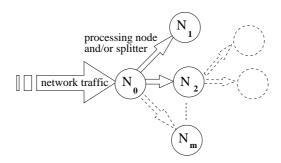

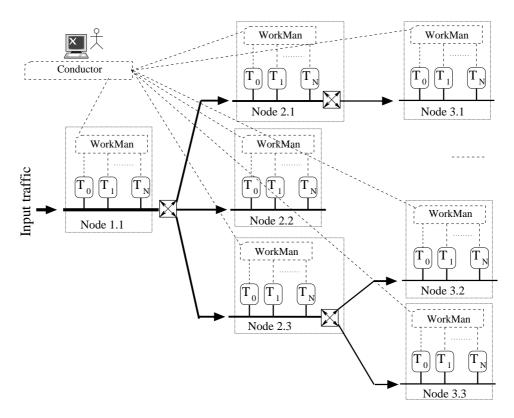

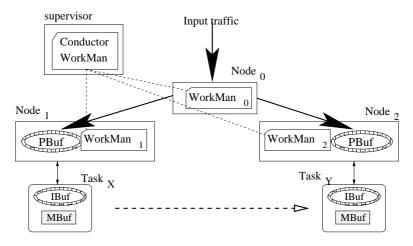

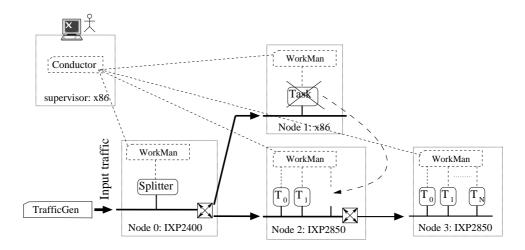

In our context of traffic processing, such a system works as follows: First, there is a *traffic splitter* that splits the input traffic in substreams and distributes them on a hierarchy of possible heterogeneous *processing nodes*. Next, each processing node performs, in parallel, specific traffic processing tasks over its received stream. In the end, the processed packets can be modified and sent out, dropped, or forwarded out as they came in. These actions belong to the packet processing tasks deployed by a user on the entire distributed system. In addition to the processing actions, a supervisor host can collect some of the processing results (e.g., packet counters, virus occurrence numbers) from all processing nodes. These results are then available for further investigation by the user (e.g., a system administrator).

Although the idea of a distributed network monitor was first advocated by Kruegel et al. in May 2002 [7], it was used only in the context of a distributed intrusion detection system development using one traffic splitter and several other hosts for distributed processing. Another usage of the traffic splitting idea was introduced by Charitakis et al. in [8] also in a NIDS. Although their implementation used a heterogeneous architecture (a network processor card plugged in a commodity PC), the splitter was used to separate the traffic processing of an NIDS into two steps: 'early filtering' and 'heavy processing'. The first step was designed to process a few bytes (e.g., packet header fields) so as to slice and load balance the traffic onto a distributed NIDS sensors. While the 'early filtering' step was implemented on a network processor card, the 'heavy processing' step was implemented in several commodity PCs using the Snort NIDS software. Our approach uses the splitter idea in a generalised context of a fully distributed processing system composed of processing nodes that form a processing hierarchy where nodes near the root perform traffic splitting and processing together, and the nodes near the leaves perform only 'heavy processing' tasks. Our architecture is fully programmable by the way the traffic is split/routed across the distributed nodes and is designed to support various traffic processing applications and aims to cope with speed, scalability, and heterogeneous demands.

1.2 Approach 5

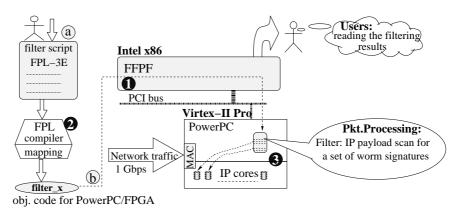

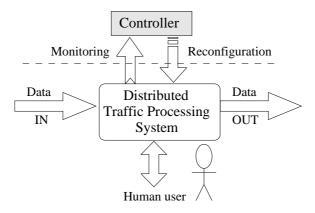

The approach proposed in this thesis is illustrated in Figure 1.3 and consists mainly of a distributed traffic processing system that *processes* the input traffic, sends out some of the processed traffic, and *interacts* with a user. In addition, the illustrated architecture provides autonomy and self-adaptive properties by using a 'supervisor' component that *monitors* the system and environment states and *re-configures* the system so the entire architecture remains stable regardless of the environment changes (e.g., increase in traffic input, hardware failure).

Figure 1.3: Self-adaptive architecture for traffic processing.

We have chosen to use a distributed system for the purpose of traffic processing for the following reasons. First, there is an increasing demand for intensive traffic processing applications such as the Network Intrusion Detection Systems (NIDS) and the Network Intrusion Prevention Systems (NIPS). Second, running the traffic processing applications at backbone line rate (10 Gbps and more) is a challenge in itself. Third, special hardware systems called network processors (NPs) provide hardware parallelism (using multi-cores) to cope with high bandwidth from a backbone line, but programming them is difficult and the performance is still insufficient. For instance, even a basic NIDS implementation on a network processor (as Bos et al. show in [9]) cannot perform more than 1 Gbps. Fourth, the life cycle of the special purpose hardware for traffic processing (e.g., network processors) gets shorter and shorter. Moreover, these hardware systems are expensive and a customer often has multiple hardware system generations in use. We see an increasing demand for using heterogeneous hardware for processing nodes in a distributed system. Fifth, various traffic processing applications make use of hardware designed for a specific purpose: network processors for generic traffic processing such as routing, monitoring, limited payload scanning; custom FPGA designs for specific processing tasks such as processing video streams; etc. Using a distributed system is a solution for unifying every specific traffic processing node. Concluding, a distributed system offers the following benefits: (1) heterogeneity (using a federated architecture composed of various hardware processing system such as commodity PCs, network processors); (2) scalability (practical because there is no limitation for the size of the system). At the same time, a distributed approach comes at a price: the increased complexity of the system.

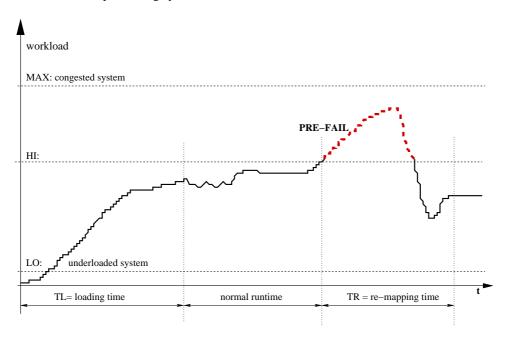

The traffic processing system in which we are interested is designed to work at the network edge of enterprise gateways. Once the system is deployed by an administrator, we expect it to work non-stop. However, it is well known that there are always peaks in the network traffic (e.g., rush hours or malicious traffic). Therefore, in addition to the distributed

property we also propose to use an automatic control system (the 'supervisor' in Figure 1.3) that provides (3) a high availability property, meaning robustness to congestions for unexpected environment changes.

### 1.3 State of the Art in network traffic monitoring

In the following subsections we describe the state-of-the-art problems in traffic monitoring and the current related technologies.

### 1.3.1 Network monitoring applications

The explosion of network based applications increases the complexity of the traffic by means of more and more protocols and their relationships to be analysed by any system administrator in case of network problems. Every network user produces and consumes traffic data through the applications he/she uses. For example, in the early days of Internet, most of the traffic seen at a corporate gateway was produced by e-mail client/server applications and could be monitored easily by a commodity PC over a 10/100 Mbps connection. At the present time, the peer-to-peer and web-service applications have risen the traffic bandwidth to such a level that soon no piece of hardware could monitor, alone, the entire traffic that passes a corporate backbone. Moreover, there are specific demands for handling high speed traffic (multi Gbps) in various research fields such as super computing, grid computing, etc. For instance, a scientist needs to access, remotely, the results of certain physics experiments from his office across the ocean. This action requests huge amount of data over a (physically) long connection that bypasses the regular Internet and uses specially demanded fibre optic links. In order to provide such links on-demand dynamically, we need to monitor the traffic at these high speeds so as to prevent un-authorised traffic using the requested links.

For a convenient description of the network tools, we classify them in two categories: high-level and low-level. The latter are run-time libraries and tools for packet processing at the lowest level (OS kernel or specialised hardware) on top of which the former are built: network monitoring applications.

### **High-level: applications**

Although there are monitoring applications that need to analyse the full backbone traffic such as network intrusion detection or prevention systems, there are also monitoring applications that are interested in only part of the traffic. Such tools that monitor only part of the traffic are: network debugging that answer to questions like 'what is the performance between two clients?', traffic accounting tools that identify 'what traffic is p2p', etc.

Traffic monitoring applications can diagnose network problems by protocol analysis. For instance, a performance analysis of real-time streams between two nodes may take into account the following parameters:

• total delay: it is given by the network latency and usually is a stable value for any connection;

- bandwidth consumption: it may be shown by the average, or maximum value or, the peak burst value of the moving average bit rate;

- *jitter*: distribution of packet inter-arrival time determines how many packets are delayed beyond the jitter buffer;

- packet loss: determine the effect on quality due to packet loss for real-time streams.

Traffic monitoring provides critical information for internet service providers (ISPs) looking to optimise network speed, content delivery and performance of subscribed services on the network. Advanced reporting also helps ISPs categorise unidentified traffic for increased security from unidentified P2P traffic, for instance.

In the end, we see an increasing demand for a monitoring system that supports multiple monitoring applications processing together the incoming traffic within the same hardware due to speed demands and cost reasons.

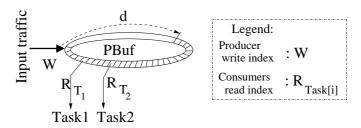

For example, multiple monitoring applications (e.g., snort [10], topdump [11], ntop [12], CoralReef [13]) access identical or overlapping sets of packets. Therefore, we need techniques to avoid copying a packet from the network device to each application that needs it. For instance, the FFPF tool [14] provides different 'copy' semantics so as to minimise the packet copying. The most common mechanism is using shared buffers. As an example, the FFPF implementation uses a large shared packet buffer (where all received packets are stored) and one small index buffer for each application. Applications use the local indexes to find the interesting packets in the shared buffer. One of the copy semantic features available in FFPF is called 'copy-once'. In other words, the system copies only once the received packet from NIC to the host's shared memory. Usually this copy is transparently performed by the network card itself through DMA channels. Another copy semantic provided by FFPF is 'zero-copy'. In zero-copy, every incoming packet is stored in a large shared buffer within the network card and the packet index is provided to each monitoring application running locally in the card or remotely in the host. Then the application uses this packet index to point to the main packet data from the card's buffer and checks the fields it is interested in. There is a trade-off between the usage of zero-copy or copy-once, depending on the application demands and on the available hardware support. For instance, when we have monitoring applications that are interested in processing the entire stream of incoming packets (e.g., NIDS) it is feasible to use copy-once. However, using zero-copy may be better when the most processing takes place on the card and only statistics are sent to the host, or when the host accesses packets irregularly and only for checking a few bytes of the packet (e.g., various protocol performance analysers).

One of the most intensive traffic processing applications is network intrusion detection/prevention systems because they usually process the full traffic (entire packet payload). In Information Security, intrusion detection is "the act of detecting actions that attempt to compromise the confidentiality, integrity or availability of a resource" [15]. Intrusion detection does not, in general, include prevention of intrusions. In other words, a network intrusion detection system (NIDS) detects computer systems threats by means of malicious usage of the network traffic. A NIDS works by identifying patterns of traffic presumed to be malicious that cannot be detected by conventional firewalls such as network attacks against vulnerable services, data driven attacks on applications, etc. A network intrusion prevention system (NIPS) works differently from IDS in the sense that it analysis each packet for malicious

content before forwarding it and drops packets sent by an intruder. To do so, the IPS has to be physically integrated into the network and needs to process the actual packets that run through it, instead of processing copies of the packets at some place outside the network. Therefore, independent of the way they are built, all IPSes introduce the same problem: a decrease in performance (e.g., inter-packet delay) of the network they try to protect.

A lightweight network intrusion detection system is Snort [10]. Snort is the most widely deployed intrusion detection and prevention technology worldwide and has become the de facto standard for the industry. Snort is an open-source software capable of performing real-time traffic analysis and packet logging on IP networks. It can perform protocol analysis, content searching/matching and can be used to detect a variety of attacks and probes, such as buffer overflows, stealth port scans, CGI attacks, OS fingerprinting attempts, and much more. Snort uses a flexible rules language to describe traffic that it should collect or pass, as well as a detection engine that uses a modular plugin architecture. Snort has a real-time alerting capability as well as alerting mechanisms for syslog, or a user specified file. However, Snort copes fairly well with low speed links, but it cannot handle multi-gigabit link rates.

Other intensive traffic processing applications such as *transcoders* are currently adjusting the encoded video streams (e.g., JPEG-2000, MPEG-4) to the unreliable transmission medium which uses fast and low transmission-delay protocols such as UDP. On the one hand, the encoded video streams are sensitive to the arrival order of consequent packets which compose video frames. On the other hand, a best effort protocol such as UDP does not offer any guarantee of the packet arrival correctness. Therefore, the encoded multimedia stream needs to be 'transcoded' into a more appropriate format stream for the transmission capabilities. For example, a transcoding from the layered representation in which any frame loss brings a huge quality drop (e.g., video de-synchronisation) to multiple distinct descriptions of the source which can be synergistically combined at the other end would enhance the quality [16]. Transcoding may also use algorithms such as Forward Error Correction (FEC) which requires intensive computation in real-time and thus, we see the need for parallel and distributed architectures in order to provide the required processing power for the current and the future encoded media streams.

Other intensive traffic processing applications are those that require encryption computation. For example, network oriented applications which require specific networks such as direct end-to-end fibre interconnection (e.g., grid computation, corporate database transfers) need to provision a safe authentication for the dynamically demanded fibres. Therefore, encryption per-packet is sometimes used to provide the end-to-end paths over multiple network domains where different policy applies [17]. Again, parallel and distributed architectures help to bring the required traffic processing power.

#### Low-level: run-time libraries

Most of the high-level applications are built on top of a few, common, low-level libraries or tools. In this section, we briefly describe the evolution of the packet filtering tools and their techniques.

The Berkeley Packet Filter (BPF) [18] was one of the first generation of packet filtering mechanism. BPF used a virtual machine built on a register-based assembly language and a directed control flow graph. However, BPF lacks in an efficient filter composition technique because the time required to filter packets grows linearly with the number of con-

catenated filters and hence, BPF does not scale well with the number of active consumers. MPF [19] enhances the BPF virtual machine with new instructions for demultiplexing to multiple applications and merges filters that have the same prefix. This approach is generalised by PathFinder [20] which represents different filters as predicates of which common prefixes are removed. PathFinder is interesting in that it is well suited for hardware implementation. DPF [21] extends the PathFinder model by introducing dynamic code generation. BPF+ [22] shows how an intermediate static single assignment representation of BPF can be optimised, and how just-in-time-compilation can be used to produce efficient native filtering code. Like DPF, the Windmill protocol filters [23] also targets high performance by compiling filters in native code. And like MPF, Windmill explicitly supports multiple applications with overlapping filters. All of these approaches target filter optimisation especially in the presence of many filters. Nprobe [24] aims at monitoring multiple protocols and is therefore, like Windmill, geared towards applying protocol stacks. Also, Nprobe focuses on disk bandwidth limitations and for this reason captures as few bytes of the packets as possible. In contrast, FFPF [14] has no a priori notion of protocol stacks and supports full packet processing.

The current packet filtering generation, so called packet classification, uses advanced searching algorithms for rules matching. Packet classification is currently used in many traffic processing tools such as traffic monitoring, routers, firewalls, etc. While in the early days of packet filtering, tools like iptables used a matching algorithm which traverses the rules in a chain linearly per packet. However, nowadays, when many rules have to be checked, a linear algorithm is not suitable anymore. There are many solutions that may use, for instance, geometric algorithms, heuristic algorithms, or specific hardware accelerated searching algorithms. For instance, nf-HiPAC [25] offers a packet classification framework compatible with the known iptables. An ongoing research effort in a packet classification using regular expressions is described in [26, 27].

We note that the most popular high-level tools in use currently (e.g., tcpdump, ntop, snort) are built on top of the pcap library (libpcap) [28]. libpcap provides a cross-platform framework for low-level network monitoring. We notice that libpcap uses a packet filtering mechanism based on the BSD packet filter (BPF).

### 1.3.2 Specialised hardware for network monitoring

The current demands of monitoring high speed network links such as backbone links and the increasing speed of those links beyond the processing capabilities of nowadays' commodity PCs opened the market for specialised architectures for traffic processing. Such architectures uses specialised hardware systems that accelerate specific packet processing functions (e.g., hashing, encryption, searching algorithms) similarly to the graphic accelerators in the 1990s. Currently, the available hardware technology for traffic processing, namely network processors, make use of parallelism to cope with the increasing gap between the link and the memory access speeds.

Filtering and processing in network cards was initially promoted by some Juniper routers [29] and the Scout project [30]. In programming Intel IXP network processors (IXPs), the most notable projects are NPClick [31] and netbind [32]. Although NPClick and netbind introduce interesting programming models, they were not designed for monitoring.

Although the network processors are the current state-of-the-art of specialised technology

for traffic processing, they are surpassed by FPGA technology for specific intensive computation such as custom encryption algorithms, or other mathematically based encoders/decoders. FPGAs are fully programmable chips and suitable for experimental software development in the hardware until an ASIC chip may be deployed.

SpeedRouter [33] is one of the first FPGA-based network processor, but as such, it may require more user programming than most of the network processors (NPs). While the device provides basic packet-forwarding functions, it is up to the user to program functions such as key extraction and packet modification. SpeedRouter was designed for a cut-through data path, as opposed to the store-and-forward nature of most pipelined architectures met in NPs.

DAG cards [34] are another example of NICs based on FPGA technology. They are designed especially for traffic capture at full link rate. DAG cards make use of FPGA parallelism to be able to process the incoming traffic at high speeds, they offer accurate time-stamp using GPS signals (7.5ns resolution), and transfer the full traffic directly to the host PC's memory for a further processing/storing.

The value seen in FPGA prototyping for emulating ASIC designs is recognised across a growing spectrum of design applications. For instance, Shunt [35] is an FPGA-based prototype for an Intrusion Prevention System (IPS) accelerator. The Shunt maintains several large state tables indexed by packet header fields, including IP/TCP flags, source and destination IP addresses, and connection tuples. The tables yield decision values that the element makes on a packet-by-packet basis: forward the packet, drop it, or divert it through the IPS. By manipulating table entries, the IPS can specify the traffic it wishes to examine, directly block malicious traffic, and 'cutting through' traffic streams once it has had an opportunity to 'vet' them, all on a fine-grained basis.

Using reconfigurable hardware for increased packet processing efficiency was previously explored in [36] and [37]. Our architecture differs in that it provides explicit language support for this purpose. As shown in [38], it is efficient to use a source-to-source compiler from a generic language (Snort Intrusion Detection System) to a back-end language supported by the targeted hardware compiler (e.g., Intel  $\mu$ EngineC, PowerPC C, VHDL). We propose a more flexible and easy to use language as front-end for users. Moreover, our FPL language is designed and implemented for heterogeneous targets in a multi-level system.

### Offloading the traffic handling down to the NIC

The current hardware technology contributes to improve the way the traffic is processed in a commodity PC by offloading intensive computations from general purpose CPU down to the NIC card. For instance, looking at the workload that a general purpose CPU spends on processing the network traffic in any user PC connected to a network, it is known that the TCP protocol requires the most CPU time spent on traffic handling before the data arrives at the application. Hence, the first 'protocol accelerators' arrived on the market are: TCP Offload Engine (TOE) and TCP segmentation offloading (TSO).

TCP Offload Engine (TOE) is the name for moving part or all of the TCP/IP protocol processing down to a specialised NIC. In other words, by moving of the TCP/IP processing to a separate dedicated controller off the main host CPU, the overall system TCP/IP performance can be improved. Currently, the developer community is reluctant to adopt TOE, as we will see shortly.

In addition to the protocol overhead that TOE addresses (e.g., sliding window calculations

for packet acknowledgment and congestion control, checksum and sequence number calculations), it can also address some architectural issues that affect many host based endpoints. For example, a TOE solution, located on the network interface, is placed on the other side of the (slow) PCI bus from the CPU host so it can address some I/O efficiency issues. Thus the data needed to cross the TCP connection can be sent to the TOE from the CPU across the PCI bus using large data burst sizes with none of the smaller TCP packets having to traverse the PCI bus.

On the other hand, there are several reasons to consider the full network stack offload (TOE) of little use, as also observed by J. Mogul [39] and summarised as follows:

- Security updates: A TOE network stack is proprietary source firmware. System administrators have no way to fix security issues that arise;

- Hardware-specific limits: TOE NICs are more resource limited than the overall computer systems. This is most readily apparent under load factors which arise when trying to support thousands of simultaneous connections. TOE NICs often simply do not have the memory resources to buffer thousands of connections;

- Dependency on vendor-specific tools: In order to configure a TOE NIC, hardware-specific tools are usually required. This dramatically increases support costs.

The TCP segmentation offloading (TSO) features can improve performance by offloading some TCP segmentation work to the adapter and cutting back slightly on bus bandwidth. For instance, when large chunks of data are to be sent over a computer network, they need to be first broken down into smaller segments that can pass through all the network elements like routers and switches between the source and destination computers. This process is referred to as segmentation. Segmentation is often done by the TCP protocol in the host computer. Offloading this work to the network card is called TCP segmentation offload (TSO).

However, despite its benefits, TSO has also several drawbacks. One drawback is that once a TSO capability was developed to work in an OS vendor's software, the NIC hardware and driver modifications that allow offloading will not work with other OSes. A second drawback is that the offload capability is one-way (transmit) only. A third drawback is that the host cannot offload a data block larger than the remote endpoint's receive window size.

### 1.3.3 Storing traffic at high-speeds

Traffic monitoring by means of traffic capture requires also storing functionality. The received traffic from a network tap needs to be transferred to disks for a further detailed analysis. Support for high-speed traffic capture is provided by OCxMon [40]. Like the work conducted at Sprint [41], OCxMon supports DAG cards to cater to multi-gigabit speeds [34]. Besides using a host PC for traffic capture from a high speed link onto a storage disk, another research area is to use custom FPGA designs as a glue between fibre optic for traffic input and fast serial data lines (e.g., SATA) for output to storage disks. Such systems are currently in use by Storage Area Network (SANs) systems [42].

### 1.4 Traffic processing at high link rates

In this section we present the speed problems that arises when more and more tools want to process packets at higher and higher speeds as shown in the previous sections.

Figure 1.4 shows, in logarithmic scale, the trends in the technologies related to networking as found by McKeown [5]. We see the smallest technology improvement in the DRAM memory access time (chart ①). We can also see that according to Moore's Law, processor complexity (and hence the performance) is constantly growing at mostly the same rate as the line capacity until year 1995 (chart ②). By that time, the optical revolution in wave division multiplexing (DWDM) came together with another prophecy: Gilder's law [1]. George Gilder predicted that "network bandwidth would triple every year for the next 25 years" (chart ③). The most rising chart, user traffic (chart ④), is constantly growing since the early days of the Internet, and sustained by the web innovation in beginning of 1990s, by doubling each year.

Figure 1.4: Trends in technology, routers and traffic.

Considering the disparity between memory access time (chart ①) and processors speed (chart ②), we can say that accessing memory becomes twice as expensive every 18 months [5]. In this context, a generic CPU uses bigger caches and better pre-fetching algorithms, and networking uses more processing cores in order to hide the memory latency because networking cannot offer the locality of reference of the processed data on which a caching technology needs to work.

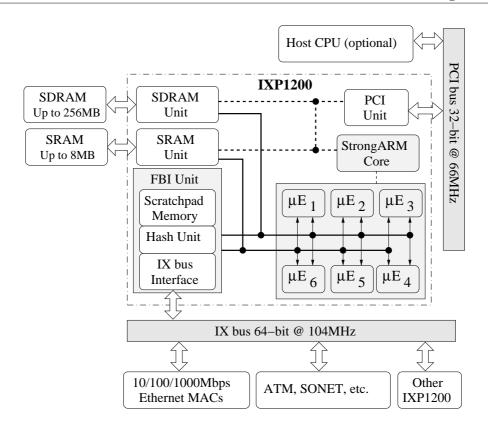

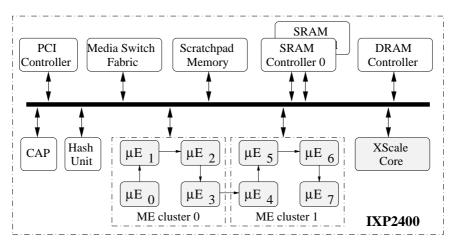

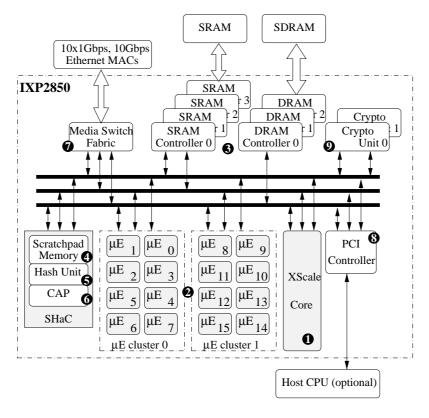

For example, as mentioned earlier, the networking industry may use specifically designed processors called network processors (NPs). NPs use a highly parallelised internal architecture (typically more than 8 cores), several memory types (e.g., SRAM, DRAM) organised in multiple banks and interconnected through parallel buses. NPs use multiple cores specialised in packet processing in order to offer flexibility (they support many applications and deal with protocol and standards changes), and reduce risks (bugs are easier to fix in software than in hardware). NPs try hard to hide memory latency by means of asynchronous memory access because conventional caching is not suitable for networking applications (no temporal or spatial locality, cache misses decrease throughput).

Summarising, the bottleneck moved from processor clock speeds down to the memory latency. In this context, the most important issues in packet processing are the answers to

1.5 Thesis overview 13

'how the packets come in and get out of a chip and memory'; computation becomes a side issue.

The current technologies provide scalability in traffic processing by means of tightly-coupled parallelism (multi-core). Although there are powerful packet processing systems (e.g., network processors) that perform traffic processing applications at high-speed links in use now, we believe that application demands increase beyond the processing ability of only one stand-alone, single processing node system. Moreover, new hardware components best specialised for parts of the processed traffic (FPGAs) become available. The thesis of this dissertation is that processing traffic at future link rates is facilitated by parallel processing tasks either on single node, or for even higher rates, using multiple nodes in a heterogeneous distributed architecture.

Using distributed system addresses, at a minimum, two current demands. The first demand is *scalability*. More work needs to be done in the same time by only one node (e.g., traffic processing at multi-gigabit rates needed at the network edges in large community areas). The second demand is the use of *heterogeneous* systems shown by the possibility to use specialised systems for various and different traffic functions (e.g., IDS, generic traffic monitoring, video streams processing), or to use different hardware generations for the purpose of traffic processing.

One can say that using a parallel machine (e.g., many Pentium cores on the same die) can give the same processing power as a distributed system could do, but at a smaller development price (e.g., using better development environments and known trade-offs from the generic symmetric multi-processing research domain). However, getting good performance from parallel machines requires careful attention to data partitioning, data locality, and processor affinity. When using distributed systems, we care less about such low-level application partitions, and we focus on higher level issues like how to map the application on multiple nodes so that it processes the traffic optimally. For instance, in a processing hierarchy, the first nodes may offload the processing tasks of the last (leaf) nodes by pre-processing part of the entire task. For instance, a distributed intrusion detection system can use heterogeneous processing nodes such as old generation network processors for traffic splitting, and several state-of-the-art network processors for deep traffic inspection.

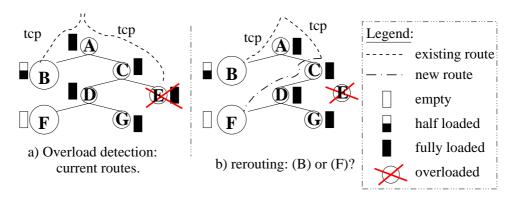

In addition to a distributed traffic system we show that we need systems that are able to manage themselves because the complexity of the systems (and applications) grows in time and the environment becomes more and more hostile at the same time. For example, when the traffic increases beyond the processing capacity of one node from the processing hierarchy then a supervisor may decide to offload the affected node by moving the task onto another node (having more resources) or by replicating the troubled task over multiple nodes.

### 1.5 Thesis overview

The thesis is outlined as follows:

Chapter 2 (*Background*) gives a brief presentation of the FFPF software framework used (and extended) for providing proof of concepts during this research. The text in this section is based on the FFPF paper of which the author of this thesis was a co-author. The chapter then describes the state-of-the-art hardware, network processors, that are largely used in networking applications at high-speeds at the present time.

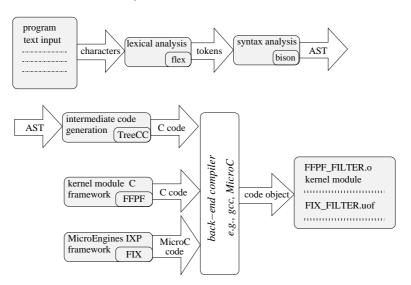

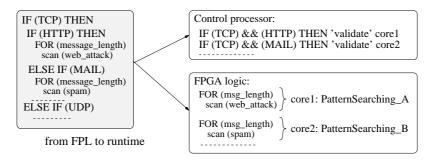

Chapter 3 (FPL: a Resource Constrained Language for Packet Processing) introduces the FPL language and the FPL compiler as a support added to the FFPF software framework. The FPL language is a new packet processing language proposed as a means of obtaining the levels of flexibility, expressive power, and maintainability that such a complex packet processing system requires.

Parts of this chapter have been published in the *Proceedings of the 6th USENIX Symposium on Operating Systems Design* (OSDI'04).

Chapter 4 (*FPL Run-time Environments*) presents the run-time extensions made to the FFPF packet processing framework in order to support the FPL applications onto several hardware architectures in use in these days: commodity PCs, network processors, and FP-GAs. Although the run-time environments make use of tightly coupled parallelism through multi-cores, they are limited to a single-node architecture.

Parts of this chapter have been published in the *Proceedings of the 5th Conference of the Embedded Computer Systems: Architectures, MOdeling, and Simulation* (SAMOS'05) and in the *IEEE Proceedings on IP Operations & Management* (IPOM'04).

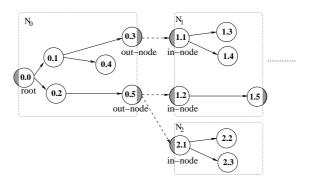

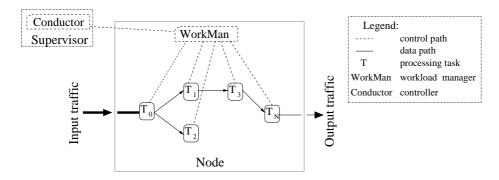

Chapter 5 (Distributed packet processing in multi-node: NET-FFPF) introduces the distributed traffic processing concepts that form some of the key components in the extended multi-node FFPF framework. This chapter presents the distributed network processing environment and the extensions made to the FPL programming language, which enable users to process network traffic at high speeds by distributing tasks over a network of commodity and/or special purpose devices such as PCs and network processors. A task is distributed by constructing a processing tree that executes simple tasks such as splitting traffic near the root of the tree while executing more demanding tasks at the lesser-travelled leaves. Explicit language support in FPL enables us to efficiently map a program to such a tree.

Parts of this chapter have been published in the *Proceedings of the 4th International Conferences on Networking* (Networking'05).

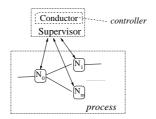

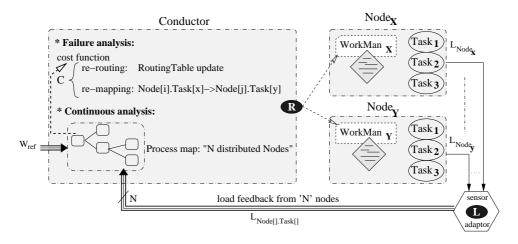

Chapter 6 (*Control for Distributed Traffic Processing: ConDucTor*) introduces a control architecture for distributed traffic processing systems. The control architecture proposes a control loop that monitors and adjusts each processing node of the entire distributed system. In order to achieve the stability goal, the controller re-maps the application tasks from a congested node to another and re-distributes the traffic across the distributed processing hierarchy accordingly.

Chapter 7 (A Simple Implementation of Conductor Based on Centralised Control) presents an implementation of the centralised control approach applied to our distributed traffic processing system.

Chapter 8 (*Case study: Token Based Switch*) presents a case study in which the FPL compiler and the extended run-time version of the FFPF framework described in Chapter 3 are applied to build a specific application: traffic authentication at multi-gigabit speeds using hardware encryption support.

Parts of this chapter have been published in the *Proceedings of the 6th International Conferences on Networking* (Networking'07).

Chapter 9 (*Conclusions*) closes the thesis with a summary and discussion of the presented research topics, and concludes with some suggestions for future research.

### Background

In this chapter, we introduce the software framework – Fairly Fast Packet Filter (FFPF) – and the hardware – IXP network processors – used as a background support for the development of the tools needed to prove the concepts of parallel and distributed traffic processing.

### 2.1 The FFPF framework

Most network monitoring tools in use today were designed for low-speed networks under the assumption that computing speed compares favourably to network speed. In such environments, the costs of copying packets to user space prior to processing them are acceptable. In today's networks, this assumption is no longer true. The number of cycles available to process a packet before the next one arrives (the cycle budget) is minimal. The situation is even worse if multiple monitoring applications are active simultaneously, which is increasingly common as monitors are used for traffic engineering, intrusion detection, steering schedulers in GRID computing, etc.

In this section, we discuss the implementation of the fairly fast packet filter (FFPF) framework. FFPF introduces a novel packet processing architecture that provides a solution for filtering and classification at high speeds. FFPF has three ambitious goals: speed (high rates), scalability (in number of applications) and flexibility. Speed and scalability are achieved by performing complex processing either in the kernel or on a network processor, and by minimising copying and context switches. Flexibility is considered equally important, and for this reason, FFPF is explicitly extensible with native code and allows complex behaviour to be constructed from simple components in various ways.

On the one hand, FFPF is designed as an alternative to kernel packet filters such as CSPF [43], BPF [18], mmdump [44], and xPF [45]. All of these approaches rely on copying many packets to userspace for complex processing (such as scanning the packets for intrusion attempts). In contrast, FFPF permits processing at lower levels and may require as few as zero copies (depending on the configuration) while minimising context switches. On the other hand, the FFPF framework allows one to add support for any of the above approaches.

FFPF is not meant to compete with monitoring suites like Coralreef that operate at a

16 Background

higher level and provide libraries, applications and drivers to analyse data [13]. Also, unlike MPF [19], Pathfinder [20], DPF [21] and BPF+ [22], the FFPF goal is not to optimise filter expressions. Indeed, the FFPF framework itself is language *neutral* and currently supports five different filter languages. One of these languages is BPF, and an implementation of libpcap [28] exists, which ensures not only that FFPF is backward compatible with many popular tools (e.g., tcpdump, ntop, snort [11,46]), but also that these tools get a significant performance boost (see the FFPF evaluation on Section 4.4). Better still, FFPF allows users to mix and match packet functions written in different languages.

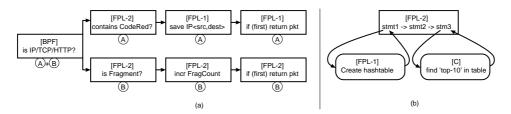

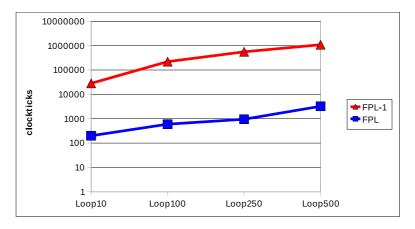

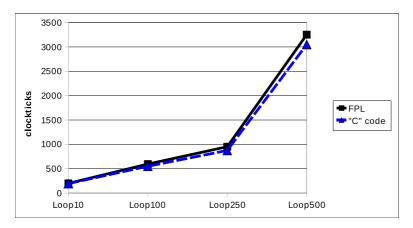

To take full advantage of all features offered by FFPF, we implemented two languages from scratch: FPL-1 (FFPF Packet Language 1) and its successor, FPL. The main difference between the two is that FPL-1 runs in an interpreter, while FPL code is compiled to fully optimised native code. The FPL-1 language is briefly illustrated in Section 2.1.2 and the FPL language is described in Section 3.1 as a part of the thesis work.

The aim of FFPF is to provide a complete, fast, and safe packet handling architecture that caters to all monitoring applications in existence today and provides extensibility for future applications.

Some contributions of the FFPF framework are summarised below.

- We generalise the concept of a 'flow' to a stream of packets that matches arbitrary user criteria;

- Context switching and packet copying are reduced (up to 'zero copy').

- We introduce the concept of a 'flow group', a group of applications that *share* a common packet buffer;

- Complex processing is possible in the kernel or NIC (reducing the number of packets that must be sent up to userspace), while Unix-style filter 'pipes' allow for building complex flow graphs;

- Persistent storage for flow-specific state (e.g., counters) is added, allowing filters to generate statistics, handle flows with dynamic ports, etc.

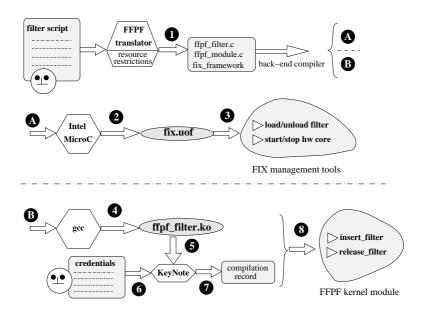

### 2.1.1 The FFPF architecture

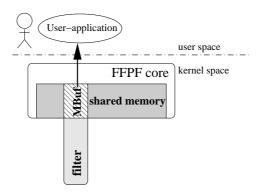

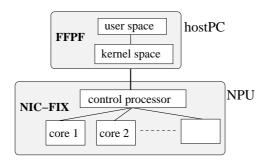

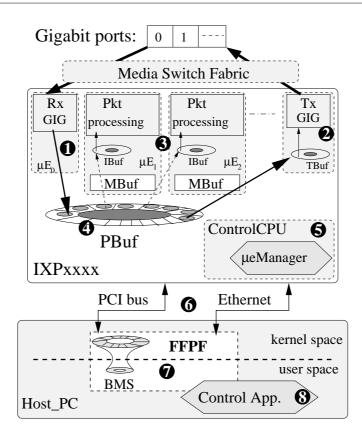

The FFPF framework can be used in userspace, the kernel, an IXP2xxx network processor, a custom FPGA hardware, or a combination of the above. As network processors and FPGAs are not yet widely used, and (pure) userspace FFPF does not offer many speed advantages, the kernel version is currently the most popular. For this reason, we use FFPF-kernel to explain the architecture here, and describe the network processor and FPGAs versions later in Sections 4.2 and 4.3, respectively.

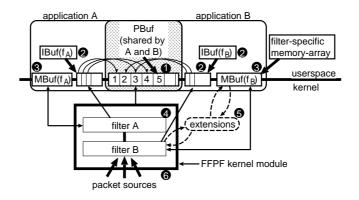

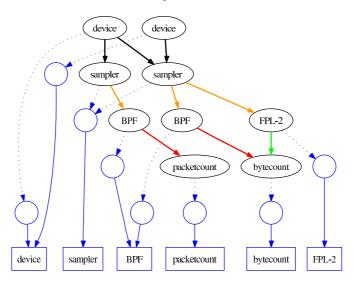

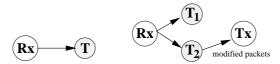

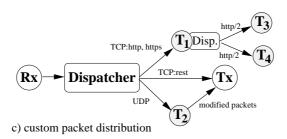

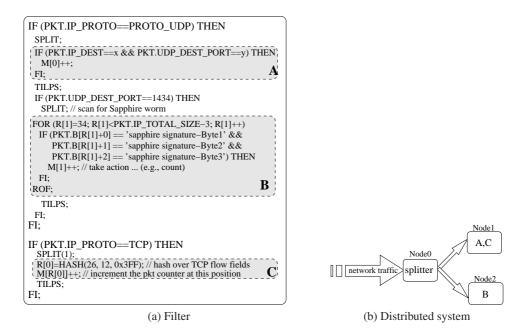

To introduce the architecture and the terminology, Figure 2.1 shows an example scenario in which two applications (A and B) monitor the network. We assume, for illustration purposes, that they are interested in overlapping 'flows', with the definition of 'flow' as follows. A flow is a kind of generalised socket which is created and closed by an application in order to receive/send a stream of packets, where the packets match a set of arbitrary criteria. Examples include: 'all packets in a TCP connection', 'all UDP packets', 'all UDP packets

containing a worm signature plus all TCP SYN packets', etc. A flow is captured by a set of interconnected filters, where a filter is defined as a processing engine that at the very least takes a stream of packets as input and generates a new (possibly empty) stream of packets as output (in addition, it may produce statistics and perform sophisticated tasks). Connected filters form 'processing graphs' through which packets flow.

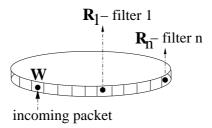

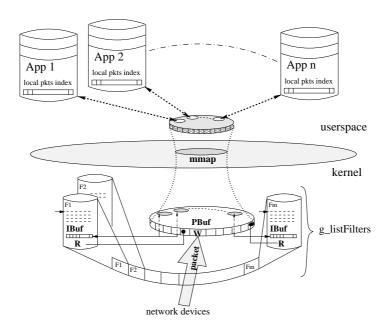

Figure 2.1: The FFPF architecture

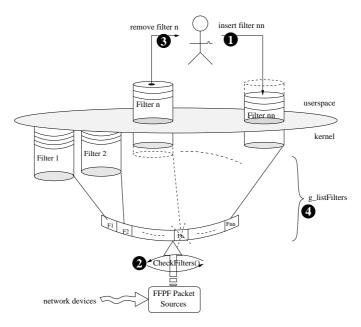

The idea behind FFPF is simple (see Figure 2.1). In the kernel users load sets of connected filters that process packets 4. Strictly speaking, a *filter* is an instantiation of a *filter class*, and may perform more complex tasks than just filtering (e.g., it may generate statistics). The precise nature of the filters will be discussed in detail in Section 2.1.1. If a packet is classified by filter A as 'interesting', and it is not yet in a shared circular buffer (PBuf), it is pushed in PBuf, while a pointer to the packet is placed in filter A's index buffer ( $IBuf_A$ ). If B is also interested in the packet, the packet is not copied, but rather another pointer to the packet is placed in B's index buffer ( $IBuf_B$ ). Applications use the index buffers of filters to find the packets in which they are interested in PBuf. Clearly, proper management of the buffers is needed, but we skip the details in this section and return to this issue in Section 4.1.1. The third buffer, MBuf, is used for exchanging information between the application and the filter code in kernel space or to store persistent state. For instance, the expression may use it to store statistics.

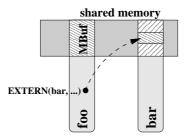

All buffers are memory mapped, so in addition to avoiding copies to multiple applications, we also avoid copies between kernel and userspace. Depending on the language that is used for the filters, a filter expression may call extensions in the form of 'external functions' loaded either by the system administrator or the users themselves ⑤. External functions contain highly optimised native implementations of operations that are too expensive to execute in a 'safe' language (e.g., pattern matching, generating MD5 message digest).